前言

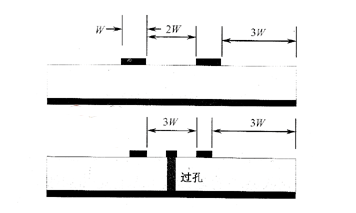

在封装的SI/PI设计中,走线的RLGC参数是常用的评估指标。芯和Hermes X3D是基于矩量法的准静态电磁场仿真求解器,在低频求解具有较高的精度。Hermes X3D支持常用的封装/PCB版图设计格式,简化的流程也易于用户上手。

Hermes的X3D仿真流程

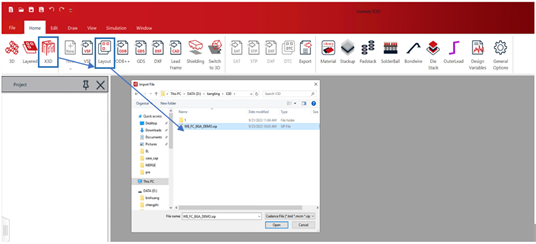

1.导入MCM设计文件

运行Hermes后,在左上角菜单栏中选择Home的X3D流程,再选择Layout流程。在弹出窗口中,选择导入所需的mcm文件。

图 1

导入mcm文件

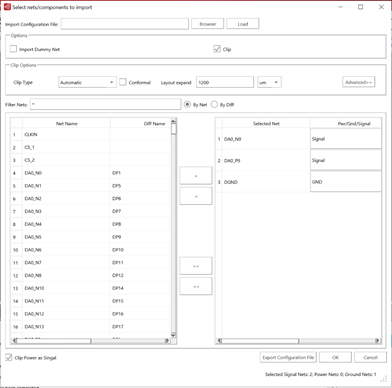

选择要仿真的网络,DA0_P9,DA0_N9,GND,同时,勾选clip,软件会根据所选择网络自动做版图切割,版图外扩尺寸可设置。

图 2

导入窗口

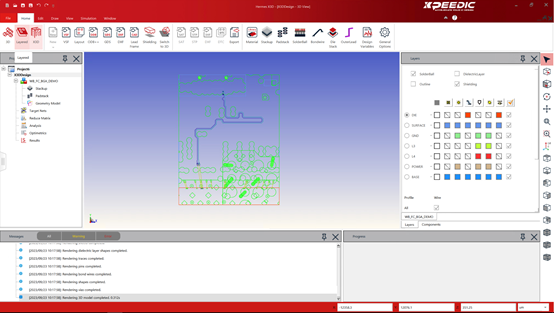

导入后的界面如下图所示:

图3

导入的版图

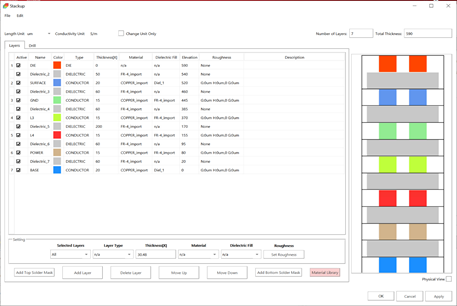

2.叠层属性配置

模型导入到Hermes工作区后,双击Stackup,即可进行叠层及材料属性等配置。

图4

叠层设置

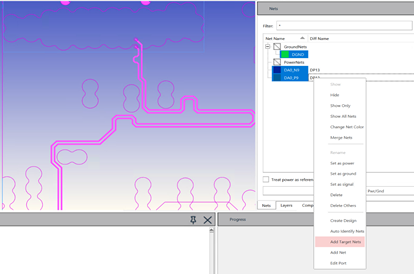

3.选择target net

在右侧NET栏中,将要仿真的net,设置为target net。GND的处理有2种方式,一种是先设成ground 类别,然后抽参数,另外一种是不设,当成signal直接抽参数,然后利用reducematrix指定ground即可。

图 5

选择target net

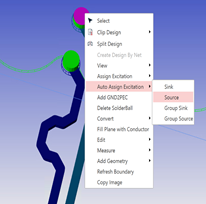

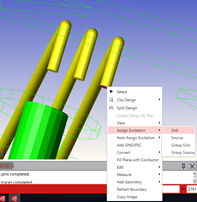

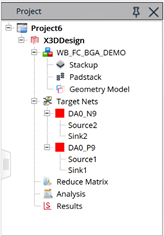

4.添加source,sink

点击select by face,选中相应的面来添加source,sink,如图6。设置好后,source, sink会在左侧工程栏中显示,如图7所示。需要注意的是,设置sink/source需要与实际电流流向吻合,提高精度。

图6

添加source, sink

图7

工程树中显示source, sink的添加结果

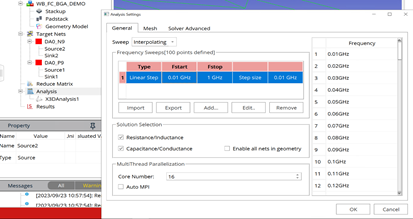

5.仿真配置

添加一个X3D Analysis流程,设置仿真分析条件,仿真频率设置为0.01GHz-1GHz,默认勾选Resistance/Inductance, Capacitance/Conductance。

图8

仿真配置

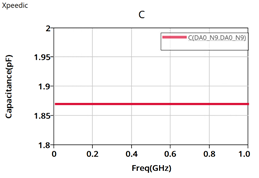

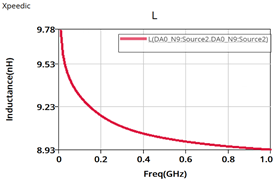

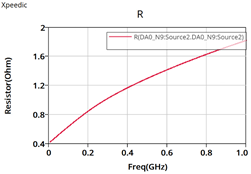

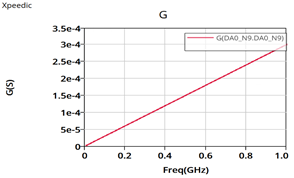

6.仿真结果查看

仿真求解完毕后,可以查看RLGC的结果和S参数结果,并且可以根据需要导出需要的结果文件。

图9

RLGC结果

总结

本文介绍了如何使用Hermes平台的X3D实现对封装走线的RLGC提取。提取流程包括导入版图,检查层叠,选择target net,添加source/sink,仿真配置这五个步骤,该流程可以实现任意走线的RLGC提取,流程简单,界面友好,容易上手。

审核编辑:刘清

-

仿真器

+关注

关注

14文章

1048浏览量

86756 -

Layout

+关注

关注

15文章

418浏览量

73128 -

RLGC

+关注

关注

0文章

2浏览量

8116 -

PCB封装

+关注

关注

21文章

89浏览量

31339 -

GND

+关注

关注

2文章

548浏览量

41132

原文标题:【应用案例】如何实现“封装走线RLGC提取”

文章出处:【微信号:Xpeedic,微信公众号:Xpeedic】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

3条以上的分支怎么处理PCB走线

Cadence 凭借突破性的 Integrity 3D-IC 平台加速系统创新

【技术】BGA封装焊盘的走线设计

芯片那么小,封装基板走线损耗能大到哪去?

基于STL转换为X3D格式的研究

利用X3D语言对电气定位实验进行虚拟仿真

如何使用Hermes平台的X3D实现对封装走线的RLGC提取呢?

如何使用Hermes平台的X3D实现对封装走线的RLGC提取呢?

评论