平台级中断控制器(PLIC)

PLIC:Platform-Level Interrupt Controller.

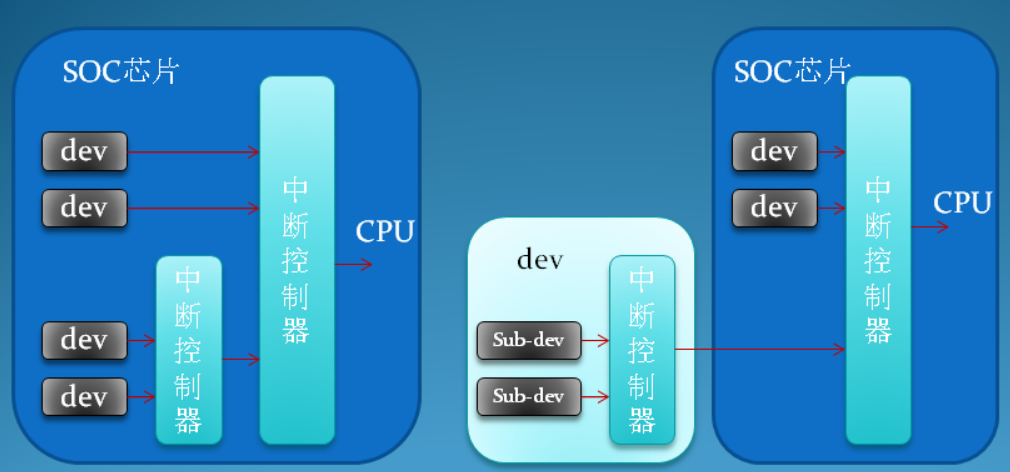

实际上,除了CLINT管理的软件中断和定时器中断,其他的中断都是由PLIC管理的。

U54内核的平台级中断控制器 (PLIC) 最多可支持 132 个具有 7 个优先级的外部中断源。

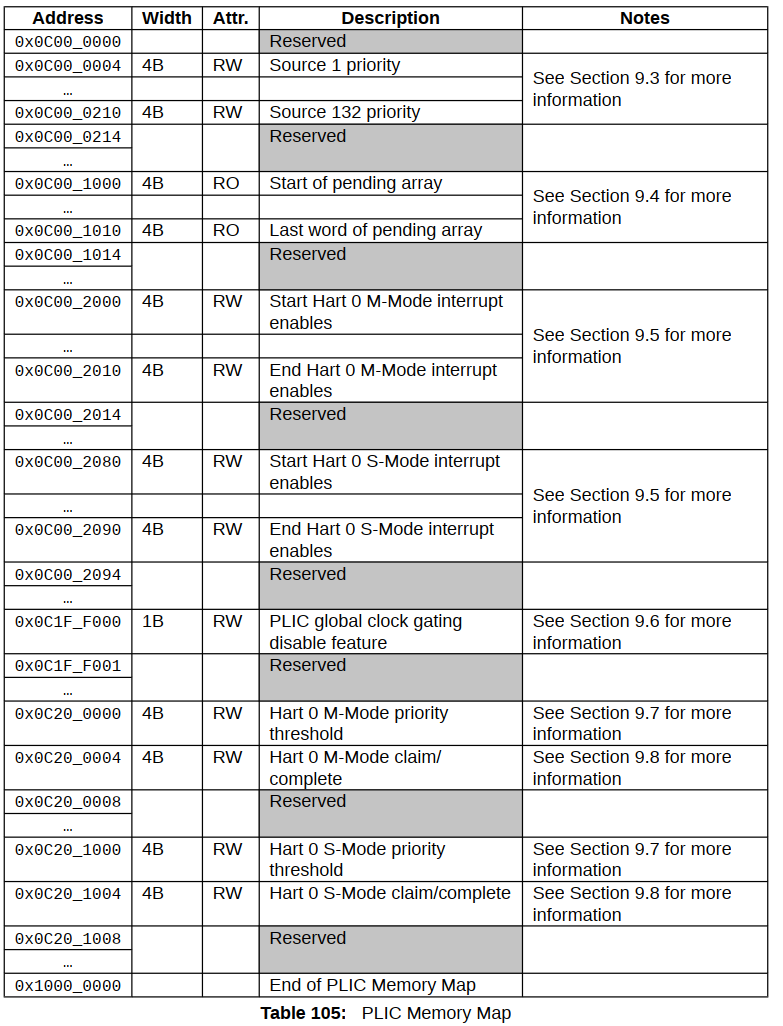

Memory Map

U54 内核 PLIC 控制寄存器的内存映射如表 105 所示。PLIC 内存映射仅支持对齐的 32 位内存访问。

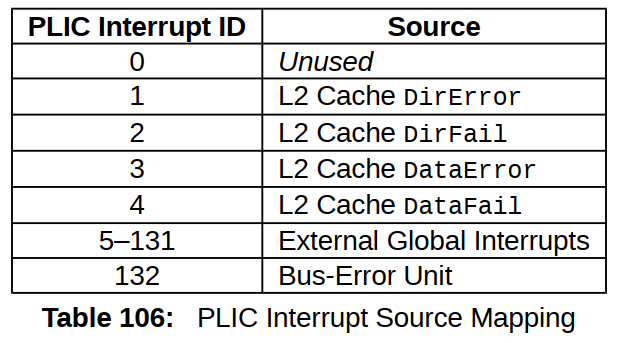

中断源

U54内核共有 132 个全局中断源,此外还有CLINT管理的 中描述的本地中断。

其中 127 个是外部全局中断,其余由表 106 中列出的各种片上设备驱动。表 106 描述了 U54 核心复合体上的全局中断源。

Note:在 RISC‑V 平台级中断控制器规范中,中断源 0 (ID 0) 未使用,因此第一个可用的 PLIC 中断 ID 的值为 1

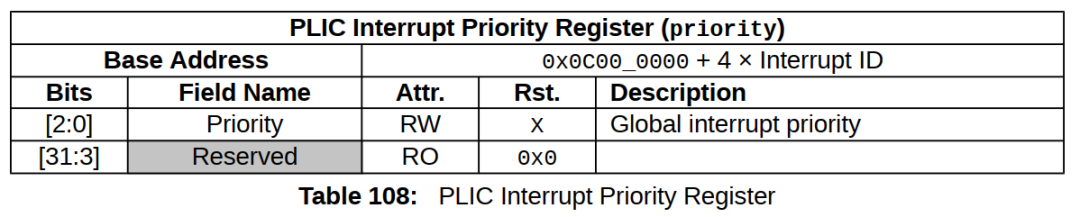

中断优先级

每个 PLIC 中断源都可以通过写入其 32 位内存映射优先级寄存器来分配优先级。

U54 内核支持 7 个优先级。保留优先级值 0 表示“永不中断”并有效地禁用中断。

优先级 1 是最低的活动优先级,优先级 7 是最高的。

相同优先级的全局中断之间的关系由中断 ID 打破;ID 最低的中断具有最高的有效优先级。相关寄存器信息如下:

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

内核

+关注

关注

4文章

1476浏览量

43102 -

RISC

+关注

关注

6文章

485浏览量

86878 -

sifive

+关注

关注

0文章

37浏览量

9825

发布评论请先 登录

相关推荐

热点推荐

易灵思Sapphire SoC中RISC-V平台级中断控制器深度解析

随着 RISC -V处理器在 FPGA 领域的广泛应用,易灵思 FPGA 的 Sapphire RISC-V 内核凭借软硬核的灵活支持,为开发者提供多样选择。本文深入探讨 Sapphire SoC 中 RISC - V 平台级

psoc1中断控制器

本章介绍了中断控制器及其相关的寄存器。中断控制器为PSoC可编程片上系统设备的硬件资源提供了一种机制,改变程序执行到一个新的地址,而不考虑到目前正在执行的任务被执行的代码。

发表于 11-22 15:30

NVIC嵌套向量中断控制器介绍

一、NVIC 介绍NVIC 英文全称是 Nested Vectored Interrupt Controller,中文意思就是嵌套向量中断控制器,它属于 M3 内核的一个外设,控制着芯片的中断

发表于 12-07 07:51

简要介绍配置嵌套向量中断控制器

配置嵌套向量中断控制器static void NVIC_Configuration(void)//OK{NVIC_InitTypeDef NVIC_InitStructure; /* 嵌套向量

发表于 02-22 08:14

华芯微特MCU的嵌套向量中断控制器与外部中断/事件控制器的使用方法

“嵌套向量中断控制器(NVIC)”用以管理中断事件。其中M0和M4提供的中断优先级及个数不一致,为了让您更加简单的使用这一功能,下面小编将以SWM190为例,给大家展示如何使用SWM系

中断控制器的驱动解析(上)

这里主要分析 linux kernel 中 GIC v3 中断控制器的代码(drivers/irqchip/irq-gic-v3.c)。设备树先来看下一个中断控制器的设备树信息:gic:...

发表于 12-04 16:36

•10次下载

扒开 ARM 中断控制器的底裤

GIC 硬件原理GIC,Generic Interrupt Controller。是ARM公司提供的一个通用的中断控制器。主要作用为:接受硬件中断信号,并经过一定处理后,分发给对应的CPU...

发表于 12-04 17:36

•6次下载

细说STM32的中断控制器(NVIC)那些事

1、什么是NVIC?来自《CM3技术参考手册》的官方资料回答:即嵌套向量中断控制器(Nested Vectored Interrupt Controller)。说白了NVIC的功能就是中断优先级

发表于 01-14 15:54

•6次下载

AS32X601驱动系列教程 PLIC_中断应用详解

平台中断控制器(Platform Level Interrupt Controller,PLIC)是国科安芯AS32系列MCU芯片的中断控制器,主要对中断源进行采样,优先

RISC-V怎么实现核间中断?核心本地中断控制器(CLINT)深度解析

于每个核心 / 硬件线程(hart)的中断控制器,专门处理「核心本地、非共享」的中断类型,区别于处理外设共享中断的 PLIC(Platform-Level Interrupt Cont

PLIC平台级中断控制器介绍

PLIC平台级中断控制器介绍

评论