作者:Adam Taylor

编者按:全新的 FPGA 架构方法带来了更精细的控制和更大的灵活性,以满足机器学习 (ML) 和人工智能 (AI) 的需求。本系列文章包括两部分,第 1部分介绍了 Efinix 的一款此类架构,以及如何借助开发板快速入门。第 2 部分讨论了开发板与外部器件和外设(如摄像头)的连接。

从工业控制和安全到机器人、航空航天和汽车,FPGA 在许多应用中扮演着重要角色。凭借可编程逻辑内核的灵活性及其广泛的接口能力,FPGA 在需要部署 ML推理的影像处理中的应用日渐广泛。FPGA 非常适合用来实现具有多个高速摄像头接口的解决方案。此外,FPGA 还能在逻辑中实现专门的处理管道,从而消除基于 CPU或 GPU 的解决方案的相关瓶颈。

然而,对于许多开发人员来说,他们的应用需要更多 ML/AI 功能及更精细的控制或路由和逻辑,而这些是采用组合逻辑块 (CLB) 的经典 FPGA架构所不能提供的。全新的 FPGA 架构方法解决了这些问题。例如,Efinix 的 Quantum 架构采用可交换逻辑和路由 (XLR) 块。

本文讨论了 Efinix FPGA 架构的主要特点和属性,重点介绍其 AI/ML能力并探讨了其在真实世界的实现。随后,本文讨论了一款开发板及相关工具,开发人员可以借助它们快速开始后续 AI/ML 成像设计。

Efinix FPGA 器件

Efinix 目前提供两个系列的器件。最初推出的是 Trion 系列,逻辑密度为 4000 (4K) 至 120K 逻辑元件 (LE),采用 SMIC40LL 工艺制造。最新系列的器件则是 Titanium 系列,逻辑密度为 35K 至 100 万 (1M) 逻辑元件,采用非常流行的 TSMC 16 nm节点制造。

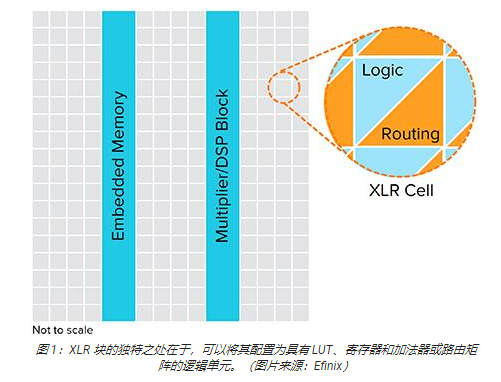

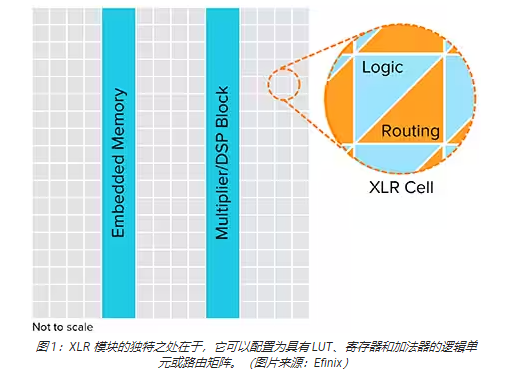

这两个系列均基于 Quantum 架构,这在 FPGA 领域是独一无二的。标准 FPGA 架构基于 CLB,在最基础的层面上,包含一个查找表 (LUT)和触发器。CLB 实现逻辑方程,然后通过路由互连。借助 XLR 块,Efinix 的 Quantum 架构摆脱了单独的逻辑和路由块。

XLR 块的独特之处在于,可以将其配置为具有LUT、寄存器和加法器或路由矩阵的逻辑单元。这种方法带来一个更精细的架构,可提供路由灵活性,使复杂逻辑或路由的实现能够达到预期的性能。

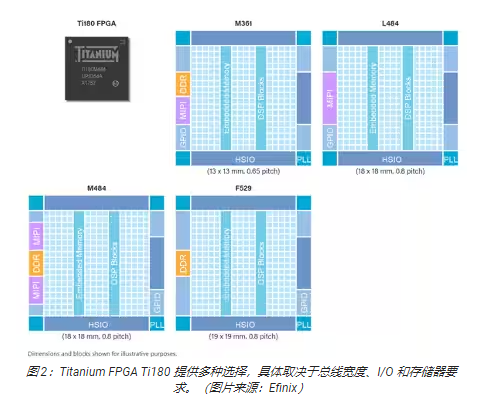

最新的 Titanium 系列器件为开发人员提供了最先进的功能(图 2)。搭载 XLR 内核,该系列器件可提供运行速度为 16 Gbps 或 25.8Gbps(具体取决于所选择的器件)的多千兆位串行链路。这些多千兆位链路对于实现芯片内外的高速数据传输至关重要。

Titanium 器件还提供广泛的输入/输出 (I/O) 接口功能,可归类为通用 I/O (GPIO),并可支持单端 I/O 标准,如 3.3 V、2.5V 和 1.8 V 的低压 CMOS (LVCMOS)。

对于高速和差分接口,Titanium 器件提供高速 I/O (HSIO),支持单端 I/O 标准,如 1.2 V、1.5 V 的 LVCMOS,以及SSTL 和 HSTL。HSIO 支持的差分 I/O 标准包括低压差分信号 (LVDS)、差分 SSTL 和 HSTL。

现代 FPGA 还需要紧密耦合的高带宽存储器来存储用于图像处理应用的图像帧、用于信号处理的采样数据,当然还要为 FPGA内实现的处理器运行操作系统及软件。Titanium 系列器件能够连接动态数据速率四 (DDR4) 和低功耗 DDR4(x)(LPDDR4(x))。根据所选择的具体 Titanium 器件,支持的总线宽度为 x32 (J) 或 x16 (M),而有些器件不支持 LPDDR4(L)。

Titanium FPGA 基于 SRAM,需要配置存储器,通过主/从串行外设互连器件 (SPI) 或 JTAG进行器件配置。为了确保这种配置方法安全,Titanium FPGA 使用 AES GCM 对比特流进行加密,同时使用 AES GCM 和 RSA-4096提供比特流验证。采用这种强大的安全措施非常有必要,原因在于 FPGA 部署在边缘,恶意攻击者可在边缘访问并操纵其行为。

开发板介绍

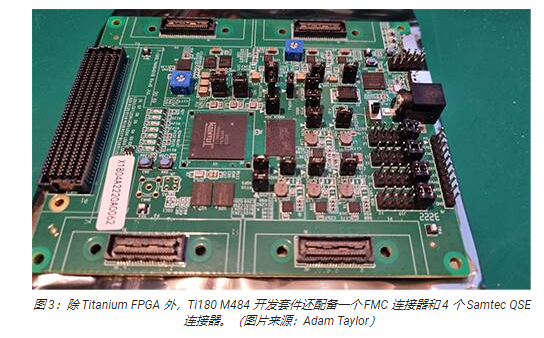

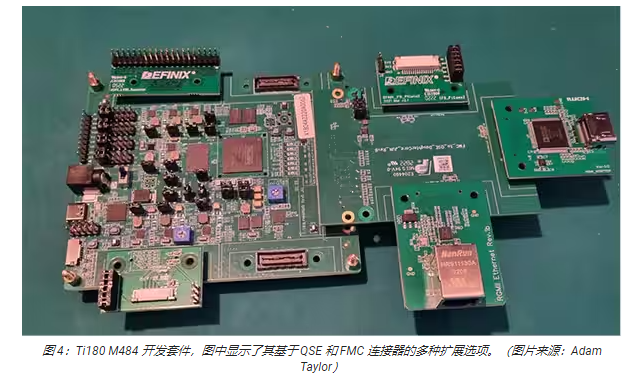

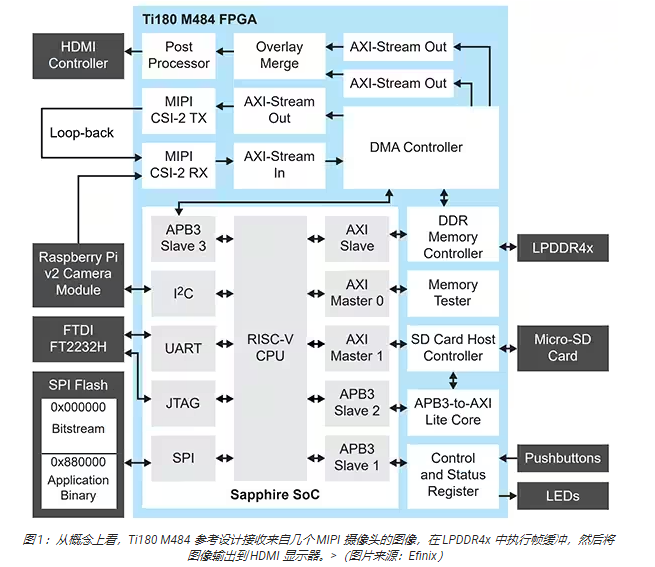

开发板是 FPGA 评估流程的关键要素,因为它们可以用来探索器件的功能和原型应用,从而帮助降低整体风险。首款可用于评估 Titanium FPGA和开始原型设计应用的开发板是 Ti180 M484(图 3)。此开发板具有一个 FPGA 夹层卡 (FMC) 连接器和 4 个Samtec QSE连接器。

安装在此开发板上的 Ti180 FPGA 提供 172K XLR 单元、32 个全局时钟、640 个数字信号处理 (DSP) 元件和 13 Mb 的嵌入式RAM。DSP 元件能够实现固定点 18 x 19 乘法和 48 位乘法运算。此 DSP 还可针对以双路或四路配置运行的单指令多数据 (SIMD)运算进行优化。DSP 元件也可以配置为执行浮点运算。

像大多数开发板一样,Ti180 开发板提供了简单的 LED 和按钮。但是,其真正的强大之处在于连接能力。Ti180 开发板提供一个小引脚数的 FMC连接器,可以连接各种外设。由于这是一种广泛使用的标准,因此有许多 FMC 卡可以实现高速模数转换器 (ADC)、数模转换器(DAC)、网络和内存/存储解决方案的连接。

除 FMC 连接外,此开发板还配备 4 个 Samtec QSE 连接器,供开发人员添加扩展卡。这些 QSE 连接器用于提供 MIPI输入和输出,其中每个 QSE 连接器提供一个 MIPI 输入或输出。

Ti180 开发板还提供 256 Mb 的LPDDR4,以支持影像或信号处理应用所需的高性能存储器。此外,该开发板提供了一系列时钟选项(25、33.33、50 和 74.25 MHz),可搭配器件锁相环(PLL) 使用以产生不同的内部频率。

在开发过程中,能够在开发板上实时重新编程和调试至关重要,而这需要 JTAG 连接,此板通过 USB-C 接口提供了此连接。另外,还提供了两个 256 MbNOR 闪存器件形式的非易失性存储器,可用于演示配置解决方案。

此开发板由包装盒内随附的 12 V 通用电源适配器供电。附件还包括一个 FMC 到 QSE 分线板,以及基于 QSE 的 HDMI、以太网、MIPI 和LVDS 扩展卡。为了演示 Ti180 的影像处理能力,还提供一个双 RPI 子卡和两个 IMX477 摄像头卡。

软件环境

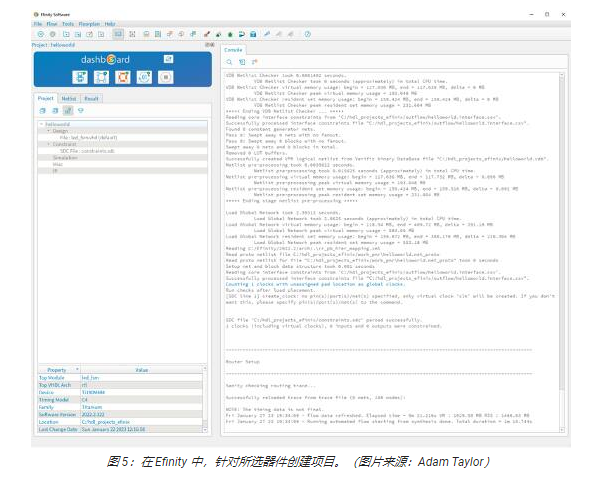

实现针对 Ti180 开发板的设计时要使用 Efinix 软件 Efinity。该软件能够通过合成及布局布线生成比特流。此外,它还为开发人员提供了知识产权(IP) 块、时序分析和片上调试功能。

请注意,需要有开发板才能使用 Efinity 软件。但与其他供应商不同的是,该工具没有其他需要额外许可的版本。

在 Efinity 中,针对所选的器件创建项目。然后,可以将 RTL 文件添加到项目中,并为定时和 I/O 设计创建约束条件。利用 HSIO、GPIO和专用 I/O,开发人员还可在 Efinity 中实现 I/O 设计。

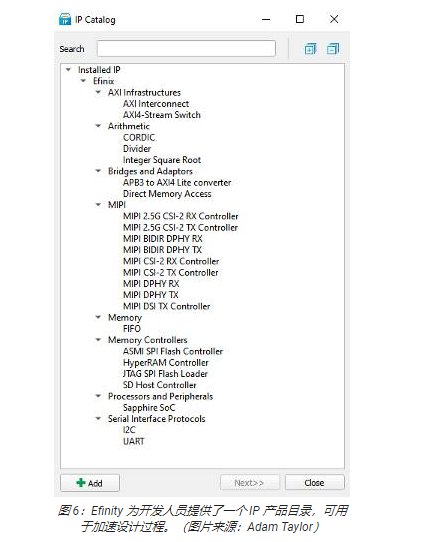

FPGA 设计的一个关键因素是利用 IP,特别是复杂的 IP,如 AXI 互连、存储器控制器和软核处理器。Efinity 为开发人员提供了一系列 IP块,可用于加速设计过程。

虽然 FPGA 在实现并行处理结构方面表现优异,但许多 FPGA 设计包含软核处理器。这些处理器能够实现顺序处理,如网络通信。为了能够在 Efinix器件中部署软核处理器,Efinity 提供了 Sapphire 片上系统 (SoC) 配置工具。Sapphire允许开发人员定义一个多处理器系统,该系统具有跨多个处理器的缓存和缓存一致性,同时能够运行嵌入式 Linux 操作系统。在 Sapphire 中,开发人员可以选择1 至 4 个软核处理器。

所实现的软核处理器是 VexRiscV 软 CPU,基于 RISC-V 指令集架构。VexRiscV 处理器是一款 32

位实现,具有流水线扩展,并提供可配置的特性集,使其非常适合用作 Efinix 器件中的软核处理器。可选配置包括乘法器、原子指令、浮点扩展和压缩指令。根据 SoC系统的配置,性能范围为 0.86 至 1.05 DMIPS/MHz。

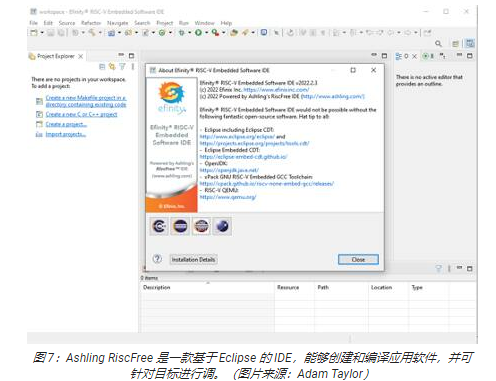

在 Efinix 器件中设计并实现硬件环境后,即可使用 Ashling RiscFree IDE 来开发应用软件。Ashling RiscFree是一款基于 Eclipse 的 IDE,能够创建和编译应用软件,并可针对目标进行调试,以在部署前对应用程序进行微调。

如果要开发嵌入式 Linux 解决方案,将提供所有必要的启动工具,包括第一级引导程序、OpenSBI、U-Boot 和使用 Buildroot 的Linux。另外,如果需要实时解决方案,开发人员可以使用 FreeRTOS。

AI 实现

Efinix 的 AI 实现以 RISC-V 软核运算为基础。其中利用 RISC-V 处理器的自定义指令功能,来实现 TensorFlow Lite解决方案的加速。借助 RISC-V 处理器,用户还能够创建自定义指令,这些指令可用作 AI

推理后的预处理或后处理的一部分,从而创建出响应速度更快、更具确定性的解决方案。

要开始 AI 实现,第一步是探索 Efinix 模型库,这是一个已针对其终端技术优化的 AI/ML 模型库。对于使用 Efinix器件的开发人员,可以访问该模型库,并使用 Jupyter Notebooks 或 Google Colab 来训练网络。训练网络后,便可使用TensorFlow Lite 转换器将其从浮点模型转换为量化模型。

转入 TensorFlow Lite 格式后,可以利用 Efinix 的 tinyML 加速器在 RISC-V解决方案上创建可部署的解决方案。tinyML 生成器使开发人员能够定制加速器的实现并生成项目文件。当以这种方式部署时,加速可达 4 至 200倍,具体取决于所选的架构和定制方案。

总结

凭借独特的 XLR 结构,Efinix 器件可为开发人员提供灵活性。该工具链不仅能实现 RTL 设计,还能实现部署软核 RISC-V 处理器的复杂 SoC解决方案。AI/ML 解决方案建立在软核 SoC 之上,可以实现 ML 推理的部署。

-

FPGA

+关注

关注

1602文章

21324浏览量

593215 -

AI

+关注

关注

87文章

26454浏览量

264068 -

开发板

+关注

关注

25文章

4431浏览量

94017 -

ML

+关注

关注

0文章

139浏览量

34294

发布评论请先 登录

相关推荐

为什么以及如何使用 Efinix FPGA 进行 AI/ML 成像 — 第 1 部分:入门

为什么以及如何将 Efinix FPGA 用于 AI/ML 成像第 2 部分:图像采集和处理

为什么以及如何将 Efinix FPGA 用于 AI/ML 成像 — 第 1 部分:入门指南

为什么以及如何将 Efinix FPGA 用于 AI/ML 成像 — 第 1 部分:入门指南

评论