国产CPU自主化先行者,基于LoongArch 自研指令系统实现芯片性能突破,国产替代成效渐显,GPT+信创加持驱动增长驶入快车道。

中央处理器(CentralProcessingUnit,简称 CPU)本质是负责计算机运算和控制的超大规模集成电路。CPU 承担耦合系统软硬件资源的中枢作用:1)计算机系统中所有软件层的操作,最终都将通过指令系统映射为 CPU 的操作;2)CPU 控制、调配所有硬件资源(如存储器、输入输出单元),由控制单元实现指令读取、指令译码,并通过运算单元执行数据加载、计算和回存任务。

CPU 是信息产业算力底座,生态体系上下游高度协同。CPU 生态体系是硬件和软件的结合,是产业上下游交互的产物。

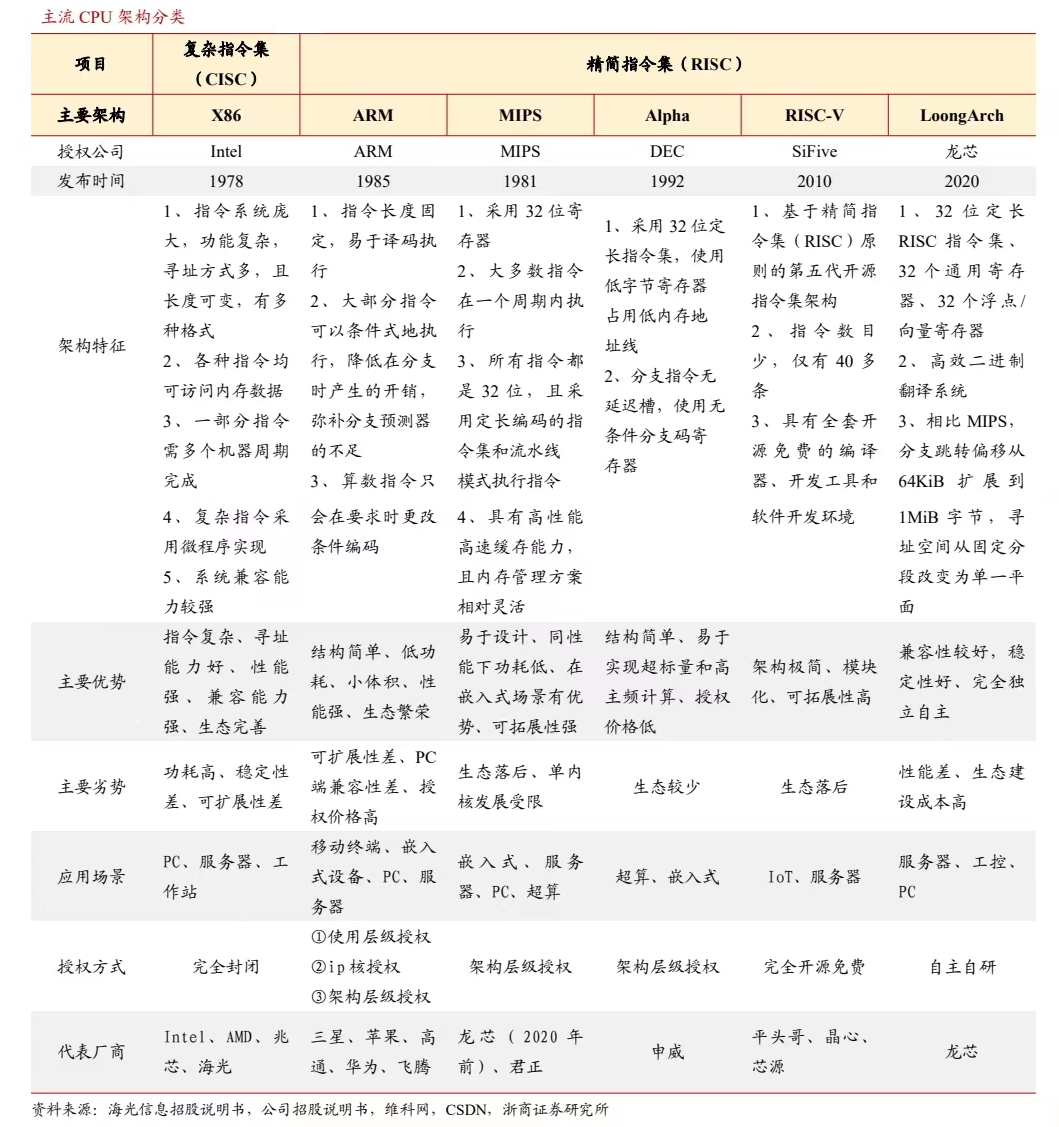

指令系统是生态底层逻辑,可分为复杂指令集和精简指令集。指令系统(ISA)属于计算机中硬件与软件的接口,可实现高级程序语言、汇编语言和机器语言的连接,最终编译为 CPU 可执行的简单指令,按照指令复杂程度可分为复杂指令集(CISC)和精简指令集(RISC)。Intel 在 1978 年推出的 X86 架构是目前唯一的 CISC,其指令复杂、性能卓越、功耗较大,产业生态庞大且完善;以 ARM、MIPS、RISC-V、LoongArch 架构为代表的RISC 对指令集进行了高度优化,具备结构简单、功耗低、体积小、多核并行运算等优势,已全面覆盖移动设备和嵌入式终端等应用场景。

微架构是执行指令集的物理电路设计,决定了芯片性能和自主创新程度。主流 ARM架构授权模式分为三类:1)使用层级授权,仅限 IP 核嵌入终端;2)IP 核授权,以内核为基础延展外设;3)架构层级授权,可对指令集进行扩展或缩减,并形成专向化的各类 IP核。X86 架构相对封闭,目前架构层级授权仅对 Intel 和 AMD 开放,目前国产厂商龙芯和申威分别基于 MIPS 和 Alpha 架构开发出了完全自主创新的 LoongArch 和 SW 架构。

CPU 行业由两大生态体系主导:一是基于 X86 指令系统和 Windows 操作系统的Wintel 体系;二是基于 ARM 指令系统和 Android 操作系统的 AA 体系。PC 时代,以IBM 代表的软硬一体化模式被英特尔和微软所打破,二者在软硬耦合的前提下,遵循“摩尔定律”和“安迪-比尔定律”滚动迭代,即计算芯片和存储器每 18-24 个月实现硬件性能的翻倍,同时 Windows 操作系统凝聚海量开发者,软件不断升级支撑应用创新,最终构成稳固的生态壁垒。移动互联网时代终端设备延续了 PC 发展规律,ARM 凭借其指令系统开源、异构运算、可定制化等一系列优势,成功立足于低功耗的移动市场。

CPU 呈双巨头格局,国产 CPU 市场份额较低。国际市场上主流的 CPU 公司都经历了长期的技术和市场积累,Intel 和 AMD 几乎形成垄断,国内同行业的厂商仍处于成长阶段,与国际主流厂商依旧存在技术差距。据 PASSMARKSOFTWARE 统计,截至 2022Q4,以出货量计算的整个 X86CPU 市场中,Intel 的市场份额为 62.8%,AMD 的市场份额为 35.2%。

新技术和新架构为国产 CPU 发展带来良好契机,自主研发更有潜力。1)处理器性能升级趋势放缓,国产 CPU 来自制程、工艺方面的技术差距将逐步弥合,自研的微架构层级和软件生态上的创新或能成为国产 CPU 性能实现弯道超车的关键变量。2)5G、云计算、人工智能等新一代信息技术加快落地,“万物智联”时代智能设备应用场景更趋于碎片化,对处理器产生专用定制化需求,结构简单的自主化开源指令系统(LoongArch、RISC-V)未来也将成为中小企业开发的重要选项,摆脱 Wintel 和 AA 生态的历史包袱。

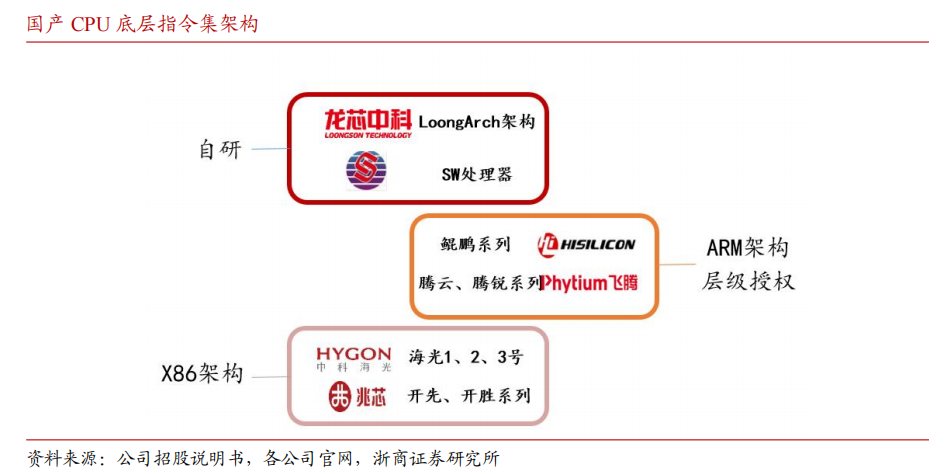

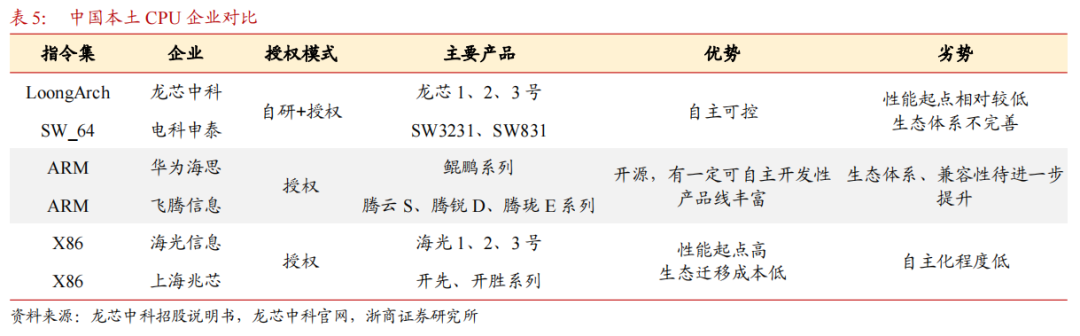

国产 CPU 发展基于两条主流路线:一是自主研发指令系统并构建相应生态体系;二是经已有 X86/AMD 架构授权,加入相应主流体系。国产 CPU 企业目前主要有 6 家,分别是龙芯中科、电科申泰、华为海思、飞腾信息、海光信息、上海兆芯。按采用的指令系统类型可大致分为三类:第一类包括龙芯中科和电科申泰,早期曾分别采用 MIPS 兼容的指令系统和类 Alpha 指令系统,现已分别自主研发指令系统。第二类包括华为海思和飞腾信息,采用 ARM 架构层级授权,自主性较强。第三类包括海光信息和上海兆芯,采用 X86指令系统。目前国产 CPU 企业在指令系统、微架构和基础生态上实现了不同层次的自主创新,其中龙芯中科和电科申泰自主性最高。

国产 CPU 厂商业务集中在党政和重点行业市场。国内 CPU 市场主要分为三类:政务及重点行业市场、企业级市场以及消费级市场。政务及重点行业市场对安全性和定制化的要求最高,对产业生态的要求较低,与国产 CPU 当前的发展现状契合,是近期国产 CPU的核心市场。企业级市场对产业生态的要求高于政务但低于消费级市场,是国产 CPU 未来重要的增量市场。消费级市场对产业生态的要求最高,对性价比较为敏感,迭代周期短,是国产 CPU 长期需突破的目标市场。

推出的自主指令集 LoongArch 迁移或研发操作系统的核心模块,包括内核、三大编译器(GCC、LLVM、GoLang)、三大虚拟机(Java、JavaScript、.NET)、浏览器、媒体播放器、KVM 虚拟机等,形成了自主 CPU 研发和软件生态建设的体系化关键核心技术积累。坚持自主研发核心IP,形成了包括系列化 CPUIP 核、GPUIP 核、内存控制器及 PHY、高速总线控制器及PHY 等上百种 IP 核,取得 400 余项专利,是国内 CPU 企业中极个别可进行指令系统架构及 CPUIP 核授权的企业。通过设计优化和先进工艺提升性能,摆脱对最先进工艺的依赖,通过自主设计 IP 核,克服境内工艺 IP 核不足的短板。目前与公司开展合作的厂商达到数千家,下游开发人员达到数十万人,基于龙芯处理器的自主信息产业生态体系正在逐步形成。

基于 LoongArch 指令系统的 CPU 产品性能有效突破。根据工业和信息化部下属测试机构提供的说明,公司的 3A5000 芯片在国产同类桌面 CPU 中处于性能领先水平。与采用相同工艺节点的同类产品相比,3A5000 在 SPECCPU 整型/浮点单核性能、Unixbench 单线程测试分值等各项性能参数方面占优,与采用领先 3A5000 两个工艺代制程的 ARM 架构桌面产品性能相当。作为一款四核 CPU,3A5000 的 Unixbench 多线程测试分值甚至超过采用X86 和 ARM 架构的相同工艺节点的可比公司八核桌面产品。

-

集成电路

+关注

关注

5446文章

12469浏览量

372690 -

指令系统

+关注

关注

1文章

83浏览量

16114 -

微架构

+关注

关注

0文章

22浏览量

7304

原文标题:龙芯指令集,世界第三极

文章出处:【微信号:AI_Architect,微信公众号:智能计算芯世界】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

龙芯指令集,世界第三极

龙芯指令集,世界第三极

评论