近年来,5G、自动驾驶、超大规模计算,以及工业物联网等领域呈现出强劲的发展势头。推动这些高速发展的产业是AI(人工智能)和ML(机器学习)的大规模应用。这种全新的技术布局不仅加速了更复杂的计算需求、更强的功能性和更快的数据传输速度,同时也为芯片研发人员带来了前所未有的挑战:即下一代芯片必须更快且更智能。

在当前的背景下,由于算力和存储需求正面临爆发式增长,这直接导致推动先进SoC(系统级芯片)设计和验证的压力也呈指数级增加。特别是在集成电路规模越来越庞大的现实情况下,从设计到流片(Tape-out)的全流程中,验证变得尤为重要。这是因为有效的验证不仅确保了电路在设计层面的完善,还保证了其在实际应用中的稳定运行,从而降低了修正和调整的成本和时间。

为了应对这一挑战并缩短验证周期,硬件仿真成为了超大规模集成电路验证的首选工具。它能在最短的时间内完成对电路功能的全面验证,这样就大大减少了整个设计到生产的周期。同时,AI/ML算力的飞速增长不仅促进了EDA(电子设计自动化)工具的快速演进,还与EDA工具结合,催生了一种“双向加速”的良性循环。

去年年底,思尔芯推出了首款国产企业级硬件仿真系统——芯神鼎OmniArk。值得一提的是,芯神鼎已将AI应用于编译流程中,这无疑推动了芯片设计领域的发展。

芯神鼎硬件仿真系统采用了由AI驱动的智能编译引擎,该引擎能够在编译流程中极大地减少编译时间和内存占用,实现增量编译,并能智能匹配P&R(布局与布线)策略,从而显著提高布线的成功率。本文将从多个独立模块的角度,深入探讨芯神鼎硬件仿真系统的智能编译流程。

并行综合:打破传统编译瓶颈

传统综合方法充满了局限性。在集成电路设计领域,传统综合方法主要有两种:Top-down综合和Bottom-up综合。1.Top-down综合

该方法对整个设计进行处理,以实现彻底的优化。尽管优化程度高,但这一方案的综合时间通常非常长,不适用于迅速变化的项目周期。2.Bottom-up综合

此方法首先对底层模型进行独立综合,然后逐步并入上层模块进行综合。虽然这适用于一些包含独立IP的复杂设计,但其在超大规模集成电路(VLSI)应用中表现出速度和灵活性的明显不足。对于超大规模集成电路,这两种传统综合方法通常成为编译过程的瓶颈。除了时间效率低下,其对计算资源,特别是内存的占用也相当巨大。

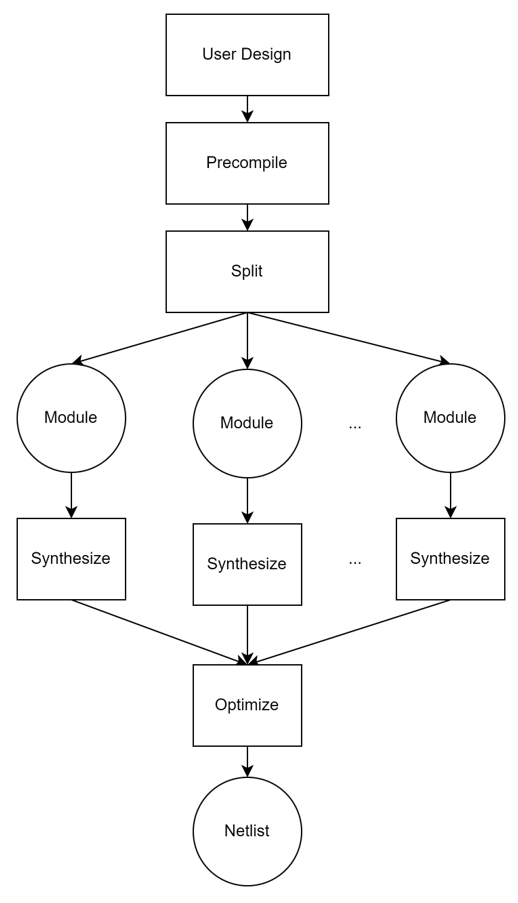

芯神鼎硬件仿真系统对并行综合进行了创新,采用Module-by-Module的综合方式,彻底改变了这一现状。首先,芯神鼎针对整个设计进行必要的全局处理和优化,例如XMR(Cross-Module Reference)处理。接着,以Module为最小粒度,启动多核并行综合过程。这一步是本系统最大的创新之一,它允许系统充分利用服务器/集群的并行计算性能。在所有模块综合完成之后,系统进一步进行跨模块边界(Cross Module Boundary)逻辑优化。此外,芯神鼎能根据服务器配置和实际负载动态调节并行任务数量,以实现负载均衡。

这种并行综合方法大大加速了超大规模集成电路设计的整体综合效率。实际应用中,对于多核NVDLA(NVIDIA Deep Learning Accelerator)这样的复杂设计。经测试,其加速率可以达到惊人的10~100倍,尤其在多核设计中表现出色。

通过创新的并行综合技术,芯神鼎硬件仿真系统成功地突破了传统综合方法在时间和资源效率方面的局限,为超大规模集成电路设计带来了前所未有的效率提升。 图一:并行综合流程

图一:并行综合流程

高效率与高质量的智能P&R

在基于硬件仿真的超大规模设计流程中,P&R(布局与布线)通常是编译的最后一步,负责生成最终的bitstream文件。虽然现有的编译工具提供了多种P&R选项,目的是适应不同设计需求和优化目标,但实际情况却远没有那么简单。由于各种SoC需求和应用场景的多样性,几乎没有一种“通用”的P&R选项组合能适用于所有场景。因此,开发人员需要根据特定的设计需求,手动选择或调整P&R选项,以求达到最佳的设计输出。

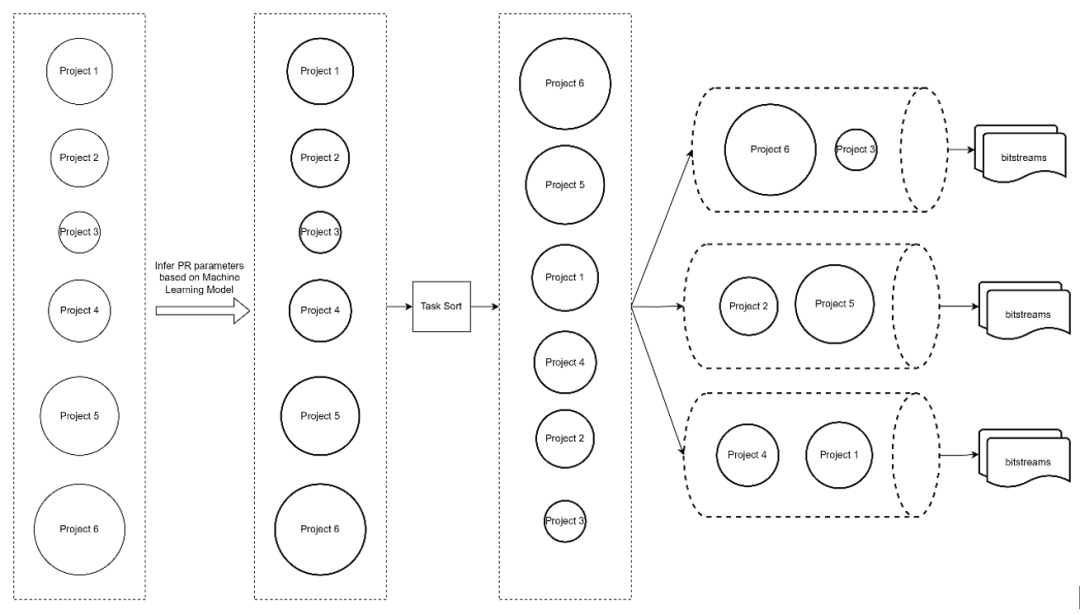

1. 基于机器学习的智能P&R

芯神鼎硬件仿真系统突破了这一局限,采用基于机器学习(ML)的智能P&R方法。通过使用大量的实际P&R数据进行深度训练,系统生成的ML模型能在推理阶段输出最优的P&R参数组合。更值得一提的是,这种基于数据驱动的方法在多个关键性能指标上都超过了人工专家的判断。例如,在布线成功率方面,经测试,可以显著提高布线通过率;同时,P&R所需的总时间也可大幅度减少。

2.优化任务调度和并行计算

除了使用机器学习进行智能选项推荐外,芯神鼎硬件仿真系统还进一步优化了任务调度算法。通过智能任务调度,系统能确保在进行P&R操作时充分利用编译服务器的多核计算能力。具体的并行能力和效率提升取决于编译服务器的性能和配置。

通过集成基于机器学习的智能P&R以及高效的任务调度和并行计算功能,芯神鼎硬件仿真系统为FPGA设计提供了一种更高效、更质量可控的解决方案。这不仅大幅减少了编译时间,同时也显著提升了输出结果的质量。 图二:任务调度和并行计算流程

图二:任务调度和并行计算流程

增量编译

在超大规模集成电路(VLSI)的设计过程中,即使进行了多方面的编译流程优化,编译时间依然可能成为项目进度的瓶颈。更进一步地说,对于那些已经编译过但需做细微修改的工程,每次都进行全量编译会大大延长开发周期,耗费人力和计算资源。

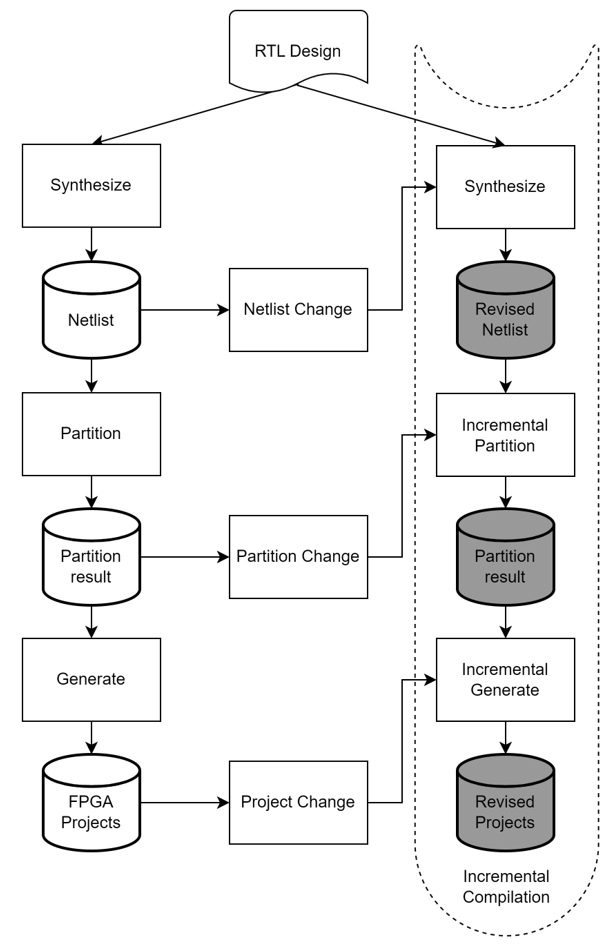

增量编译(Incremental Compilation)是一种编程优化策略,用于加快编译过程。在一个大型或复杂的代码基础上,每次进行全量编译(即重新编译整个代码基础)通常会消耗大量时间和计算资源。增量编译的目标是只重新编译自上次编译后发生变化或被影响的代码部分,而不是整个代码库。

增量编译系统首先会跟踪代码中各模块、函数或文件的依赖关系。当某一部分代码发生改动后,编译系统会识别这一改动,并查找所有依赖于该部分的其他代码。只有被改动的代码和依赖于它的代码会被重新编译。其它未改动和不受影响的代码则不需要重新编译。重新编译的代码会与旧的编译结果合并,生成一个更新的可执行文件或库。对于代码库非常大的项目,增量编译几乎是必需的。

芯神鼎硬件仿真系统便采用了这种增量编译策略。它采用了一种先进的增量编译引擎,该引擎涵盖了综合模块、Partition模块以及工程生成模块等关键部分。这些模块都集成了增量编译技术,可以在二次编译过程中智能感知用户所做的任何修改。这种自动感知机制极大地减少了重新编译所需的计算量,因为它只针对修改过的部分进行编译,而非整个设计。这样不仅大幅度缩短了编译时间,还优化了资源使用效率。 图三:增量编译流程

图三:增量编译流程

总结

AI+EDA的结合代表了一次跨越式的技术进步,它不仅有望延续并拓展摩尔定律的生命周期,还能显著节约研发时间和资本投入,提升行业整体竞争力。进一步地,这一结合还为全球芯片设计领域开创了全新的可能性,比如通过机器学习算法优化设计流程,从而缩短产品上市时间,或者在更短的时间内完成更为复杂的设计任务。

芯神鼎硬件仿真系统集多种创新技术于一身,如并行综合、智能P&R和增量编译等模块,不仅大幅度缩短了编译时间,还提高了整体编译质量。这些模块都运用了我们自主研发的先进技术,为客户在超大规模集成电路验证方面提供了强有力的支持。除了应对现有的编译挑战,我们的解决方案还具备极强的可扩展性,能够适应未来更高复杂度的工程需求。

通过持续的研发和创新,芯神鼎硬件仿真系统有望成为推动整个集成电路设计行业进入新“智”元的重要力量,开启一个全新的、以数据和算法为驱动的芯片设计时代。

-

芯片设计

+关注

关注

15文章

1173浏览量

56784 -

仿真

+关注

关注

55文章

4539浏览量

138692 -

硬件

+关注

关注

13文章

3638浏览量

69174 -

AI

+关注

关注

91文章

41299浏览量

302683

发布评论请先 登录

Cadence与NVIDIA扩大合作以加速新一代工程设计流程

WBS Power推进3.2吉瓦超大规模数据中心园区能源基础设施建设

中科曙光scaleX万卡超集群筑牢超大规模智算硬核底座

中科曙光scaleX万卡超集群重塑超大规模算力基础设施

泰芯半导体携手生态伙伴助力AI硬件产业规模化落地

燧原科技荣获2025年超大规模智算集群创新应用实践成果

思尔芯荣登“国产EDA工具口碑榜”,以“芯神瞳”原型验证解决方案赋能芯片创新

芯华章 HuaEmu E1 四大技术打通超大规模验证核心瓶颈

AI芯片:加速人工智能计算的专用硬件引擎

伟创力高效电源模块在超大规模数据中心的应用

超大规模芯片验证:基于AMD VP1902的S8-100原型验证系统实测性能翻倍

AI驱动的国产硬件仿真芯神鼎如何加速超大规模芯片设计

AI驱动的国产硬件仿真芯神鼎如何加速超大规模芯片设计

评论