pll锁定时间按照频率精度多少来计算

PLL锁定时间是指当PLL尝试将输出频率与输入频率相匹配时所需的时间。这个时间可以用来衡量PLL的性能,因为它决定了PLL能否快速、准确地锁定频率,并且影响PLL的应用领域。PLL锁定时间可以根据PLL的频率精度来计算,下面是一个详细的讨论。

PLL - 综述

PLL是一种电路,它在输入信号和输出信号之间建立了一个相位锁定环,以使输出频率与输入频率之间存在固定的关系。举例来说,如果PLL的输入频率为f_in,而输出频率为f_out,则它们之间的比例为f_out/f_in。PLL的设计目的是在输出信号中保持与输入信号相同的相对相位关系。

PLL通常用于数字通信的网络中,以确保数据传输的准确和可靠性。这是因为它可以平滑地调整周期性信号的相位和频率,以便与同步数据传输协议匹配。

PLL锁定时间 - 定义

PLL锁定时间是指PLL从应用外加的输入信号后,达到稳定输出频率所需的时间。PLL锁定时间是一个关键参数,因为它决定了PLL能够快速、准确地调整输出信号。如果PLL的锁定时间太长,将导致系统延迟和稳定性差,影响PLL的性能。

PLL锁定时间 - 计算

PLL锁定时间可以通过下式计算得出:

t_lock = (2π/Δf_rms) * ln(1/ε)

其中,Δf_rms是指取样时间段内参考时钟的频率抖动标准差(也称为参考时钟的稳定度);ε是指设定的固定值,用于表示PLL输出频率与参考时钟频率之间的偏差。例如,如果设置ε=0.01,则PLL输出频率与参考时钟最多相差1%。Π是圆周率,ln表示自然对数。

这个公式由两个部分组成:一个反映抖动稳定度的部分,一个反映PLL响应的部分。抖动稳定度是参考时钟的波动,它会影响PLL的锁定时间。PLL响应则指PLL反应能力的快慢,它会影响PLL锁定时间。PLL响应越快,锁定时间就越短。

在计算PLL锁定时间时,还要考虑PLL的输出频率范围和精度。例如,如果要实现PLL输出频率在1GHz到2GHz之间,那么Δf_rms的值应该取1GHz到2GHz范围内参考时钟的抖动标准差。

PLL锁定时间 - 影响因素

PLL锁定时间受许多因素的影响,包括抖动稳定性、PLL类型、芯片技术、电路设计等。

在很多情况下,PLL的锁定时间是影响PLL的整体性能的最重要参数之一。PLL的锁定时间从理论上可以通过上面的公式来计算,但实际的参数可能会与理论值略有不同,因为每个PLL都有自己独特的抖动和响应特性。

PLL锁定时间 - 案例研究

对于某些应用来说,PLL的锁定时间是一个关键因素。在具体的设计中,需要考虑PLL锁定时间的大小,以确保系统的稳定性和可靠性。

例如,在字节缓存器中,PLL的性能对数据捕获非常关键。实验表明,如果PLL与参考时钟的差异达到1%或更高,PLL就可能无法在规定的时间内完成锁定。针对这个问题,可以优化PLL的抖动稳定度和响应速度,来确保其能够以最短的时间内完成锁定。

在数字时钟生成电路中,锁定时间也是非常关键的参数。数字时钟生成电路中的PLL通常需要产生多种频率和时钟源,以满足不同的应用需求。在这种情况下,锁定时间对于确保时钟源的同步性和稳定性也非常重要。

PLL锁定时间在很多电路设计中都是必不可少的性能参数之一。为了确保PLL能够快速、准确地调整输出频率,电路设计人员必须仔细评估PLL的抖动稳定度和响应速度,以确定理想的锁定时间和参数。通过优化PLL的性能和参数,设计人员可以确保电路的稳定性和可靠性,来满足不同的应用需求。

-

pll

+关注

关注

6文章

991浏览量

138394 -

缓存器

+关注

关注

0文章

63浏览量

12090 -

时钟源

+关注

关注

0文章

113浏览量

16821

发布评论请先 登录

ADF4196:低相位噪声、快速稳定的6 GHz PLL频率合成器

低相位噪声、快速稳定PLL频率合成器ADF4193的设计与应用

双射频PLL频率合成器ADF4206/ADF4208:高精度与多功能的完美结合

ADF4212L双低功耗PLL频率合成器:特性、应用与设计要点

硬件定时器如何配置固定频率?

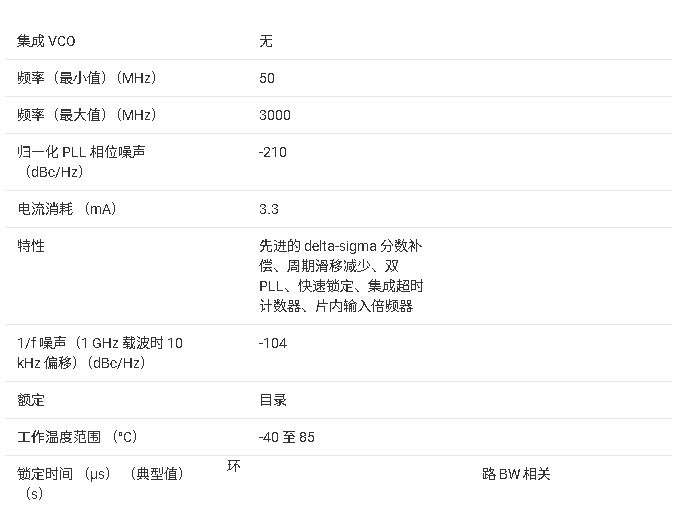

LMX2485E 用于射频个人通信的 50 MHz 至 3 GHz Δ-Σ 低功耗双通道 PLL技术手册

如何测量CAN/CAN FD的位时间精度?

pll锁定时间按照频率精度多少来计算

pll锁定时间按照频率精度多少来计算

评论