pll倍频最大倍数

PLL倍频是一种常见的电路设计技术,通常用于将信号的频率提高到需要的倍数。PLL倍频的实现原理比较复杂,通常需要使用精密的电路元件、时钟信号以及数字信号处理器。本文将详细介绍PLL倍频的实现方法、工作原理以及最大倍数的计算方法,帮助读者更好地了解和应用PLL倍频电路。

一、PLL倍频的实现方法

PLL倍频主要通过三个电路模块来实现:相位比较器、锁相环和除频器。其中,相位比较器主要用于比较输入信号和反馈信号的相位差,从而调整锁相环的频率;锁相环则主要用于根据相位比较器的输出信号来调整时钟信号的频率,保证输入信号和输出信号的同步;除频器则用于将锁相环输出信号的频率按照预定比例进行除频,最终得到需要的输出信号。

二、PLL倍频的工作原理

PLL倍频的工作原理基于锁相环原理,具体步骤如下:

1.将所需倍频的输入信号和时钟信号分别输入给相位比较器和锁相环;

2.相位比较器将输入信号和时钟信号进行相位比较,得出两者之间的相位差;

3.锁相环将相位比较器的输出信号作为反馈信号输入,与输入信号合成新的时钟信号;

4.除频器将锁相环的输出信号按照预定比例进行除频,得到需要的输出信号。

在这个过程中,相位比较器、锁相环和除频器三者相互配合,保证了输入信号到输出信号的同步性和倍频率的准确性。同时,在PLL倍频中,除频器的除数越大,输出信号的频率就越低,但是也会增加系统的时延。

三、PLL倍频的最大倍数

PLL倍频的最大倍数是指在给定的输入信号频率下,可以实现的输出信号最高频率。计算PLL倍频的最大倍数需要考虑多方面的因素,包括锁相环的带宽、稳定性、噪声等。

常用的计算公式如下:

最大倍频率=N×Fclk/(2×M)

其中,N为除频器的除数,M为锁相环的倍频器,Fclk为时钟频率。

从公式上可以看出,除频器的除数N越大,最大倍频率就越低,锁相环的倍频器M越大,最大倍频率就越高。同时,时钟频率Fclk的大小也对最大倍频率有一定的影响。

四、总结

PLL倍频是一种重要的电路设计技术,其主要工作原理是通过相位比较器、锁相环和除频器这三部分电路模块相互配合,实现输入信号到输出信号的同步和倍频。在实际应用中,计算PLL倍频的最大倍数需要考虑多种因素,包括带宽、稳定性、噪声等。希望本文可以为读者提供一些关于PLL倍频的基础知识和理解,帮助读者更好地应用该技术。

-

锁相环

+关注

关注

36文章

633浏览量

90817 -

比较器

+关注

关注

14文章

1887浏览量

111435 -

pll

+关注

关注

6文章

976浏览量

137589 -

倍频电路

+关注

关注

4文章

12浏览量

32894 -

除频器

+关注

关注

0文章

2浏览量

5028

发布评论请先 登录

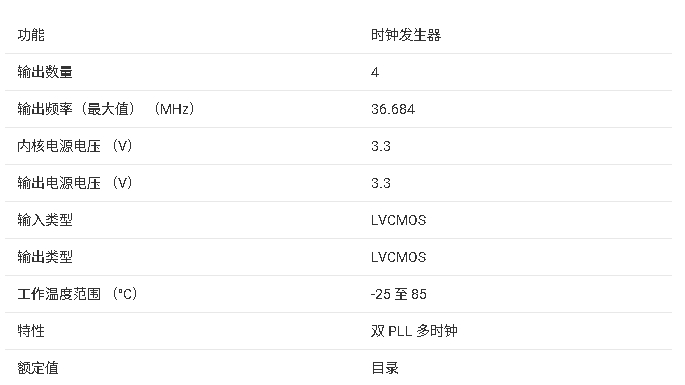

PLL1708双PLL多时钟发生器技术文档总结

PLL1707/PLL1708 双PLL多时钟发生器技术文档总结

易灵思 FPGA TJ375的PLL的动态配置

智多晶PLL使用注意事项

PLL用法

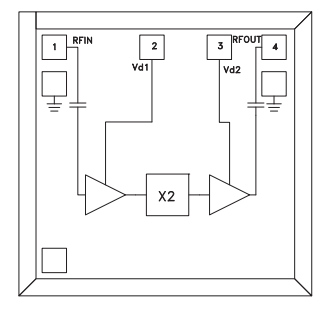

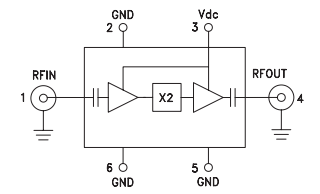

HMC448 x2有源倍频器芯片技术手册

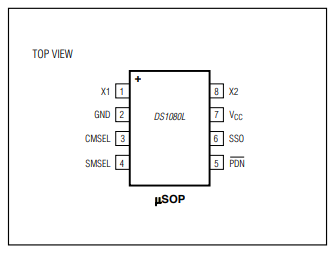

DS1080L扩频晶振倍频器技术手册

HMC-C034 x2有源倍频器模块技术手册

pll倍频最大倍数

pll倍频最大倍数

评论