运放电路优点

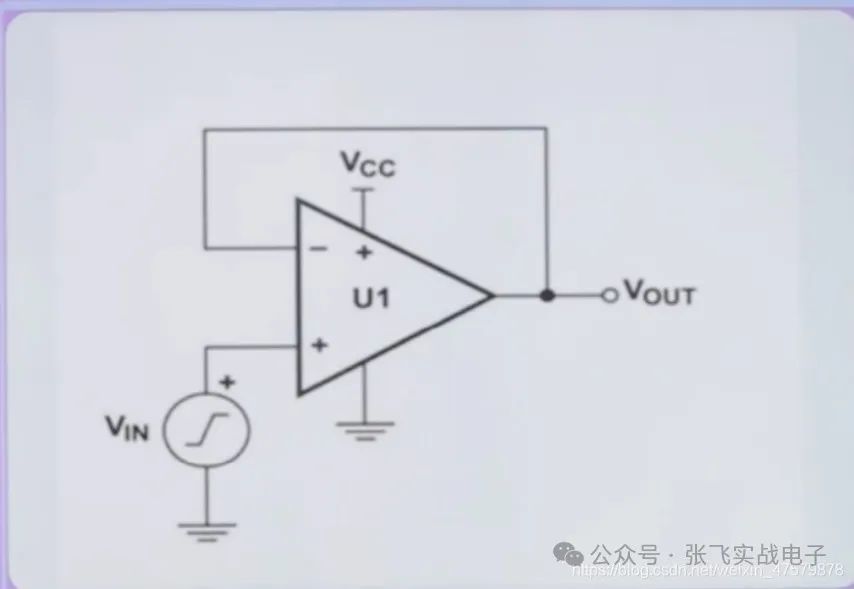

运放电路是一种广泛使用的电路,具有许多优点。在本文中,我们将探讨运放电路的优点,并简要介绍其原理和应用。我们将详细解释运放电路如何工作,以及它们在现代电子设备中发挥的作用。

首先,运放电路具有高增益,这使得它们在许多电路应用中非常有用。这是因为它们可以提供大量的输出信号,并将其放大到预定的电平。运放电路中独立的电流放大器可以用来放大信号,而独立的电压放大器则可以提供增益。这些放大器的组合构成了一个完整的运放电路。这意味着使用运放电路可以获得非常高的增益,而不需要使用大量的元器件来实现它。

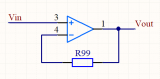

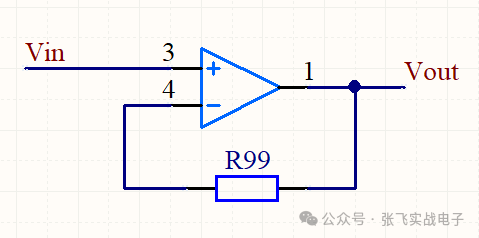

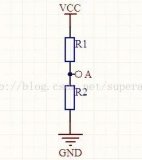

其次,运放电路可以方便地控制和调节。这是因为大多数运放电路都有可调的电阻,比如电压反馈电路和电阻分压电路。这些电阻可以用来控制电路的增益、带宽和输入和输出电压。这使得这些电路非常适合实现各种参数的可调电路,从而增加了电路的灵活性和优化性能。

第三,运放电路具有很低的噪声水平。这是因为在运放电路的输入阻抗非常高,而输出阻抗非常低的情况下,它们可以非常有效地减少噪声和干扰。如果运放电路被正确抑制和接地,它们可以大大减少电路中的各种噪声和干扰。

第四,运放电路可以通过多种方式使用。在现代电子设备中,运放电路被广泛应用于各种应用中。比如,在音频系统中,运放电路被用来增加音频信号,以及存储和处理音频数据。在通信和电视领域,运放电路被用来处理视频信号,包括放大和分组。还有其他各种应用,如测量、传感、控制和信号处理等等,使用了不同的运放电路。

最后,运放电路可以实现消费成本低。运放电路可通过标准化制造过程驱动批量生产,这将使成本降低。此外,由于通过封装和标准的连接方式,运放电路可以与其他电子元器件轻松集成,这也有助于成本降低。相对于自定义电路来说,运放电路的生产成本更低,且精度也更高。

在总体上,运放电路在现代电子设备中起着重要的作用。它们具有高增益、可控制性强、噪声低、多功能、成本低的优势。这些优势使运放电路成为许多电路应用中必不可少的组成部分。为此,我们可以看到运放电路在未来的发展中将继续发挥它的作用并成为电子设备中不可或缺的技术。

-

传感器

+关注

关注

2574文章

54438浏览量

786358 -

运放电路

+关注

关注

39文章

367浏览量

36190 -

电流放大器

+关注

关注

4文章

51浏览量

24925 -

信号处理器

+关注

关注

1文章

263浏览量

26124 -

可调电阻

+关注

关注

0文章

51浏览量

5501

发布评论请先 登录

集成运放电路图

这里有70个经典运放电路,直接套用省时50%

一篇文章教你使用运放实现三角波、方波(详细电路分析)+multisim仿真

请问运放电路有哪些补偿方法以及如何补偿?

运放电路采集电流0~1A、电压0~15V

常用运放电路总结笔记

轨对轨双路运放电路NX722,低价高性能,可国产替代SGM722

运放电路输出波形发生振荡怎么办?不要慌,教你一步步分析问题所在

请问DAC7554的输出是否必须加一级运放电路?

运放电路中电容的常见身影

运放电路优点

运放电路优点

评论