器件在使用过程中最常见的失效模式之一就是电浪涌引起的电过载(EOS)损伤或烧毁。下面简聊下集成电路电浪涌的产生和预防。

1.什么是电浪涌(电过载EOS)

电源电网的波动,电路状态的变化,外来干扰信号的馈入以及旁邻元器件的失效,都会在电路中产生峰值很高的电流或电压脉冲,称为电浪涌(电过载EOS),电浪涌会使器件瞬间工作在超过最大额定值的状态下。电浪涌的平均功率很小,但瞬时功率很大,足以引起器件失效。有时较低功率的浪涌也会引起器件自激或CMOS电路闩锁效应而导致失效。电浪涌引起的失效占集成电路使用失效的50%以上。

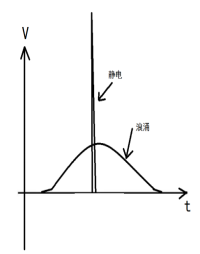

2.电浪涌与静电的区别

静电和电浪涌的区别在于静电是电压高而能量小,而浪涌能量较大,所以静电失效的电路表面看不到失效点,功耗并不超标。而电浪涌损伤往往在开帽镜检时可以看到,往往伴随着功耗的增加。

异常电应力烧毁一个器件,靠的不是器件感受到多少电压,而是该电应力在器件上产生了多少焦耳的热能。就好比说,一个人站在几十千伏高压输电线下没事,而用手摸220V交流电就有事是一个道理。

焦耳定律:流过纯阻性负载上产生的热能:

Q=W=Uit=U²/R×t

若R=5Ω,U1=1000V(静电),t1=1us(静电),则静电在半导体上产生的热能为:

Q1=1000²V/5Ω×1uS=200 毫焦耳

若R=5Ω,U2=50V(电浪涌),t2=100ms(电浪涌),则电浪涌在半导体结上产生的热能为:

Q2=50²V/5Ω×100mS=50 焦耳

3.电路中产生电浪涌的原因

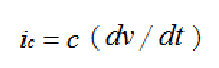

(a)电容负载接通时产生浪涌电流。开关电路驱动电容负载时,当电路中有电压突变时,由于电容上电压不能突变,就会产生一个为电容充电的瞬间电流。其大小为

例如一个稳压器,输出端接一个大电容,输入端没有接电容。在加电的瞬间,就会产生非常大的电流,将稳压器烧毁。

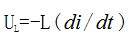

(b)电感负载关断时产生浪涌电压。当电路由开态向关态转换时,由于电感上的电流不能突变,在电感上就会产生一个阻止电流变化的浪涌电压。其大小为

。

(c)当电路中使用输入或输出变压器时,在输入变压器初级或输出变压器次级开路状态下,会感应很高的电压,导致电路输入级或输出级损伤。

(d)电网电压的波动,特别是突然的停电和来电,也会产生很大的浪涌电压和浪涌电流。

(e)由于接线错误或操作失误,如加电顺序错误导致电路中某些晶体管正向击穿或反相击穿,不但晶体管特性变坏,还会引起浪涌电流。

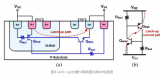

(f)数字电路翻转可产生浪涌电流。数字电路的翻转过程往往是部分晶体管由导通转为截止,而另一部分晶体管由截止转为导通。晶体管都有相应的开关时间,即存储电荷的充放电时间,翻转时会出现两部分晶体管同时导通,就在电路中形成了浪涌电流。

4.电浪涌的预防

(a)正确的使用集成电路,包括正确连接、加电顺序、断电顺序、试验程序、操作方法等。认真检查外围电子元器件,防止外围电子元器件失效导致浪涌产生。

(b)对于产生浪涌电流的电路,原则上串入适当的电感或电阻来加以消除。

(c)对于产生浪涌电压的电路,原则上并联一个电阻,或一个二极管(电压浪涌发生时二极管应导通)来加以消除。

(d)设计中按集成电路使用说明书进行电路设计,该使用的元器件一定不要少,如消振电容、电源滤波电容等。

(e)避免输入变压器初级和输出变压器次级开路,必要时,可并联一个电阻或电容。

-

集成电路

+关注

关注

5464文章

12681浏览量

375671 -

电浪涌

+关注

关注

0文章

3浏览量

5673

发布评论请先 登录

行芯科技亮相IIC 2026国际集成电路展览会暨研讨会

可调整阈值的过压保护控制集成电路

覆盖全“芯”链路!IICIE国际集成电路创新博览会解锁集成电路全链新商机

焕新启航·品质跃升 IICIE国际集成电路创新博览会,构建全球集成电路全产业链生态平台

CMOS集成电路中闩锁效应的产生与防护

PDK在集成电路领域的定义、组成和作用

国内首条碳基集成电路生产线正式投产运营

集成电路电浪涌的产生和预防

集成电路电浪涌的产生和预防

评论