本文包含以下几方面内容,程序设计,模块例化、运算符,模块设计模板

目标:用最简单,最简洁的方式,设计最易读,最高效的代码

1、程序设计

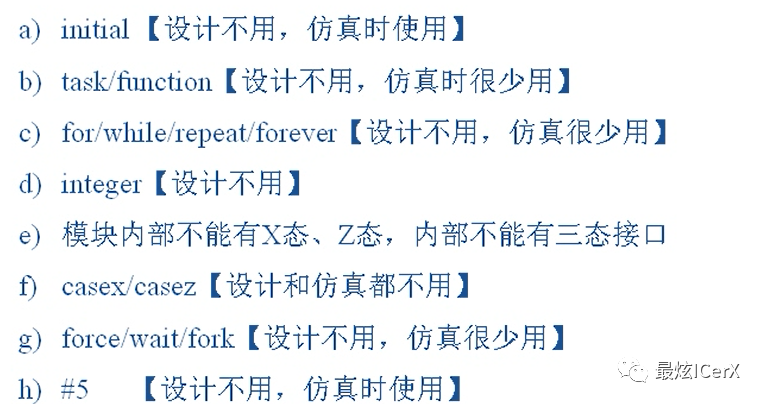

1)设计时不用的语法

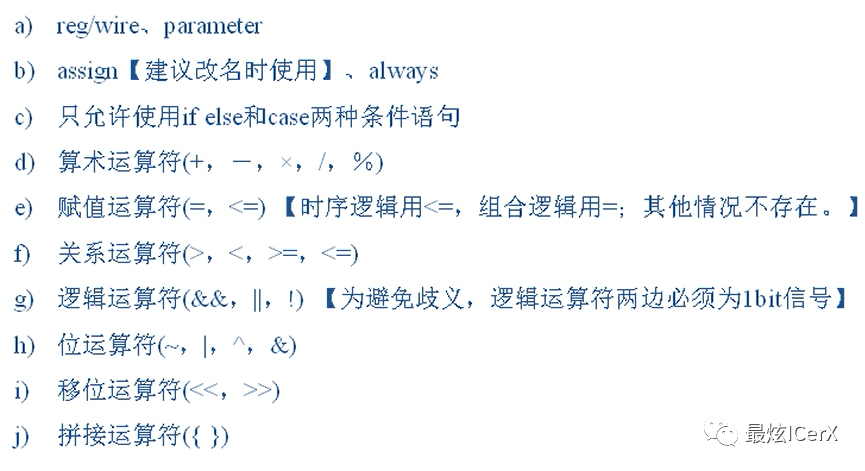

2)设计时使用的语法,主要为下述a,b,c三类

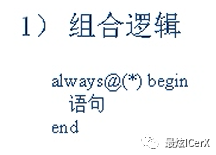

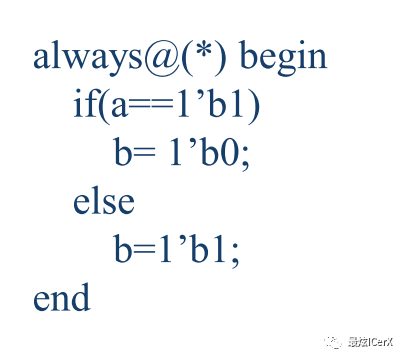

3)电路设计结构,主要有以下三种

4)电路设计要点

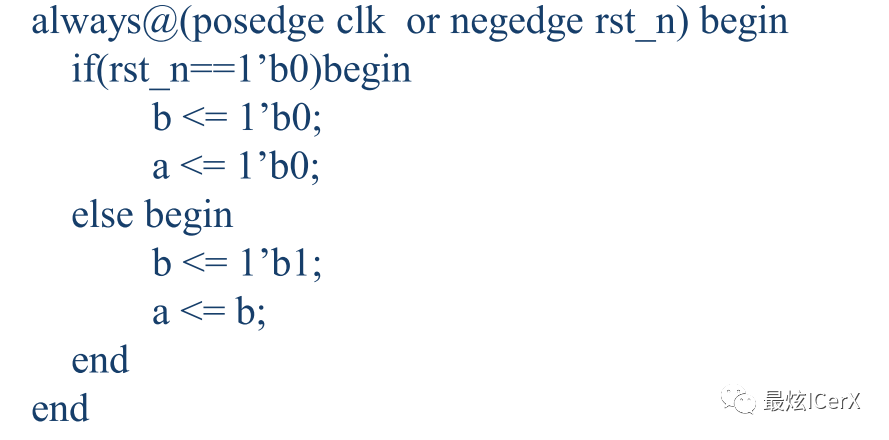

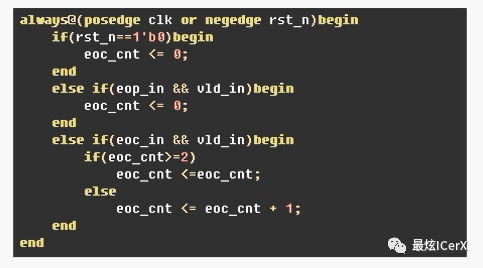

[1]一个always只产生一个信号

下述不合适

改为下述,只考虑一个信号,调试,分析,代码修改很方便,不需要考虑很多

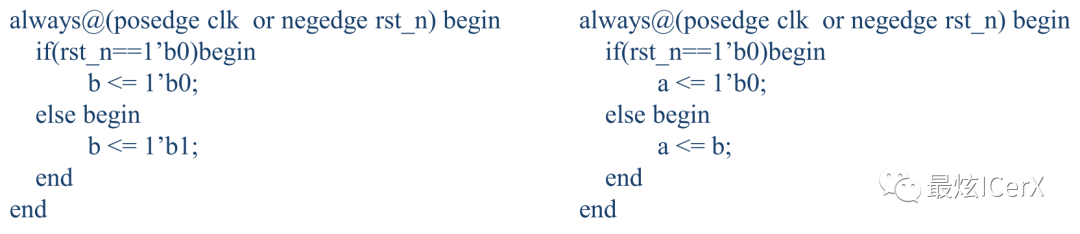

[2]一个信号只在一个always中产生

下述不符合要求,在多个always中产生

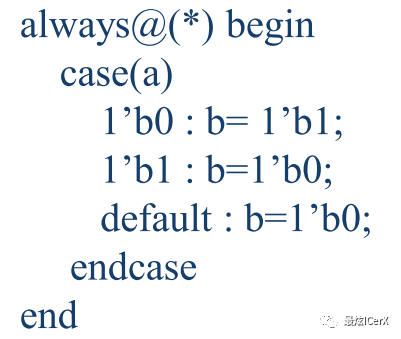

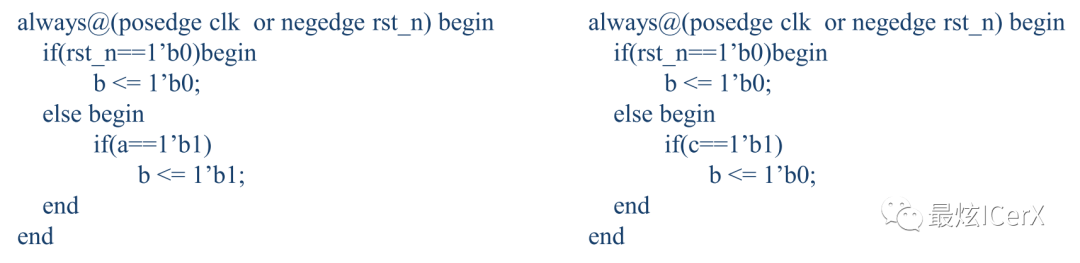

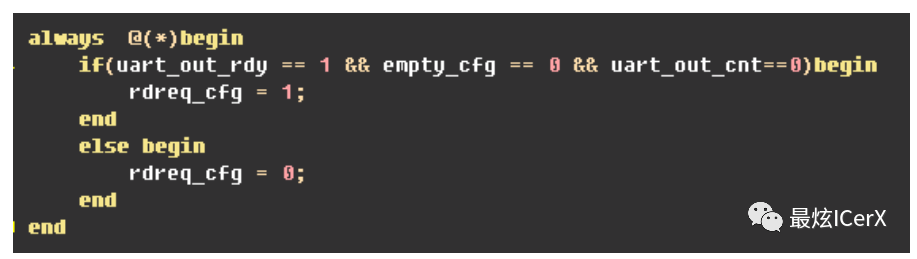

[3]always是描述一个信号产生的方法,即在什么情况下,信号值为多少,其它情况下,值又为多少,情况要全部考虑

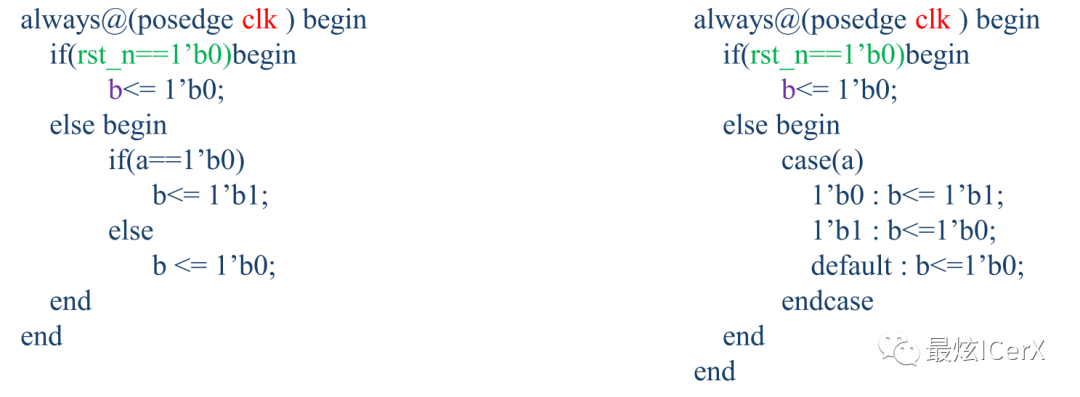

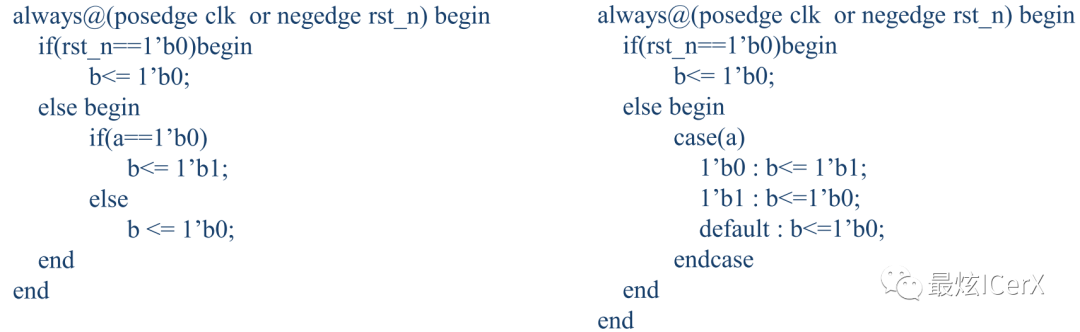

[4] 条件判断只允许使用if else和case,其它的不使用(包括casex);

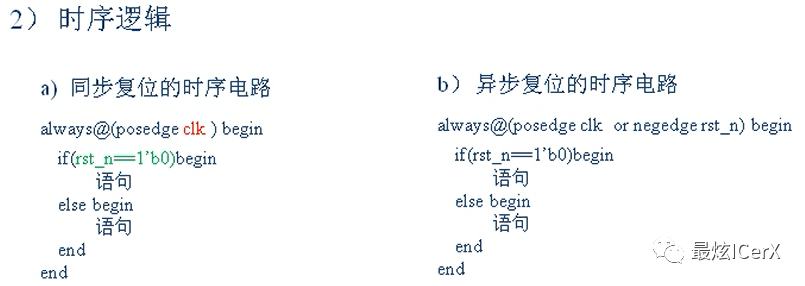

[5] 含有posedge或negedge的,一定是D触发器,是时序电路

[6] 想立即有结果用组合逻辑,延迟一拍有结果用时序逻辑

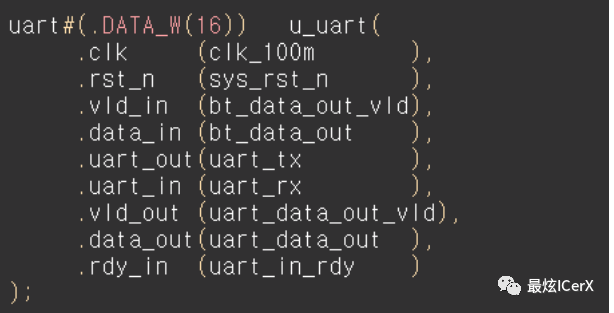

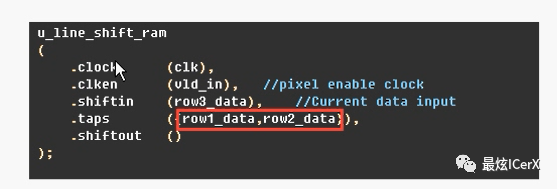

2、模块例化

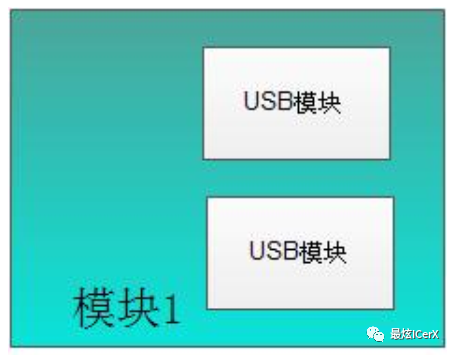

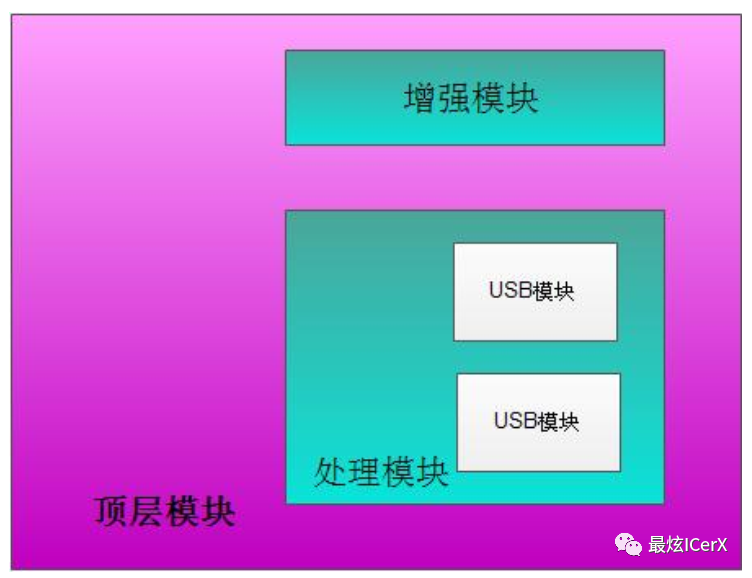

1)什么是例化,简单到复杂

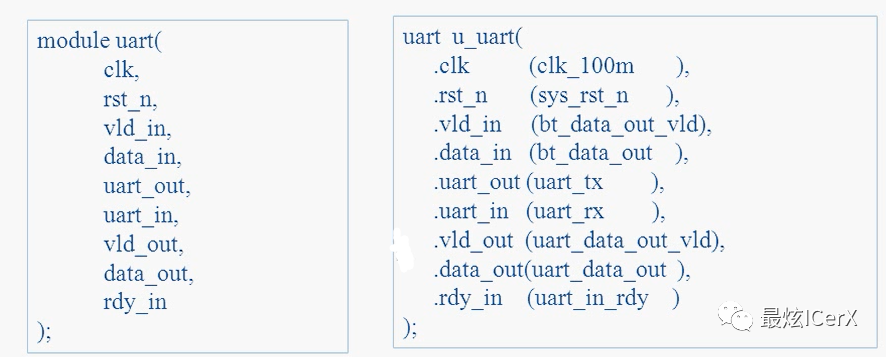

2)例化方法

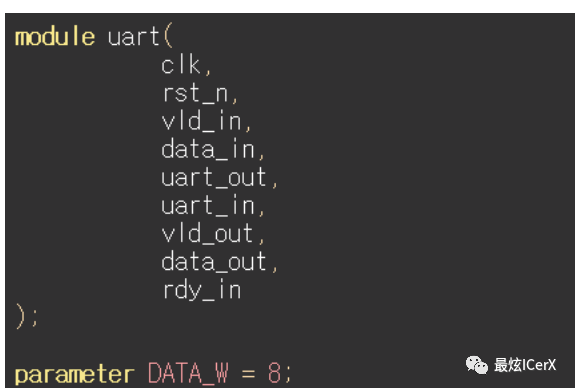

3)参数例化

3、运算符

1)信号类型reg/wire

(1)设计代码仅用reg,wire两种类型

(2)设计代码中,由本模块且是always产生的信号,为reg类型

(3)测试代码中,用initial产生的对测试模块的输入信号,用reg类型

(4)其它情况都用wire

(5)reg类型的信号,不一定产生寄存器

2)参数parameter

(1)将整个模块中的CNT_C_W替换成12

(2)参数名用大写

3)算术运算符(+,-,*,/,%)

(1)+,-,*用的多,/,%少用,消耗资源多,用的少

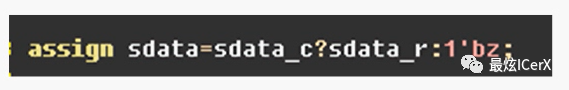

4)赋值运算符(=,<=),注:时序逻辑用<=,组合逻辑用=,其它情况不存在

(1)时序逻辑用<=

(2)组合逻辑用=

5)关系运算符(>,<,>=,<=)

6)逻辑运算符(&&,||,!)

(1)一般两边都是1bit信号,多Bit也可以

(2)一般用于条件判断

7)位运算符(~,|,^,&)

(1)一般用于赋值

8)移位运算符(<<,>>)

(1)一般用于乘除运算

(2)右移1位表示除2,左移1位表示乘2

9)拼接运算符({ })

(1){a[0],b[3:2]}

(2){{3{a[0]}},b[2],a[1]}

4、模块设计模板

1)解析电路功能

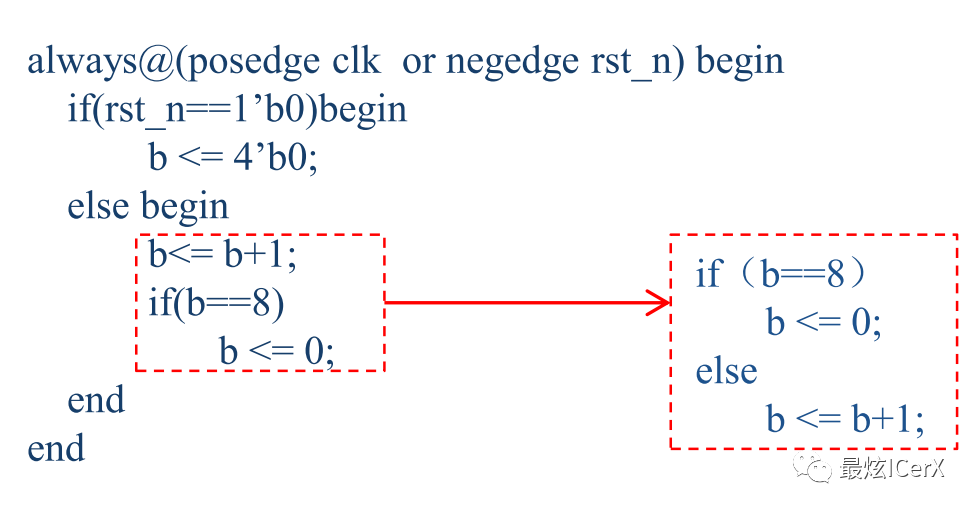

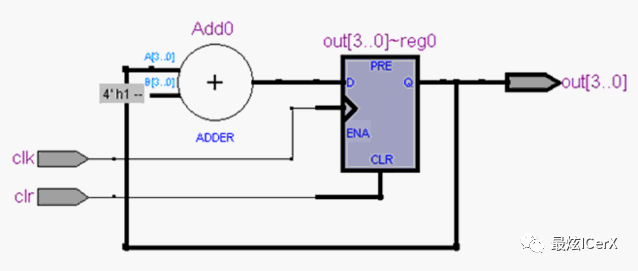

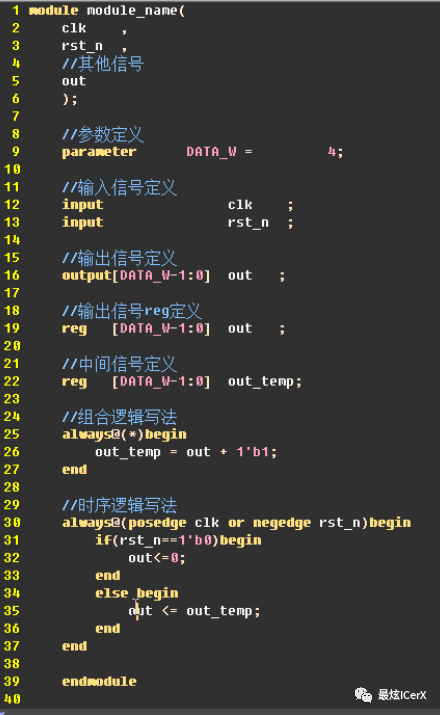

下图为自加1的电路图,左边为组合逻辑,右边为时序逻辑

2)修改电路设计模块

verilog模板

规则:输出信号必须打一拍送出去,所以会在always中赋值,所以输出信号定义为reg类型

先定义,位宽参数,输入,输出,中间信号,编写组合逻辑,时序逻辑代码,下述为上图加法器代码

-

IC设计

+关注

关注

38文章

1405浏览量

108411 -

Verilog

+关注

关注

31文章

1374浏览量

114713 -

程序

+关注

关注

117文章

3848浏览量

85459 -

Verilog设计

+关注

关注

0文章

20浏览量

6750

发布评论请先 登录

IC设计之Verilog代码规范

IC设计之Verilog代码规范

评论