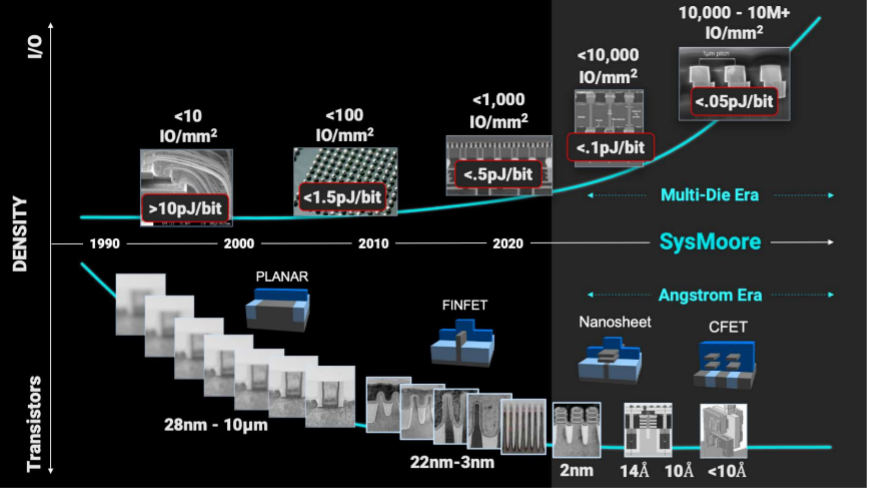

数十年来,在摩尔定律的影响下,半导体公司每隔两年,就会将集成电路(IC)上容纳的晶体管数量增加一倍。随着摩尔定律的放缓,SoC的器件微缩也明显放慢了脚步,而更新、更复杂的工艺节点成本却持续稳步上升。然而,随着“万物智能”带来的爆发式影响和无处不在的人工智能(AI)极大推动人们追求更快的速度和数量更多的晶体管,市场对更快、更好和更智能的芯片的需求只会越来越大。我们将摩尔定律的规模复杂性与新系统复杂性需求的这种交汇融合称为SysMoore时代。

新思科技董事长兼首席执行官Aart de Geus博士表示,半导体公司正在利用新的Multi-Die系统来彻底改变架构功能和形式,以便满足市场需求。事实上,将大型单片式芯片设计分解为多个经验证的小裸片,不仅可以提高良率,而且长期下来可以降低芯片成本,并有助于提供更多可定制的SKU。在新思科技最近发布的行业洞察报告《Multi-Die系统推动半导体设计变革》中,Aartde Geus博士在开篇章节中指出,通过跨行业合作,芯片开发者在降低每比特能量转换的同时,极大地提高了连接密度。该报告还收录了Ansys、Arm、博世、谷歌、英特尔和三星等公司对Multi-Die系统的看法。

随着埃米级晶体管与Multi-Die硅基板交汇融合,经典的摩尔定律已将接力棒传递给了SysMoore。如今,新思科技跟踪了一百多种Multi-Die系统设计,其中既有硬件/软件数字孪生方法、Multi-Die互联IP方法,也有AI驱动的芯片设计方法。总之,我们与代表着未来方向的众多SysMoore领先公司保持着密切合作。

Aart de Geus

董事长兼首席执行官

新思科技

本文将简要介绍该报告中的关键要点,并概述业内领先企业的观点。

2.5D和3D封装技术助力Multi-Die系统的加速采用

Ansys:

随着传统摩尔定律的微缩方案逼近物理极限,为了追求更高的电子系统密度,我们开始借助2.5D和3D封装技术过渡到Multi-Die系统。不过能否成功采用Multi-Die系统取决于能否克服多尺度(multi-scale)、多物理场(multi-physics)和多组织(multi-organizational)协调这三大挑战。

先进的Multi-Die系统将三种设计尺度融合到一项设计挑战当中,跨越了六个数量级:从纳米级IC设计到毫米级封装设计,再到厘米级3D-IC系统。这些解决方案分为三个工具套件(IC、系统和封装),它们需要集成到一个解决方案中。

Multi-Die系统具有良率更高、功能更强大的潜力,已经为高性能计算(HPC)处理器和显卡产品供应商带来了积极的影响,也有利于在云边缘实现AI和机器学习(ML)。

Arm:

由共同封装芯粒组成的Multi-Die系统将广泛运用于整个行业。许多企业将能通过在多种产品中重复使用各个芯粒,分摊其在硬件和软件工程上的投资。复杂系统将经过清晰划分,从而降低风险和成本,并缩短产品上市时间。

三星电子:

借助三星I-Cube 2.xD和X-Cube 3D IC等2.5D和3D封装技术,设备制造商可以在Multi-Die系统的基础上,寻求新的产品设计方案。AI、5G、自动驾驶技术和元宇宙科技的突破,有望重塑我们的生活方式;但要在单个芯片上实现驱动这些技术进步所需的功能和性能,相关工作变得日益复杂,成本效益也越来越低。通过将多个现有芯片的强大功能与多样性集成到统一的系统中,便极有可能设计出新的产品。

英特尔:

先进的封装技术已经在实现Multi-Die系统方面发挥了关键作用。借助EMIB和Foveros等先进的2.5D和3D封装技术进行异构集成,可以将多种来源、采用不同工艺节点设计的芯粒封装在一起,这为开发者提供了一条设计产品架构的有效路径。这种混合匹配方法有助于优化特殊功能、性能和成本,同时还能实现重复使用和模块化设计。

芯粒标准化和开放式生态系统至关重要

谷歌:

要最大限度地发挥先进封装解决方案和芯粒的影响,半导体行业必须超越传统的逻辑设计,欣然接受模块化解决方案。利用芯粒,我们可以在Multi-Die系统环境下开展协同设计,从而获得成本优势,并在异构IP模块中进行混合匹配集成。

我们有一个新的框架来实现高级计算,并通过在硬件和软件之间“创造和谐”来重新书写硬件创新的规则。系统级优化或协同设计,需要我们关注从应用级别一直到芯片级别的整个堆栈,这可以带来巨大的成效。

英特尔:

要打造精简的开放式小芯片生态系统,标准化是必要前提。通用芯粒互连技术(UCIe)就是一个这样的标准,这也是实现健全行业生态系统的关键步骤。

博世:

开放式芯粒生态系统对汽车行业至关重要。汽车的定制芯粒设计可以基于一些非汽车领域高性能应用中经验证的芯片架构。这将有助于将单体系统分解为多个裸片上的独立集成电路,再通过先进封装技术集成这些裸片,从而构成高性能的计算单元。该方法可实现超高程度的模块化和协同设计,有助于打造出色的可扩展产品。

同时,明确定义的接口、连接和标准对开放式汽车芯粒生态系统至关重要,众多生产类似芯粒的业内厂商对此的全力支持也同样重要。

新思科技强调,要想简化和优化异构Multi-Die系统设计,需要跨行业的合作。

Multi-Die系统的未来展望

SysMoore时代,Multi-Die系统能让开发者超越摩尔定律,应对各种复杂性挑战,从而以经济高效的方式更快地扩展系统功能、降低风险、缩短产品上市时间、以更低的功耗实现更高的吞吐量。Multi-die正在走向成熟,其进展与前景也被广泛看好。Multi-Die系统的创新示例包括:将架构分析和实现相结合,作为Multi-Die系统流程的一部分;借助AI,使效率和结果质量出现跨越式提高。

如今95%以上的先进芯片都采用新思科技的技术制造。我们跟踪了一百多种设计,该数目在过去六个月增长了约20%。透过这一增长,可以看到Multi-Die系统设计正在迅速走向成熟。即使是现在,我们的客户和合作伙伴仍在设计几年前还完全遥不可及的产品。到2030年代时,Multi-Die系统将广泛应用于各大市场。我之所以这样说,是因为我看到了它在新思科技工程实验室中的快速进展;与此同时,对于Multi-Die系统领域的投资源源不断。

SassineGhazi

总裁兼首席运营官

新思科技

进一步了解Multi-Die系统

新思科技致力于携手生态系统合作伙伴,共同迈入Multi-Die系统的创新时代。我们迫不及待地想要见证,利用我们的AI驱动EDA工具、IP产品和深厚的系统设计专业知识,半导体行业能够取得怎样的成就。

了解整个行业对加速采用Multi-Die系统的展望,扫描下方二维码或阅读原文获取新思科技行业洞察报告。

-

新思科技

+关注

关注

5文章

923浏览量

52638

原文标题:新思科技CEO Aart de Geus:SysMoore时代,Multi-Die系统将重塑半导体未来

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

新思科技助力UCIe 3.0快速落地

新思科技以AI驱动EDA加速Multi-Die创新

新思科技斩获2025年台积公司开放创新平台年度合作伙伴大奖

新思科技半导体设计解决方案拓展GenAI能力

新思科技UCIe IP解决方案实现片上网络互连

新思科技网页端虚拟原型工具的工作流程

新思科技与三星深化合作加速AI和Multi-Die设计

功率半导体器件——理论及应用

FPGA+AI王炸组合如何重塑未来世界:看看DeepSeek东方神秘力量如何预测......

利用新思科技Multi-Die解决方案加快创新速度

新思科技与英特尔携手完成UCIe互操作性测试

新思科技全新40G UCIe IP解决方案助力Multi-Die设计

新思科技助力晶圆代工厂迎接Multi-Die设计浪潮

利用Multi-Die设计的AI数据中心芯片对40G UCIe IP的需求

新思科技CEO Aart de Geus:SysMoore时代,Multi-Die系统将重塑半导体未来

新思科技CEO Aart de Geus:SysMoore时代,Multi-Die系统将重塑半导体未来

评论