SPARC沉积技术可满足新兴需求,为逻辑和DRAM器件提供有效隔离

作者:泛林集团公司副总裁兼电介质原子层沉积产品总经理Aaron Fellis

提升集成电路中的介电层性能可以在现在和未来的存储器和逻辑电路发展中产生巨大的战略影响。

想象一下,在一个挤满人的大房间里,每个人都有一条您需要的重要信息。他们都很乐意告诉您他们的信息,但问题是,他们都在同一时间说话。房间里的人越密集,就越难将想要关注的信息与周围的杂音区分开。

这就是“串扰”,维基百科将其定义为“传输系统上一个电路或通道上传输的信号在另一个电路或通道中产生不希望出现的影响”。如果您从事存储器和逻辑器件制造,那么您面临的情况就很像那个嘈杂的房间,因为在这当中非常邻近的范围里就有数十亿个动态随机存储器 (DRAM) 单元或逻辑晶体管。

典型的DRAM单元包含一个电容器(存储电荷用以代表1或0)、一个存取晶体管以及一个位线(用来读取电容器中的电荷)。为了追求更高的存储密度、更快的读写速度和尽量小的功耗,这些结构变得越来越小,并在最近几年演变出了3D结构设计。传感电压 (∆V) 和单元电容 (Cs) 随着每一代技术的演进而降低,因此需要相应的降低位线电容(CBL)。

类比嘈杂房间的例子,传感电压和单元电容的降低就好比你想听到的说话声变得更加不清晰,使你更难将他所说的内容区分于环境音。逻辑领域也是如此:越来越大的寄生电容(栅极间以及栅极和栅极触点之间)增加了串扰的风险。

串扰问题自电子学早期就一直存在。幸运的是,我们有一个众所周知的解决方式:隔离。在嘈杂的房间中,隔离需要在每个人的周围都放置隔音板;而在集成电路上,通常可以通过更好的介电薄膜来实现隔离。

其中“更好”的介电薄膜不仅仅意味着更低的介电常数 (k),尽管这是一个重要因素。薄膜也必须在不损害其他电路元件的情况下进行沉积,还要能够在随后的热加工、刻蚀、清洗和其他步骤中存留并且不改变任何特性,它们必须是无缺陷且均匀的。而且在3D电路的时代,仅实现平面厚度均匀还不够,即使是在垂直维度沉积,薄膜特性也必须一致。

此外还有一个因素:每个先进的芯片制造企业都面临着激烈的竞争,因此他们努力开发自己独特的方法,以获得更高的良率和更优的性能。负责这些工艺调整的工程师需要薄膜具有多样性和灵活性,这意味着他们能够调控薄膜成分以获得不同特性,包括刻蚀选择性等。每一代新技术带来更高的密度和复杂性,使得提升性能和良率更具挑战。回到嘈杂房间的类比,我们可以理解为房间变得越来越小,而人们说话的声音越来越大;可以用于隔离的空间越来越少,但却更需要隔离来听清我们想听到的声音。

在3D时代之前,工艺与整合工程师在寻求隔离方案时可以考虑已经被证实可行的方法:沉积可调的平面介电层或共形二氧化硅或氮化物。但现在的介电层既需要可调性和共形性,也需要能够沉积含有硅碳键的薄膜如SiCO,从而获得更高的刻蚀选择性,因为从环栅结构内隔离层到后段介电层再到先进的光刻工艺,刻蚀选择性在许多应用中变得越来越重要。同时,等离子体对电路的损伤也越来越令人担忧。

l 那么,隔离的探索方向在哪里?

一种方向是新的沉积技术SPARC,它可以很好地满足这些新兴需求。除了能在高深宽比结构中的不同深度保持一致的成分和特性外,SPARC还能沉积高度共形的SiCO薄膜。这种薄膜可以作为低介电常数隔离层为逻辑和DRAM器件提供有效隔离。

SPARC方法能够实现大范围的成分调控,同时仍保持极好的共形性。SPARC沉积的SiCO薄膜致密,坚固而漏电低,其介电常数 (k) 值为~4-4.4,并且可以在不氧化底层的情况下直接沉积于钴、钨等金属。这种薄膜在表现出极佳的粘附性的同时也展现了气密性。即使在400℃的低沉积温度下,碳也是完全交联的,只有很少甚至没有末端甲基,与其他SiOC薄膜相比,SPARC法制备的SiCO薄膜具有更好的热稳定性和化学稳定性。

重要的是,这些优点是在非等离子体环境中实现的。流入的基态自由基只与选定的前驱体分子中的特定键相互作用,因此断键具有选择性,这使得前驱体自由基粘附系数低,从而获得台阶覆盖性极高的薄膜。在沉积步骤中,硅碳键不会被断开,任何与前驱体分子中的硅结合的氧、氮或碳都被保留下来。为了实现大范围的成分调控,需要根据所需的薄膜类型来设计和选择前驱体。

在此工艺中,可以增加硅碳键的比例,同时降低硅氧键的密度。即使对于在不同温度下沉积的薄膜,相比于薄膜中的碳密度或碳总量,交联碳的量才是影响刻蚀选择性的主要因素。此外,这些SiCO薄膜在稀氢氟酸和热磷酸等典型湿法化学物质中的湿法刻蚀速率为零,因此可提供近乎无限的湿法刻蚀选择性。薄膜直到15Å都一直具有连续性,且没有针孔,不像原子层沉积氮化硅薄膜,至少需要30Å才没有针孔。

l SiCO薄膜在实践中表现如何?

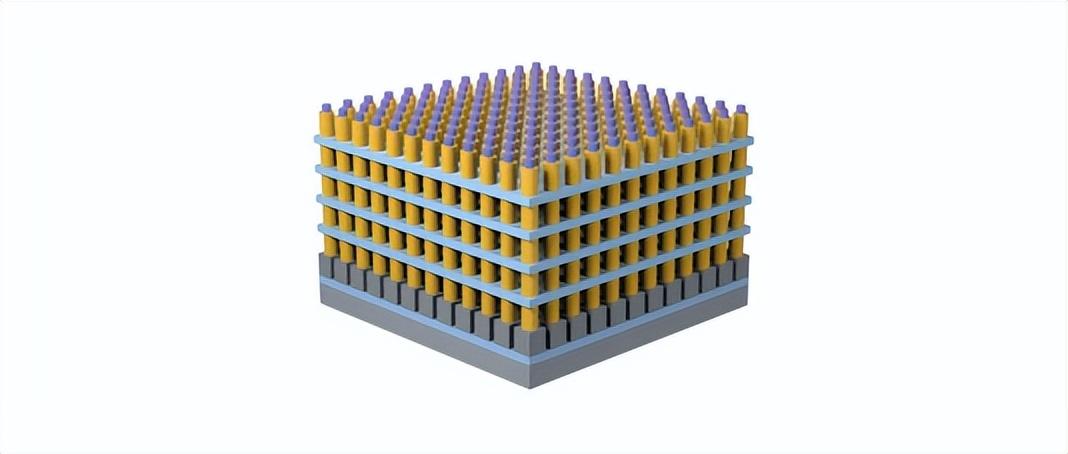

回到DRAM示例:正如前面提到的,技术节点演进过程中使得DRAM单元电容持续下降,为了提高获取DRAM单元信息的能力,需要相应的降低位线电容。

位线电容的很重要一部分(可能是一半)源自位线和存储节点单元之间的耦合。自20nm节点开始,空气间隙成为减少这种耦合的一种手段。空气间隙两侧的介电薄膜必须满足许多严格的标准,包括共形性、粘附性、气密性、介电常数和击穿电压。SPARC沉积的SiCO薄膜的特性可实现比传统材料更低的电容耦合,从而提高DRAM的性能。

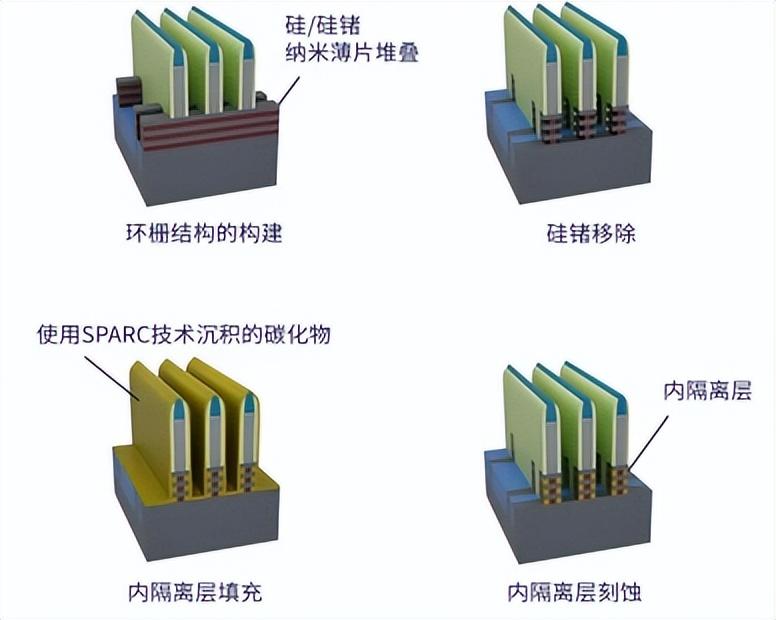

在逻辑器件中,栅极隔离层长期以来一直被认为是减少栅极之间以及栅极和栅极触点之间寄生电容、从而降低串扰风险的一种手段。隔离层的概念被引入了3D环栅结构中,但额外的要求是,隔离层材料还必须充当横向刻蚀停止层。

SPARC沉积的SiCO薄膜的综合特性也非常适合环栅结构逻辑器件这种情况。除其电学特性外,SiCO高度的各向异性和出色的刻蚀选择性还能帮助改善生产线。

在这两个例子中,串扰的最小化只是众多考虑因素之一。但这种最小化对整个电路开发有着重要影响,因为它减轻了电容器和晶体管的负担,使它们更容易实现其各自的功能。从全局来看,这减弱了寻求其他途径来提高性能的必要性,而那些途径都必然要付出成本,并且可能会带来新的复杂情况。这很好地体现了在基础层面上进行的细微升级也能产生巨大的影响力。

SPARC工艺的高度灵活性和适应性使其可以用于制备多种共形薄膜和不同成分的薄膜。例如,它可用于沉积高度可调的碳氮化硅薄膜。碳化硼和硼碳氮等优质共形硼基薄膜也已被成功制备,它们的溅射和刻蚀行为与硅基薄膜不同。

一个颇具潜力的应用是在先进的图形化技术方面,比如自对准四重图形化技术、自对准栅极和触点以及完全自对准通孔,这些技术都是为了制备日益复杂的3D结构所开发的,它们都需要用到具有特别突出的刻蚀选择性的材料,来实现更高的层间对准精度。先进图形化技术需要独特的隔离层、硬掩膜和刻蚀停止层材料的组合,以使它们能在各种等离子体刻蚀和湿法化学刻蚀过程中呈现出接近完美的选择性。基于碳化硼和硼碳氮的薄膜是很好的选择,因为它们具备合适的介电常数k值、共形性、电特性以及其他特点。

同样,使用SPARC技术沉积的、基于碳化硅的薄膜在3D NAND存储孔的制造中也非常有用,因为它们有良好的可调性,且对氧化物和氮化物具有很好的选择性。在任何基于等离子体的工艺出现问题时,使用自由基来制造薄膜的能力是很有吸引力的新选项。

很少有比半导体制造迭代得更快的行业,这对开发和整合日新月异的生产工艺组合提出了不断挑战。半导体行业一直面临着如3D整合等新问题和像串扰这样持续存在的问题,因而需要工程师们的智慧和创造力确保技术的与时俱进,也需要像SPARC这样的创新设备支持技术的实现,以确保“每条信息都被清楚听到”。

审核编辑 黄宇

-

半导体

+关注

关注

339文章

31222浏览量

266458 -

薄膜

+关注

关注

1文章

374浏览量

46260 -

串扰

+关注

关注

4文章

196浏览量

27874 -

隔离

+关注

关注

4文章

1300浏览量

33759

发布评论请先 登录

PCB设计与串扰-真实世界的串扰(上)

【连载笔记】信号完整性-串扰和轨道塌陷

EMC的串扰是什么?

示波器通道间串扰的影响

串扰的类型,串扰产生的原因?

SiCO薄膜在实践中表现如何?低介电薄膜如何解决串扰、隔离问题

使用新一代高度可调的低介电薄膜来解决串扰、隔离等制造挑战

使用新一代高度可调的低介电薄膜来解决串扰、隔离等制造挑战

评论