完整形式 :

CRP:时钟重新收敛悲观主义。

什么是 CRP(时钟重新收敛悲观主义)?

正如“聚合”的意思(字典)“两个或多个事物聚集在一起的发生”。所以我们可以假设它也与 2 个时钟路径聚集在一起有关。 (了解时钟路径请参考另一篇博客-静态时序分析基础:第1部分“时序路径”)

现在假设有如图所示的 2 个触发器电路。

正如您所看到的,翻牌共享一个公共时钟,但物理上放置在同一芯片的不同位置。或者以其他方式,您可以说启动时钟路径和捕获时钟路径(请参阅静态时序分析基础:第 1 部分“时序路径”以定义启动和捕获时钟路径)共享时钟树中的公共段,直到知道为“公共点”(在上图中,您可以看到“公共点”被写为“到目前为止两个触发器公共的时钟路径”)。 2 个时钟路径与此不同。

我们知道,每个单元都有两种类型的延迟作为其规范的一部分,“最大延迟”和“最小延迟”。在设计中有多种场景,我们使用特定单元的最大延迟或最小延迟。如时序分析时的最佳情况分析(BC)、最坏情况(WC)分析、OCV(片上变异)分析等。

让我们考虑公共段的最大延迟和最小延迟为

最大延迟=1.2ns

最小延迟=1.0ns。

现在,如果在时序分析期间出现必须对一个时序路径使用最大延迟而对另一时序路径使用最小延迟的情况(例如在 OCV 分析期间),则必须对公共路径使用 2 个不同的值。但实际上,同一组单元对于不同的时钟路径不会有不同的行为。

例如,对于设置检查,它使用启动时钟路径的最大延迟(1.2ns + 延迟,因为启动路径中的其余电路)和捕获时钟路径的最小延迟(1.0ns + 延迟,因为启动路径中的其余电路)。发射路径中电路的其余部分。

然而,在物理设计中,时钟树公共部分上的单元无法同时实现其最大和最小延迟值。因此,公共点将存在单个延迟值,该延迟值将传播到启动和捕获时钟路径。这与我们上面描述的时序分析方法相冲突,因为我们在公共点使用两组延迟值。

因此,我们的时序报告包含人为引入的悲观情绪,这种悲观情绪源自我们对沿着时钟网络的这一公共部分的启动和捕获路径使用最大和最小延迟。这种悲观主义的价值是时钟网络中公共点的最大和最小延迟之间的差异。

由于这种效应(在本例中为 0.2 ns)而产生的悲观量称为“时钟再收敛悲观度”。

时钟再收敛悲观 =(最大时钟延迟)-(最小时钟延迟)

注意:上述情况对于保留检查也是相同的。

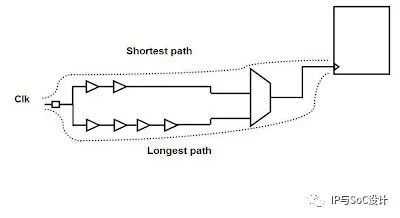

类似类型的情况也可能出现在不同类型的电路中。让我们讨论其中之一。请看下图。

馈入多路复用器的两个时钟路径不能同时处于活动状态,但分析可以考虑一次建立或保持检查的较短和较长路径。这会导致不同的启动和捕获时钟路径延迟以及随之而来的悲观情绪。

如何去除CRP?

这种不准确性的自动校正称为时钟再收敛悲观消除 (CRPR)。默认情况下,大多数工具(用于时序计算的EDA工具)禁用此功能(自动校正)。您可以通过在时序分析期间设置一个/多个变量来启用此功能。不同的工具对此有不同的变量。请参阅相应工具的用户指南或手册。

审核编辑:汤梓红

-

时钟

+关注

关注

11文章

1999浏览量

135228 -

触发器

+关注

关注

14文章

2065浏览量

63545 -

时序分析

+关注

关注

2文章

130浏览量

24273 -

静态时序

+关注

关注

0文章

20浏览量

7074

原文标题:博文速递:Clock Reconvergence Pessimism (CRP) basic

文章出处:【微信号:IP与SoC设计,微信公众号:IP与SoC设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

时序分析和时序约束的基本概念详细说明

FPGA设计中时序分析的基本概念

时序分析基本概念介绍—Timing Arc

时序分析基本概念解析

时序分析基本概念解析

评论