液相外延是碲镉汞(MCT)薄膜生长领域最成熟的一种方法,被众多红外探测器研究机构和生产商所采用。然而由于MCT材料自身属性和具体制备工艺的原因,液相外延生长过程中不可避免地会产生各种缺陷,从而降低红外探测器的性能。

据麦姆斯咨询报道,近期,昆明物理研究所的科研团队在《红外与激光工程》期刊上发表了以“液相外延碲镉汞薄膜缺陷综述”为主题的文章。该文章第一作者为起文斌工程师,主要从事红外材料与器件方面的研究工作;通讯作者为丛树仁高级工程师,主要从事红外材料与器件方面的研究工作。

文中基于已公开发表的论文总结归纳了LPE方法生长的MCT薄膜所存在的缺陷,主要包括点缺陷、位错、表面缺陷、生长波纹以及生长台阶。文中同时归纳分析了各种缺陷的产生原因,提炼出缺陷背后的形成机制和抑制措施,以及对LPE方法生长低缺陷密度MCT薄膜提供指导。

点缺陷

MCT薄膜的点缺陷可分为材料主元素点缺陷(空位、反位和填隙)和杂质点缺陷。这些点缺陷往往会在材料内形成浅能级缺陷或深能级缺陷,从而影响半导体材料的载流子导电类型、载流子浓度和迁移率以及载流子寿命等电学性能。提高载流子迁移率和寿命能够实现探测器量子效率的提升以及暗电流的降低,对开发高性能HOT器件和长波、甚长波器件至关重要。

主元素点缺陷

根据文献报道,Hg空位是MCT材料中最典型的浅能级受主缺陷,会对材料的载流子类型及浓度产生重要的影响。从材料组分和结构来看,MCT中还可能产生Cd空位并形成浅受主能级。然而事实上,Vydyanath等通过计算发现,对于Cd组分为0.2的MCT材料,Cd空位的生成焓为4.7 eV,比Hg空位的2.2 eV大,这主要归因于材料中较弱的Te-Hg键。

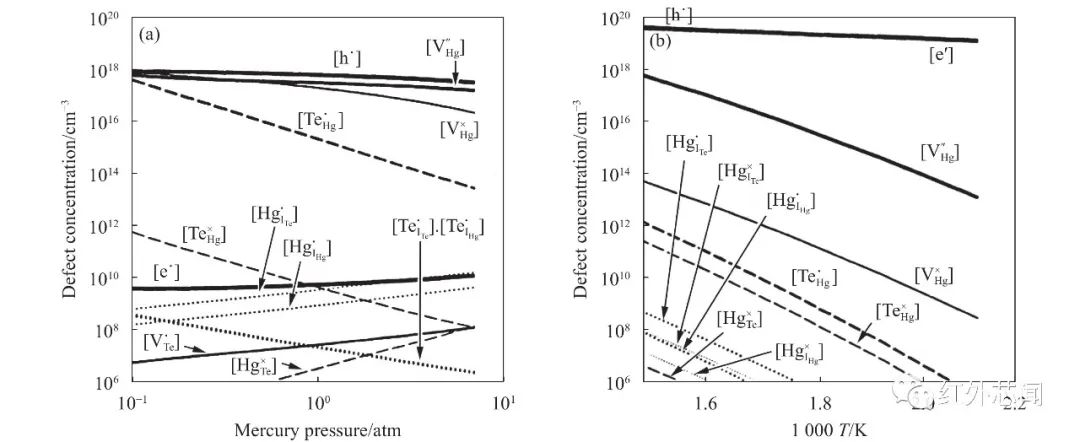

因此,不管在液相外延生长过程还是后期的退火过程中,相对于Cd空位,Hg空位的生成都占主导。Herding等采用第一性原理和局域密度近似的方法研究了退火过程中的Hg分压和温度对缺陷浓度的影响,其中作者假设材料在淬火冷却到77 K过程中缺陷总浓度不发生改变,但是电子和空穴在低温下可以达到新的平衡,结果如图1所示。图1(a)展示了Hg分压对缺陷浓度的影响,由此可以看出,在所有考虑到的点缺陷类型中,Hg空位的浓度最高;同时随着Hg分压的增大,材料中的Hg空位浓度会降低。

具体机理是:在更高的Hg分压下,材料中的更多Hg空位将被填充,因此浓度下降。图1(b)为退火温度对缺陷浓度的影响,从结果可以发现,Hg分压不变的情况下,随着退火温度的增大,Hg空位浓度也会增大,主要是因为高温使Hg原子从Hg位上发生脱离。以上所述只是简单的情况,在实际退火过程中,需要同时考虑Hg分压和退火温度的影响,根据所需材料的电学参数设置具体的退火温度和Hg分压。

图1 退火过程中的汞压(500 ℃退火并淬火冷却到77 K)

除了Hg空位,Te反位(TeHg)也是MCT材料中比较常见的一种点缺陷。如图1所示,在所考虑的几种点缺陷类型中,[TeHg]、[Te×Hg]的浓度仅次于Hg空位。得到这个结果的原因和缺陷生成能有关,计算结果表明,在MCT材料中,Te反位的缺陷生成能较低,仅次于Hg空位。因此,在液相外延生长过程中容易生成Te反位缺陷,尤其在富Te条件下生长时。根据图1的结果,[TeHg]和[Te×Hg]的浓度会随退火的温度和Hg分压变化,因此可以通过调节退火条件消除Te反位,例如Hg饱和退火。

综上,MCT薄膜中的主元素缺陷会影响材料的载流子类型和载流子浓度,而缺陷浓度同退火条件密切相关,因此可以通过选取合适的退火条件获得所设计的材料。退火条件的选取要格外注意,不同温度(包括薄膜的温度以及Hg饱和退火时Hg源的温度或Te饱和退火时Te源的温度)、不同降温速率、不同降温方式、不同退火管类型以及密封退火管的不同方式等都可能对点缺陷的生成、扩散以及消除产生影响,进而影响材料的载流子类型、载流子浓度和载流子迁移率。为了保证材料性能的稳定性,需要对退火条件的细微改变进行计算、研究和分析。

杂质点缺陷

根据文献报道,Cu、Ag、Li、Na这些元素会进入空位形成浅受主能级,影响材料的电学参数。Ⅰ族元素取代Hg位以及Ⅴ族元素取代Te位成为受主;而Ⅲ族取代Hg位以及Ⅶ族取代Te位成为施主。另外杂质元素也可能进入材料的填隙位置。同Hg空位一样,温度和Hg分压也会影响杂质缺陷的浓度。如图2(a)和(b)为Berding等计算的Li、Na和Cu杂质密度在MCT材料中的浓度随温度和Hg分压的变化。首先,随着温度升高,Hg空位浓度增大,进入Hg位置的Na也会增多,即NaHg浓度增大;相对应地,填隙位置的NaI浓度降低。而随着Hg分压增大,填隙位置的NaI浓度增加,归因于Hg位被Hg原子重新占据,杂质原子则被挤出。

图2 温度(a)和汞分压(470 ℃)(b)对本征点缺陷和杂质缺陷浓度的影响以及Li、Na、Cu元素在MCT材料和CdTe衬底中的化学势与Cd分压的关系(c)

非期望杂质元素大量进入MCT材料会严重影响材料的性能,一方面会限制材料的最低载流子浓度,进而影响到材料的电学性能;此外,杂质能级作为载流子复合中心会影响材料的载流子寿命。分析整个液相外延工艺,杂质可能来源于三方面:(1)液相外延母液中的杂质;(2)外延工艺过程中引入的外来杂质;(3)从衬底扩散进入薄膜的杂质。

通过提高原材料的纯度可以降低从母液引入的杂质,通过提高外延工艺环境的洁净度可以降低工艺过程引入的杂质。对于从衬底扩散进入薄膜的杂质,一方面应该尽可能降低衬底的杂质浓度;同时可以从降低衬底中杂质的化学势以及提高外延薄膜中杂质的化学势方面考虑。如图2(c)为Berding等计算的CdTe衬底和MCT薄膜中的杂质化学势同Cd分压的关系,在对衬底进行退火时,随着Cd分压增大,Cd空位减少,衬底中杂质的化学势也增大,因此高Cd压退火可以促使杂质从衬底向外部扩散;而在低Cd压退火时,衬底杂质的化学势会降低,可以促使杂质向衬底扩散。所以根据这个原理,可通过合适退火条件设计实现衬底中杂质的去除或抑制衬底中杂质向薄膜扩散。

位错类缺陷

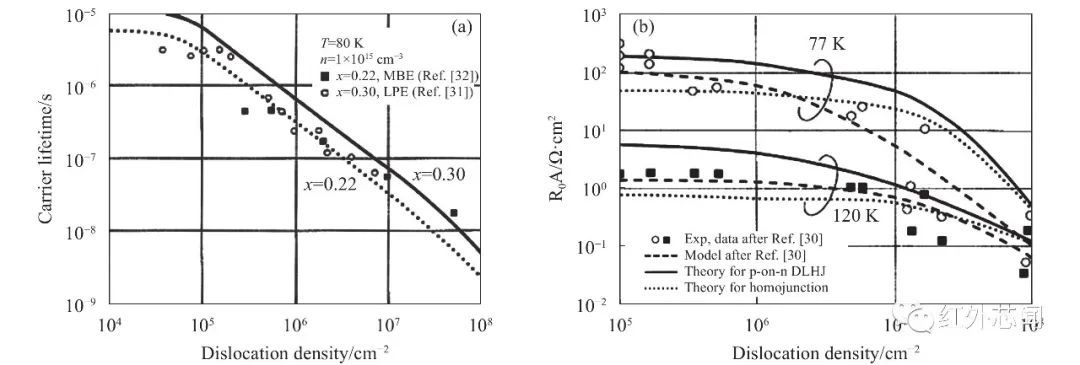

位错通常在高应变区域形成,这可能是由晶格错配、杂质、表面应力或其他形式的损伤引起的。位错的增加将严重影响探测器的性能,如图3所示,位错密度同载流子寿命和R₀A的值有很强的相关性。从图3(a)可知,当位错密度高于10⁵ cm⁻²时,载流子寿命迅速下降。从图3(b)可知,随着位错密度的增加,R₀A会减小,尤其低温时,对于77 K下工作的探测器,当位错密度高于10⁶ cm⁻²,R₀A值迅速下降。载流子寿命和R₀A的下降都会直接导致探测器性能的下降,因此需要对MCT薄膜的位错密度作严格的控制。MCT薄膜的位错主要有晶格失配造成的失配位错和从衬底延生而来的穿越位错,对这两种类型的位错分开进行讨论和归纳。

图3 MCT薄膜位错密度对载流子寿命(a)和器件R₀A(b)的影响

失配位错

在衬底表面进行液相外延生长时,如果衬底材料和外延材料之间晶格不匹配,即晶格常数不相等,外延层将在应变条件下生长。随着厚度的持续增加,薄膜中的应变能持续增大。研究结果表明,外延薄膜存在一个临界厚度tc,当薄膜厚度超过临界厚度时将以失配位错的形式释放压力。Cohen-Solal等指出外延层临界厚度同晶格失配η的−3/2次方成正比。为了降低失配位错对薄膜质量的影响,需要保证薄膜厚度不高于临界厚度。

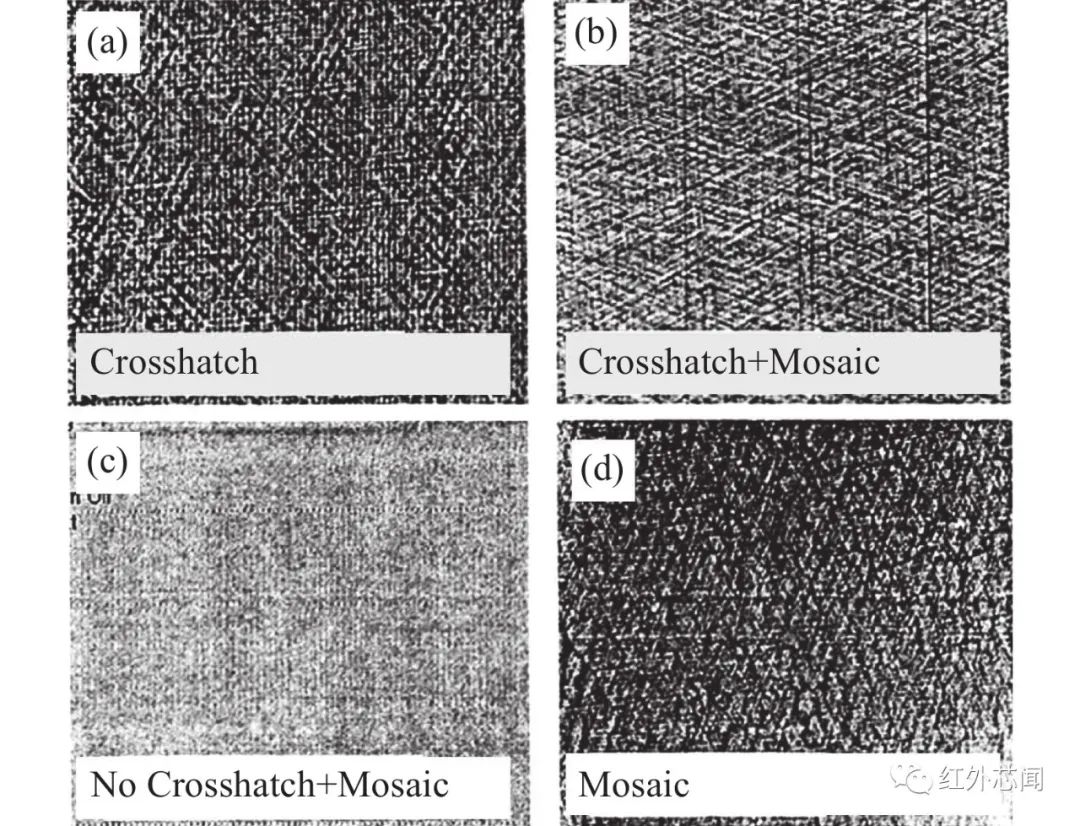

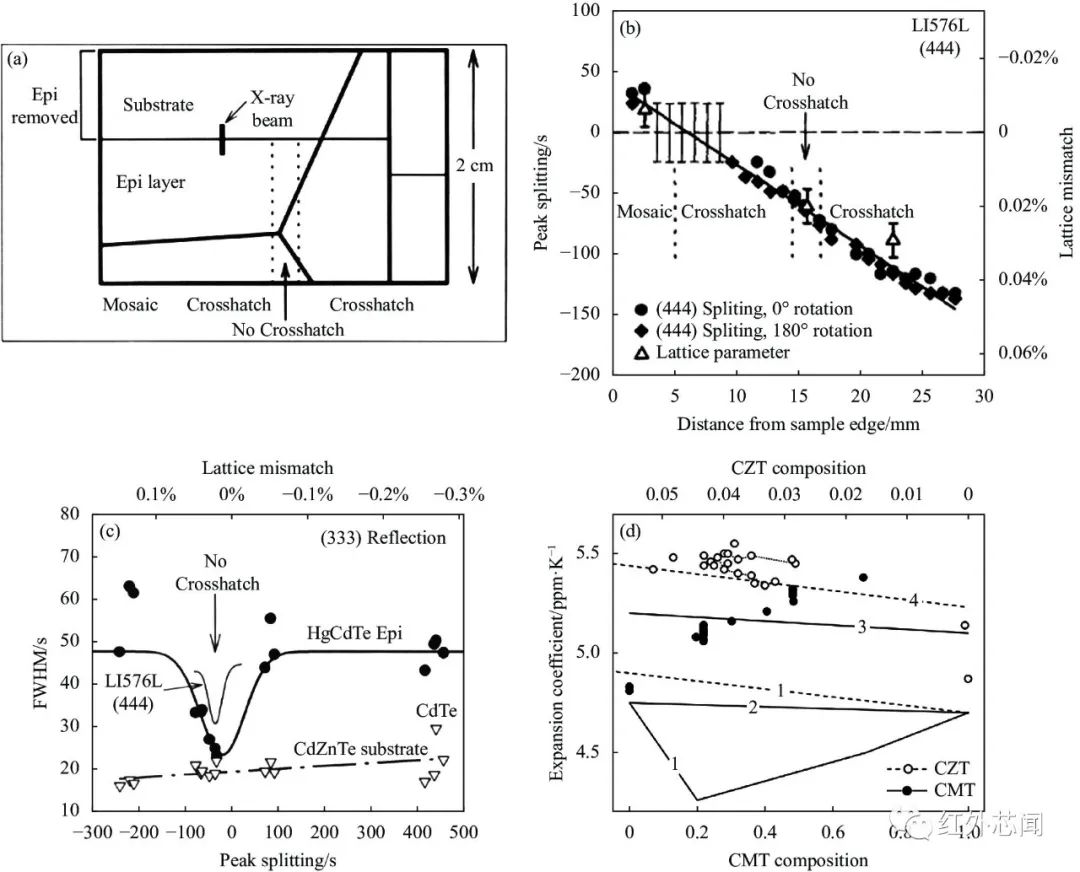

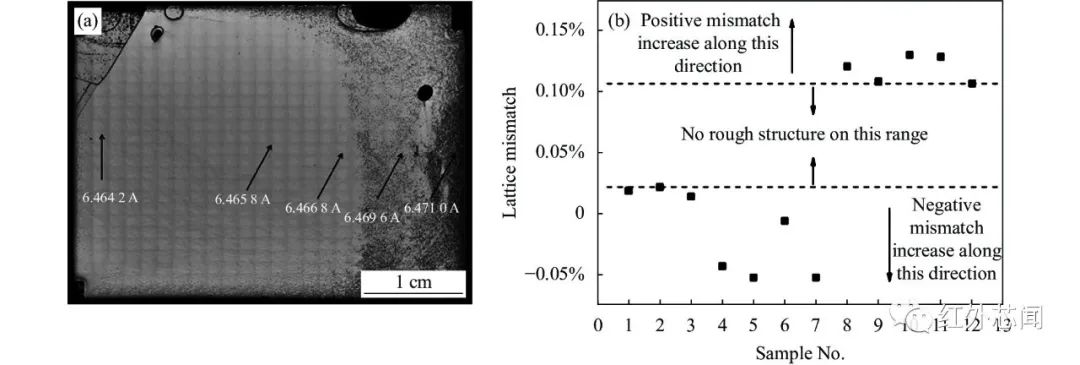

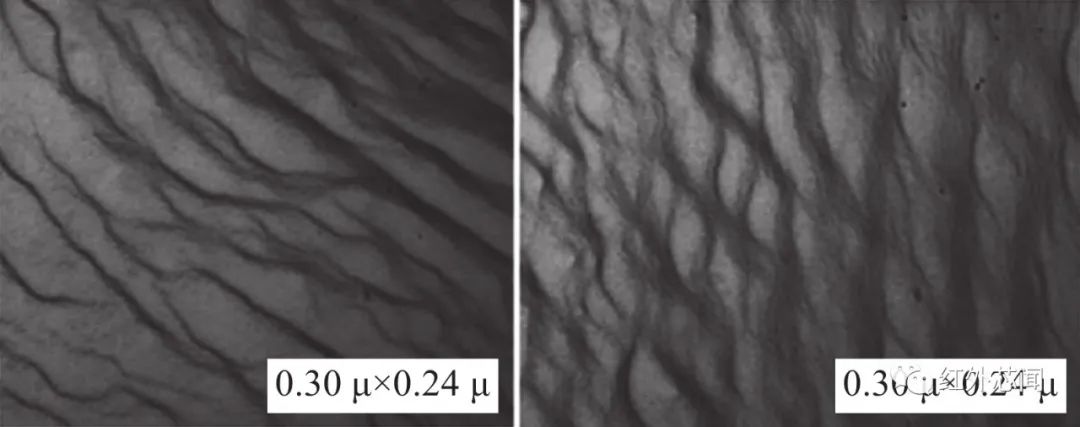

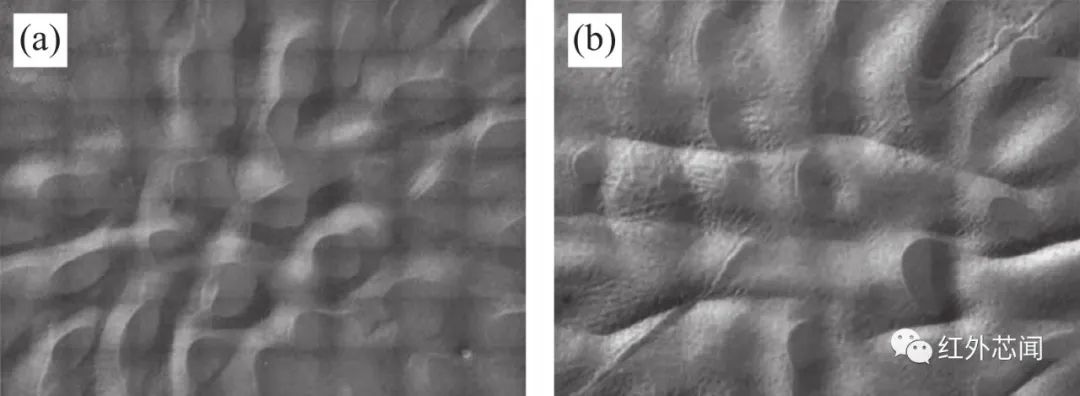

通过X射线衍射形貌相可在MCT薄膜表面观察到明显Crosshatch和Mosaic形貌,典型测试结果如图4所示,Crosshatch形貌表现为明显的交叉线(图4(a)),而Mosaic形貌存在镶嵌结构(图4(b))。研究表明,在MCT薄膜表面观察到的Crosshatch和Mosaic形貌同外延薄膜与衬底的晶格失配有关,或者说是与决定衬底晶格常数的Zn组份有关。图5(a)~(c)展示了同时出现Crosshatch区、无Crosshatch区和Mosaic区的MCT外延薄膜晶格失配、半峰宽测试结果,其中所有数据均在室温下进行测试。由图中的结果可以看出,在负晶格失配时,外延薄膜表面出现Mosaic形貌;在无晶格失配和较高晶格失配时,表面出现Crosshatch形貌;晶格失配在0.02%附近时,表面无Crosshatch和Mosaic形貌。此外,在无Crosshatch区,薄膜的半峰宽达到最小值,与衬底的半峰宽接近,如图5(c)所示。法国Sofradir公司也作过相类似的报道,他们指出对于特定Cd组份的MCT薄膜,存在衬底Zn组份最优值使薄膜的半峰宽最小。

图4 MCT薄膜表面的Crosshatch和Mosaic形貌(X射线形貌相图)

图5 晶格失配与薄膜表面Crosshatch形貌(a)、(b)和摇摆曲线半峰宽(c)的关系

在图5(b)和(c)的测试结果中可知,无Crosshatch区和半峰宽最小值并非出现在室温下的零失配位置,而是出现在微正失配位置,这主要与高温生长时和室温保存时的晶格匹配性存在区别有关。根据相关报道,CZT衬底和MCT薄膜的热膨胀系数存在一定的差别。如图5(d)所示,Skauli等测试了Zn组分为0~0.05的CZT衬底和Cd组分为0~0.7的MCT薄膜的热膨胀系数,从结果中可以发现,CZT的热膨胀系数要比MCT薄膜的大。由于热膨胀系数较大,当温度升到外延生长条件时(接近460 ℃),CZT衬底的晶格常数增加比例将比MCT薄膜大。图5(b)和(c)的测试条件为室温,因此在微正失配条件下才能使高温生长时实现晶格匹配,晶体质量也达到最优值。从图5(d)还可以看出,随着Cd组份的降低,MCT薄膜的热膨胀系数降低;随着Zn组分的增加,CZT的热膨胀系数增加。因此,对于长波器件而言,由于Cd组份低,Zn组份高,衬底和外延薄膜的热膨胀系数差别相比短波器件和中波器件要大,晶体质量最优时的室温晶格失配也将比短波和中波器件大。作进一步思考,碲镉汞红外探测器通常需要低温下工作(如77 K),同460 ℃左右的生长温度相比,晶格失配度将发生更大的变化,工作温度和生长温度下晶格失配的相关性以及两者对探测器性能的影响值得作进一步深入的研究。

当应力在薄膜内达到一定值时会发生应变弛豫,同时伴随着失配位错的产生。在应变弛豫条件下,对失配位错敏感的衍射峰半宽将随晶格失配量的增加而增大。随着晶格失配增大,晶体质量下降,薄膜表面的粗糙度(微起伏)也可能增大。Sun等对同时存在粗糙区域和平滑区域的薄膜进行了研究,图6(a)为薄膜的表面光学形貌图,箭头所标注的数值为与该位置对应的衬底的晶格常数。从结果中可以发现,衬底的晶格常数在面内并不均匀,粗糙区域和平滑区域的晶格常数相差尤其更大,由此可以说明晶格失配会导致外延薄膜表面变得更粗糙。

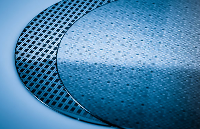

Sun等通过总结实验数据后发现,当晶格失配在0.02%~0.11%区间之外时,外延薄膜表面会出现粗糙结构(图6(b))。对于特定应用场景的红外探测器,MCT薄膜的波长和组份是确定的,因此为了降低薄膜同衬底的晶格失配,提高薄膜质量,需要对衬底的晶格常数进行严格的控制,也就是要对Zn组份进行严格控制。为了获得特定波长薄膜所对应的最优衬底Zn组份值,需要进行大量的数据分析拟合得到相应的对应曲线。同时对于大规模器件(4 k×4 k及以上),实现大尺寸衬底面内Zn组份高均匀性是获得高均匀性MCT薄膜的关键。通过大尺寸碲锌镉晶体定向生长技术攻关,实现晶圆制备可实现衬底的高Zn组份均匀性,为开发下一代大规模器件提供基础技术支撑。

图6 具有正常表面和粗糙表面的MCT薄膜(a)以及没有表面粗糙结构的晶格失配值范围(b)

穿越位错

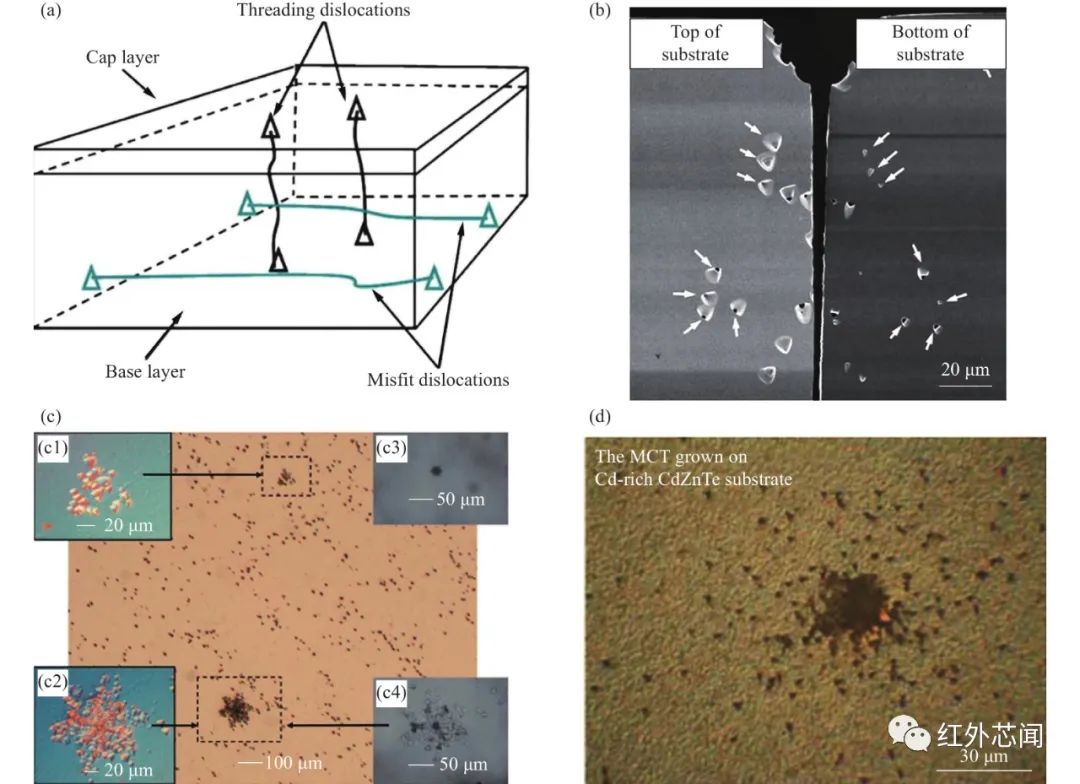

失配位错主要局域于衬底和外延薄膜的界面附近,而穿越位错则能够从衬底直接延伸到薄膜表面。图7(a)为失配位错和穿越位错的示意图,可以看到穿越位错起源于衬底,并能够穿越外延薄膜以及其上的Cap层。图7(b)为对薄膜(左图)以及去除薄膜后的衬底进行CrO₃/HF/HCl/H₂O腐蚀剂腐蚀并进行扫描电子显微镜(SEM)观察的结果,从结果可以发现薄膜表面的位错和衬底表面的位错有很强的相互关系,表明衬底的位错穿越到了薄膜中并延伸到表面。大量穿越位错的存在会严重降低外延薄膜的晶体质量,同时位错线可能穿过p-n结,进一步造成器件漏电流的增加,降低性能。因此,大量穿越位错的存在导致器件暗电流的增加,阻碍高性能HOT器件和长波、甚长波器件的开发。

图7 穿越位错的示意图(a)以及表征结果(b),衬底表面的富Cd沉积相及位错(c),起源于富Cd沉积相的MCT薄膜表面的位错(d)

根据以上分析,穿越位错的形成主要和衬底有关,衬底晶体生长过程中会形成大量位错,外延生长时这些位错能够穿越到外延薄膜中,从而影响薄膜的质量。根据目前的文献报道,CZT衬底中的富Cd沉积相周围会形成位错团,并且能够延伸到MCT外延薄膜中。图7(c)为富Cd沉积相在Everson腐蚀剂腐蚀后的光学形貌图,周围可以看到位错团簇,表明Cd沉积相会造成位错的增值。该位错团簇的形成主要和Cd沉积相的形成机理有关。在晶体生长过程中,CZT晶体内的Cd饱和度非常小,因此高Cd饱和度的富Cd熔体将以沉积相的形式进入到CZT晶体内;在降温过程中,由于同CZT的热膨胀系数存在差异,富Cd沉积相周围产生张应力,从而形成位错。Cd沉积相周围的位错能够穿越到MCT外延薄膜内,并影响晶体质量。图7(d)为采用Zhao氏腐蚀剂对富Cd沉积相的CZT衬底上生长的MCT外延薄膜的腐蚀坑进行光学显微镜观察的结果。从结果可以发现,衬底沉积相周围的位错穿越到了MCT薄膜中。和富Cd沉积相不同,目前文献中报道的富Te沉积相周围并未观察到位错增值。Sheng等对此进行了研究,他们指出在晶体生长过程中由于CZT晶体内的Te饱和度较高,富Te的CZT熔体可以进入到含有大量Cd空位的CZT晶体中;在降温过程中由于Te原子的塌陷造成富Te沉积相的生成,塌陷过程不产生张应力,因此不产生位错。

为了降低Cd沉积相带来的穿越位错密度,一方面需要对CZT生长工艺进行优化,从而抑制沉积相的生成,提高晶体质量。此外,通过富Te退火也可以减小衬底的Cd沉积相大小,如图8(a)所示。随着退火温度的提高,Cd沉积相尺寸减小的比例增大,这主要归因于高温下原子的扩散系数增加,促进原子的迁移,如图8(b)所示。随着退火的进行,富Cd沉积相引起的位错密度也会下降,如图8(c)所示,退火后的位错腐蚀坑密度大大下降。除了Cd沉积相周围形成的位错团簇,CZT晶体中还会产生其他的大量位错,总位错密度大约在10⁴~10⁵ cm⁻²。这些位错的产生非常复杂,同熔体中的杂质、坩埚壁的性质、熔体组分的化学计量偏离、振动和热应变等有关。此外,目前的研究结果表明,后期的退火工艺对位错的消除具有一定的效果,能够降低位错腐蚀坑密度。因此,为了降低CZT晶体中的位错密度,提高液相外延薄膜质量,在优化CZT生长工艺的同时应该进行后期的热处理,具体热处理条件需要通过实验进行开发,研究最优条件实现最小的沉积相尺寸和最低的位错密度。

图8 沉积相尺寸(a)和原子扩散系数(b)随退火温度的变化,退火前后富Cd沉积相腐蚀坑的形貌变化(c)

表面缺陷

对于液相外延MCT薄膜,目前在文献中报道的表面缺陷主要有孔洞、突起以及表面结晶等。这些表面缺陷会对探测器的性能造成严重的影响,尤其是当缺陷位于像元内或是缺陷的尺寸大于像元时,将造成探测率降低或像元失效,形成盲元,降低器件的有效像元率。文中根据文献报道,对孔洞、凸起等表面缺陷进行了总结和分析。

表面孔洞

根据文献报道,衬底表面杂质颗粒的存在是导致孔洞缺陷的一个重要原因之一,图9(a)分析了衬底表面的杂质颗粒对液相外延过程的影响,颗粒阻止了外延材料的正常成核及生长,而颗粒周围区域可以进行正常外延生长,因此逐渐发展成为孔洞缺陷。为了降低该类缺陷数量,需要提高操作环境和相关设备、原辅料的洁净度,减少衬底切割、磨抛等过程的杂质颗粒残留,同时对衬底进行充分的清洗,从而严格避免衬底处理过程以及外延生长过程的杂质颗粒引入。

图9 由表面杂质颗粒形成的孔洞缺陷(a)以及由衬底表面沉积相形成的孔洞缺陷(b)

除了杂质颗粒,衬底表面的沉积相也会导致孔洞缺陷的生成。图9(b)为衬底表面的沉积相与液相外延碲镉汞薄膜表面孔洞缺陷的对应关系,该孔洞从衬底表面的沉积相延伸到薄膜表面,深度达到了10 μm,同周围外延薄膜的厚度相近。衬底表面的沉积相导致外延薄膜中孔洞缺陷形成的机理为:衬底表面的Te和Cd沉积相与碲镉汞材料的晶格失配过大,阻止了成核反应,导致无法正常外延生长,而周围其他区域位置可以进行正常外延生长,从而形成了孔洞缺陷。采用合理的退火工艺减小衬底的沉积相尺寸或消除沉积相,从而提高液相外延薄膜的质量。如图8(a)所示,随着退火温度的增加,沉积相尺寸较小的比例增大。另外,对于富Te液相外延生长,由于相图中的Te角存在HgCdTe和Te的两相共存区,容易在液相外延生长时形成富Te夹杂物或沉淀物。

这些富Te夹杂物或沉淀物的生成也会破坏该位置的正常液相外延生长,并导致孔洞缺陷的生成,孔洞深度同Te夹杂物或沉淀物生成的位置有关。当然液相外延层中形成的富Te相也可能导致在薄膜表面形成凸起类缺陷,主要是因为经过元素扩散后,富Te相中的部分区域达到了与碲镉汞薄膜相近的元素水平,可以继续进行外延生长,进而在复杂生长环境的作用下形成了凸起。为了消除这类缺陷的生成,需要对温度、过冷度的液相外延生长条件进行严格的优化和控制,提高母液的均匀性,从而抑制Te夹杂物或沉淀物的生成。根据液相外延技术的特点,具体可采用温场均匀性优化、降温速率优化、石墨舟结构优化等实现整个生长过程中母液的高度均匀性。

表面凸点

液相外延碲镉汞薄膜表面上还经常存在凸点缺陷,该类缺陷也会对探测器的性能产生影响。

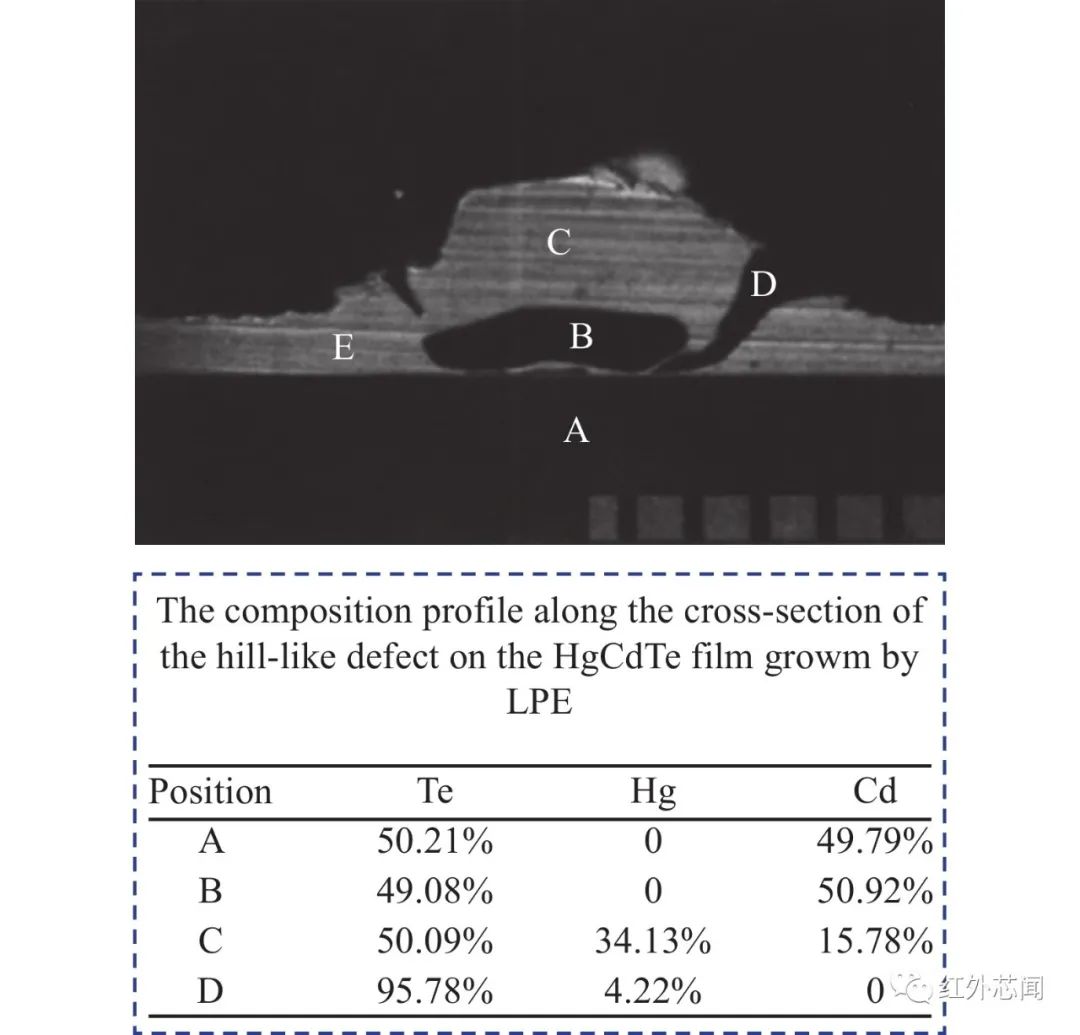

该类缺陷主要由衬底表面的衬底颗粒造成。图10为MCT薄膜表面凸起点的剖面照片和不同位置的元素含量图,其中E区为外延层,C区为凸起点,A区为衬底。从元素含量结果可以发现,C区的元素含量同外延层相同,说明该区域也进行了正常的外延生长;B区的元素含量同A区的衬底相同,说明B区应该是从衬底掉落的颗粒。分析结果可知,从衬底掉落的颗粒上也进行了正常的外延生长,因此相对于其他平整的衬底区域,该区域形成了凸起点。根据生成原因分析,为了抑制该类缺陷的生成,需要从两方面进行改进:(1)优化衬底切割及磨抛工艺,减少崩边;(2)对衬底进行充分的清洗,去除表面的残余颗粒。

图10 MCT薄膜表面凸起点缺陷剖面图及元素分布

此外,如3.1节所述,液相外延生长过程中形成的富Te沉淀相也可能造成表面凸起类缺陷生成,主要与生长过程中的元素扩散以及母液非均匀性有关,因此需要提高母液的均匀性来抑制此类缺陷的生成。外延薄膜表面的母液残留也呈现凸起状。对于水平推舟式液相外延生长,母液残留主要和石墨舟的结构有关,需要对舟的结构进行优化,从而提高第二次推舟过程中的母液清除率。

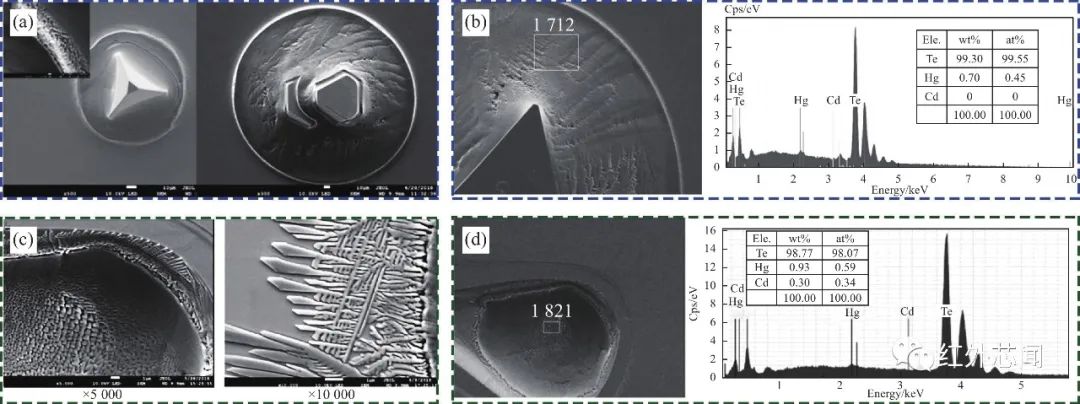

表面结晶类缺陷

如3.1节所述,对于富Te液相外延生长,由于相图中的Te角存在HgCdTe和Te的两相共存区,容易在液相外延生长时形成富Te夹杂相或沉淀相结晶析出。该类缺陷也会对探测器的性能产生影响,尤其对于小像元探测器,可能会造成盲元。图11为两种结晶类缺陷的扫描电镜形貌图和元素分析图,第一种为凸起类缺陷(图11(a)),顶端为三角形或六边形平台,然后通过圆形平台与外延薄膜接壤。经成分分析发现,顶端平台的成分同外延薄膜接近,而与外延薄膜接壤的圆形平台几乎由Te组成(图11(b))。如图11(c)和(d)所示的第二种缺陷为凹入类缺陷,经过放大后可见,该类缺陷在微观上呈枝晶状,并向四周延升;元素分析结果发现,几乎由Te组成。这两种缺陷同属于结晶类缺陷,都存在成分富Te的特征,主要形成原因是生长过程中母液不均匀,导致富Te相的析出。母液的均匀性同很多因素有关,包括母液温度梯度、降温速率、气体流量以及汞分压等,优化上述参数有助于抑制该类缺陷的生成,并提高外延薄膜的质量。

图11 两种表面结晶类缺陷SEM形貌图(a)、(c)及缺陷位置的成分分析(b)、(d)

生长台阶

表面台阶是液相外延碲镉汞薄膜的一种典型表面形貌,如图12所示,该缺陷以梯田状形貌重复出现。严重的台阶状形貌会造成器件相应均匀性下降,影响探测器性能的提升,尤其是对于未来需要重点发展的4 k×4 k、8 k×8 k等大规模探测器。

图12 MCT表面生长台阶的光学形貌图

其原因主要同衬底的晶相偏离[111]方向有关,当晶相偏离角度超过理想值范围时,液相外延过程中将出现密集的台阶状生长。当CZT衬底的晶相偏离[111]方向的角度小于0.2°时,液相外延薄膜表面较平整。Li等也指出,对于CdTe衬底垂直浸渍生长MCT薄膜的工艺,衬底偏离[111]方向的角度存在一个临界取向,当偏角在1.2° ~ 2°区间时,液相外延薄膜的质量较高。根据以往的研究结果,随着偏角的增大,台阶状生长的程度会先增加后减小,当超过临界值时,台阶状生长的程度反而减小,出现该现象主要归因于较大偏角使台阶变宽,以至于薄膜面内的台阶数量减少。

但衬底偏角过大可能会导致其他缺陷的生成或增加。Yang等研究指出,对于水平推舟式液相外延薄膜,当CZT衬底的偏角大于0.2°时,台阶状形貌开始出现;其次,当偏角超过1.4°时,台阶状生长的程度降低,整体表面形貌同偏角低于0.2°时相近,然而会出现大量尺寸大于30 μm的缺陷,降低薄膜的表面质量。因此,综合以上文献报道的结果,为了生长出无台阶的液相外延薄膜,可以将衬底的偏角控制到0.2°以内或者大于临界值;不过为了同时兼顾薄膜的整体表面质量,降低缺陷密度,将偏角控制到0.2°以内是一个较为理想的方案。

当然,影响液相外延薄膜台阶生长的因素可能并非只有衬底晶相偏角。PARKER等研究了衬底回融过程、晶相偏离、衬底支架设计、搅拌速率、温度梯度和生长速率对垂直浸渍式液相外延薄膜台阶生长的影响,他们发现,除了晶相偏离,其他因素也会对台阶的形貌产生影响。

例如,如果外延前的衬底回融过程将使薄膜表面变得粗糙,薄膜的台阶状生长过程可能受到影响;温度梯度增加会促使速率梯度的增加,从而可能导致台阶状生长;在较低的生长速率下,由于组分过冷容易产生台阶,但在较高的生长速率下,选择性吸附得到抑制,减小了组分过冷,因此可能更不容易出现台阶状生长。总之,除了衬底晶相偏角,外延生长工艺参数也可能对薄膜台阶状生长产生影响。为了有效抑制台阶状生长,降低衬底偏角的同时需要优化降温速率、石墨舟纵向温场等外延工艺参数。在具体的生产和科研中,需要细致研究这些参数对薄膜台阶状形貌的综合影响,获得最优条件,有效抑制台阶状生长。

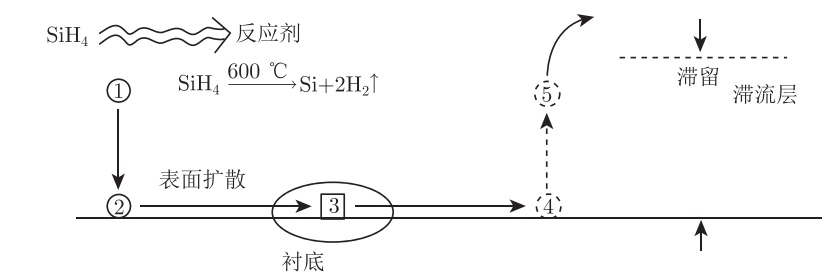

生长波纹

MCT薄膜表面波纹的典型形貌特征如图13(a)和(b)所示,薄膜表面呈现出较大的宏观起伏,会对平整度产生影响。薄膜表面出现宏观波纹生长主要起源于生长母液中熔体的对流。一方面,在生长之前衬底与母液接触时,如果母液处于未饱和状态,也就是温度高于液相线,衬底会发生回融,衬底材料补充到熔体中造成不稳定的密度梯度,从而引发熔体对流;衬底回融过程本身对液相外延生长具有积极的意义,能够清除表面污染以及提高衬底的润湿性,但是该过程难以进行有效控制,容易因熔体对流而在衬底表面形成波纹,该波纹能够在外延生长过程中延伸到薄膜表面。另一方面,在外延生长过程中,如果熔体内存在横向的温度梯度,有可能会引起对流,从而导致组分的分布不均匀,造成表面波纹状生长。

图13 MCT表面波纹的光学形貌(a)、(b)

消除薄膜表面波纹的具体方法可分为两种:(1)调节生长参数消除;(2)后续表面处理去除。对于后续的表面处理工艺,可进行机械抛光和化学抛光等方法,从而去除表面的起伏波纹,但该过程也会随之引入表面损伤层,对探测器性能造成影响。因此,相比之下,通过调节生长参数消除是比较理想的方案。外延生长前复杂的衬底回融过程以及生长过程中的石墨舟温场分布、降温速率、失汞率、母液的形状和厚度等会对外延薄膜的波纹生长产生影响。因此可通过优化石墨舟结构(具体为提高滑块和舟架之间的相互配合度)以及根据所设计的薄膜厚度研究最优降温速率、过冷度以及失汞率等实现整个生长过程中的温场均匀以及母液组份均匀,从而有效抑制表面波纹的产生。

结论

通过实现大尺寸碲锌镉晶体生长技术的突破以及大尺寸MCT薄膜缺陷抑制技术攻关,LPE基MCT薄膜将是发展2 k×2 k、4 k×4 k、8 k×8 k等大规模探测器的首选材料;同时高质量LPE基MCT薄膜的制备将为高性能HOT器件以及长波、甚长波器件的研制提供基础技术支撑。这些高性能探测器同时是国内未来几年急需要快速发展的重要方向。

缺陷控制是制备高质量MCT薄膜最主要的难点之一。为了加深对液相外延碲镉汞薄膜缺陷的认识,文中根据目前的文献报道综述了不同类型缺陷的形成机理以及相应的消除方法,具体总结的缺陷类型包括:点缺陷(主元素点缺陷和杂质点缺陷)、位错类缺陷(失配位错和穿越位错)、表面缺陷(孔洞、凸点、结晶)、生长台阶以及生长波纹。通过总结发现:(1)主元素点缺陷主要以双电离化的汞空位为主,通过调节退火条件可以精确控制汞空位的浓度,进而控制材料的电学参数,同时为了降低杂质点缺陷,需要减少各工艺过程中的杂质引入;(2)位错类缺陷主要和衬底有关,通过选择生长温度下同MCT晶格匹配的CZT衬底可以减小失配位错造成的晶体质量下降,而通过衬底生长工艺优化降低位错密度可以减小穿越位错引起的探测器性能下降;(3)孔洞类缺陷主要和衬底的质量有关,需要减少衬底的沉积相尺寸和数量以及表面杂质引入;(4)凸点类缺陷主要和生长界面的衬底颗粒以及生长过程中的沉淀相析出等有关,需要优化衬底质量,减少崩边,同时优化外延生长工艺,提高母液均匀性;(5)结晶类缺陷主要和外延生长过程有关,需要优化外延生长工艺,提高母液组份均匀性;(6)衬底的晶相偏离是导致台阶生长的主要原因,需要将偏角控制到0.2°以内,然而衬底回融过程、外延温场等生长参数也可能对台阶生长产生影响,需要进行综合考量和控制;(7)表面波纹的生长主要和熔体的对流有关,需要对石墨舟温场、过冷度、生长速率以及衬底回融过程等外延生长参数进行综合优化,提高对整个工艺过程的控制能力。

审核编辑:刘清

-

处理器

+关注

关注

68文章

20339浏览量

255175 -

晶体管

+关注

关注

78文章

10443浏览量

148676 -

SEM

+关注

关注

0文章

274浏览量

15720 -

红外探测器

+关注

关注

5文章

326浏览量

19088 -

MCT

+关注

关注

0文章

16浏览量

5845

原文标题:综述:液相外延碲镉汞薄膜缺陷

文章出处:【微信号:MEMSensor,微信公众号:MEMS】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

外延应力如何提升芯片性能

集成电路制造中薄膜生长工艺的发展历程和分类

椭偏仪在半导体的应用|不同厚度c-AlN外延薄膜的结构和光学性质

外延片氧化清洗流程介绍

汽车材料中的“汞”该怎么检测

东软医疗NeuViz P10碲锌镉光子计数CT获批上市

铝电解电容的 “环保转身”:无汞电解液如何让它从 “电子垃圾” 变 “可回收物”?

台阶仪应用 | 半导体GaAs/Si异质外延层表面粗糙度优化

攻克锂电池研发痛点-电解液浸润量化表征

饮料液位及瓶盖缺陷检测视觉系统

一文详解外延生长技术

PanDao:确认缺陷等级并用于加工

薄膜电弱点测试仪的常见问题及解决方案

液相外延碲镉汞薄膜缺陷综述

液相外延碲镉汞薄膜缺陷综述

评论