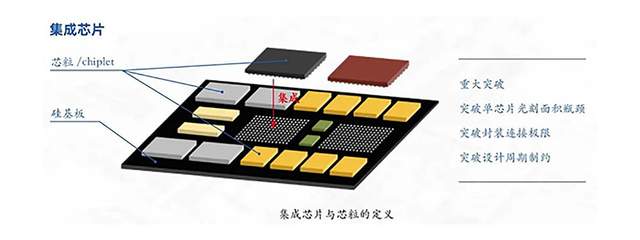

Chiplet与异构集成即将改变电子系统的设计、测试和制造方式。芯片行业的“先知”们相信这个未来是不可避免的。他们认为,相比于最新的设计节点,异构、多chiplet的架构可以降低成本和功耗。尽管这一预测得到了广泛的接受,但问题是,大家都准备好了吗?

前不久在旧金山的Semicon West上,Applied Materials举行了异构集成讨论会,由他们的半导体产品组的副总裁Vincent DiCaprio主持,讨论了fabless芯片设计师、代工厂和生产设备公司开发的特定异构集成策略。这场对话揭示出,在市场看到更广泛的chiplet实现之前,还存在一些重大挑战。

Chiplet的前景吸引了许多fabless公司,尤其是那些为高性能计算解决方案开发CPU和GPU的公司。然而,高昂的成本让Qualcomm这样重要的玩家望而怯步。异构集成的一个大问题是先进的封装技术,wafer-to-wafer键合或die-to-wafer键合。

代工厂或是OSAT(outsourced semiconductor assembly and test),谁来负责高级封装技术是个大问题。这两方将何时开始合作,如何合作?最重要的是,由于缺乏计量工具,讨论组的成员们纷纷表示,推动chiplet的快速采用变得难以负担。 小组讨论包括AMD、Intel、Qualcomm、Besi和EV Group的代表。Besi是一家设计和制造半导体设备的荷兰公司。总部位于奥地利的EV Group是晶圆键合和光刻设备供应商。

AMD:异构集成的早期采用者

AMD是异构集成的早期采用者。AMD的技术和产品工程高级副总裁Mark Fuselier将其描述为“跨越过去十年的旅程”。通过“将SoC解构成多个片段,然后在封装中重新组合起来”,AMD首先在数据中心设计了基于Zen的CPU。

但是,“当我们开始熟悉chiplet时,我们发现其中有更多的机会。”AMD的异构集成第二代是“将内存更靠近逻辑部分”。首先是在图形空间中使用了HBM(high bandwidth memory)。Fuselier称之为AMD的“一个转折点”,他解释说最近正在让SRAM更靠近CPU。

他指出,第三代更加令人兴奋。AMD看到其未来在于“实现真正的异构集成,优化chiplet以适应CPU或GPU计算。”它已经成为了“一个架构师的梦想,能够优化每一个计算空间中的工作负载。”

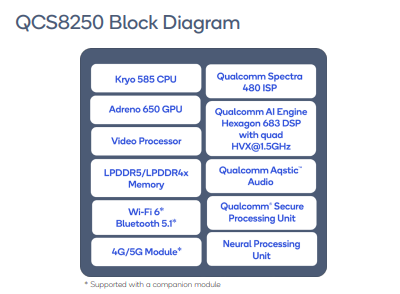

Qualcomm:移动领域中的chiplet?

当AMD利用异构集成服务于客户端和数据中心时,Qualcomm在移动领域的定位又在哪里呢?

Qualcomm的副总裁兼研究员Chidambaram指出,“Qualcomm要想在智能手机市场上继续生产更具竞争力的超大批量产品,我们需要超越摩尔定律的创新。”

他说:“五年前,我知道GAA将是2022年的技术。但是从现在起五年后,我不确定我们会做什么。”他强调,Qualcomm看到自己“走在横轴和纵轴之间的二维空间里”,其中“吞吐量成为一个关键向量,而不是规模”。

尽管Qualcomm对chiplet思考很多,但Chidambaram表示,由于chiplet无法满足Qualcomm的成本要求,所以还没有相关产品。

尽管如此,随着市场从5G转向6G,Qualcomm看到了chiplet的潜力。他解释说,从整体上看,一个系统有大量的射频、电源管理和内存。Chidambaram说:“插入损耗很大,功率放大器的性能必须非常接近系统芯片的其他部分。异构集成成为将所有这些整合在一起的关键。”

智能手机并不是6G转型唯一重要的领域。Chidambaram举了十字路口的例子。“一旦你完全实施了6G,借助异构集成将延迟从现有的7-8ms降低到1-2ms,你就可以让路边单元完全管理十字路口,人们甚至不需要停车。”

当然。他承认,启用这样的功能需要“大量的基础设施建设,才能履行所有的延迟要求和承诺,以及在路边单元上的连接数量。”

Intel:chiplet制造所需的关键技术

谈到异构集成,Intel拥有得天独厚的优势。Intel的业务涵盖了芯片设计、内部制造和外部代工服务。

Intel的高级副总裁兼装配/测试开发总经理Babak Sabi说:“未来,Intel看到了需要将大量的内核与内存结合……以绝对最低的延迟和最高的带宽”,这一切都会归结为“互连和封装问题”。

Sabi指出,可以通过混合键合来堆叠芯片,这有助于减少每比特的皮焦。除了这种物理连接,“横向集成”也是必要的,Sabi强调,以尽可能密集的方式连接芯片。他说,这一步需要创新,“超越我们在晶圆级装配中已经拥有的技术”。

这就是玻璃基板变得极其重要的地方。Sabi说:“它让我们能够将这些巨大的复合体组合在一起,你可以完全消除interposer。我知道大家都喜欢铜,但铜最终会耗尽高速通信的能量。”未来在于Sabi所说的“光学领域”。

混合键合的现状

无论是wafer-to-wafer还是die-to-wafer,混合键合都是实现chiplet高级封装的关键。

BE Semiconductor Industries N.V.(Besi)的CEO Richard Blickman表示,混合键合中最关键的元素是“装配、互连和前端之间的握手”。这个过程仍然“处于非常早期的阶段”。

尽管不愿预测混合键合何时会在更大规模上被采用,但Blickman强调,在过去的两年里,已经有了大批量chiplet设计的PoC。不过,他回顾说,flip chips在23年前就已推出,但多年后才成为主流,因此他建议大家耐心等待。他指出,混合键合需要更精确的粒子,这是设备供应商面临的“最大的敌人之一”。设备本身必须更小。

EV Group的技术执行总监Paul Lindner指出,“我们将晶圆键合视为规模提升的推动器……它提供了将有源层从一个晶圆转移到另一个晶圆的可能性,从而进入晶圆背面。”

Lindner指出,晶圆键合已经得到了不同的实现,包括SOI晶圆(键合晶圆)。另一个大量应用的例子是BSI传感器(backside illuminatedsensor),这种传感器可以接触到光电二极管的背面,而不会受到布线的阻碍。他解释说,这提高了传感器的灵敏度。Lindner还看到3D NAND闪存正在采用混合键合。

混合键合的挑战

那么,怎样才能加快混合键合的应用并实现大批量生产呢?

AMD的Fuselier说,“混合键合的神奇之处真的在于它所能带来的密度”,这为芯片设计者提供了更多选择。

“作为一个架构师,我们需要弄清楚如何最好地利用这种密度来应对我们面临的一些挑战,无论是logic to logic,还是interconnect logic to memory。”Fuselier解释说,还需要出现更多的创新。为此,“我们需要开发工具集来推动这种互连。”

他说,虽然晶圆厂有很多工具,但封装方面的工具集不足以让芯片设计者决定是否使用混合键合。

Intel的Sabi从制造角度阐述了混合键合的问题。

他指出,晶圆厂和封装供应商之间的更紧密合作至关重要。像混合键合这样的技术“真的打破了两者之间的界限”。在众多挑战中,他指出,互连的密度是巨大的。“我们需要极端的粒子控制能力,才能使CMP工艺保持原状”,这是在整个晶圆上实现这种机制所必需的。

根据Intel的说法,围绕混合键合的许多挑战可归结为计量工具。Sabi说,“我们强调计量工具。因为我们必须要找到问题,这样才能解决它们。”

考虑到混合键合模糊了传统的前端处理和后端装配测试之间的界限,像Qualcomm这样的fabless巨头需要什么呢?

Chidambaram指出,这一切都与系统级集成有关。在讨论公司内部的系统集成时,他说,“负责CPU的人和其他开发射频的人对彼此的领域了解不深。”为了实现不同领域的“协同优化”,“我们需要工具,以及人们可以在这些不同领域之间使用的语言。”

Chidambaram从三维层面详细介绍了混合集成,他说,“你说的是创造一种后端类型的集成。要做到这一点,你需要所有的物理学来解决问题,同时还需要解决多个芯片的电气行为。你把一个模块从顶部移动到底部,它会改变你的热行为、改变你的机械行为,你需要同时优化所有这些东西。”

阻碍chiplet发展的最大问题是工具集。现有的各种工具,可以分别解决一些特定的问题。但这个行业需要投资并开发能够从三维角度解决异构集成问题的工具。

审核编辑:刘清

-

传感器

+关注

关注

2574文章

54389浏览量

786168 -

电源管理

+关注

关注

117文章

6549浏览量

147542 -

SoC芯片

+关注

关注

2文章

662浏览量

36838 -

CMP

+关注

关注

7文章

160浏览量

27586 -

chiplet

+关注

关注

6文章

482浏览量

13504

原文标题:AMD、Intel与Qualcomm如何思考chiplet?

文章出处:【微信号:Astroys,微信公众号:Astroys】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

解构Chiplet,区分炒作与现实

Windows11上未检测到FX3设备是什么原因导致的?

从技术封锁到自主创新:Chiplet封装的破局之路

Chiplet与先进封装设计中EDA工具面临的挑战

Qualcomm QCS8250芯片的全面解析

奇异摩尔受邀出席第三届HiPi Chiplet论坛

Chiplet:芯片良率与可靠性的新保障!

2.5D集成电路的Chiplet布局设计

Intel为什么在2015年收购Altera?现在又为什么抛弃Altera

CES 2025:AMD锐龙9000新品亮相,表现超Intel旗舰

解锁Chiplet潜力:封装技术是关键

Chiplet技术革命:解锁半导体行业的未来之门

AMD、Intel与Qualcomm如何思考chiplet?

AMD、Intel与Qualcomm如何思考chiplet?

评论