RISC-V公测平台Stream程序路径:/public/benchmark/stream/5.10

前言

"Stream" 是一种基准测试工具,用于评估计算机系统的内存带宽性能。它通过模拟内存访问模式,测试系统在读取和写入连续内存块时的速度,衡量系统的内存性能和数据传输效率。

平台环境

| [硬件参数] | |

| 处理器: | 算能SG2042 X1 |

| DDR | 128G,3200HZ |

| [芯片参数] | |

| 主频 | 2.0GHz |

| 核心数: | 64核 |

| L1 Cache: | I:64KB and D:64KB(Per Core) |

| L2 Cache: | 1MB/Cluster(Per Cluster,X16 Cluster) |

| L3 Cache: | 64MB System Cache |

| [软件环境] | |

| linux版本: | Ubuntu 22.10 |

| gcc版本: | 12.2.0(GNU) |

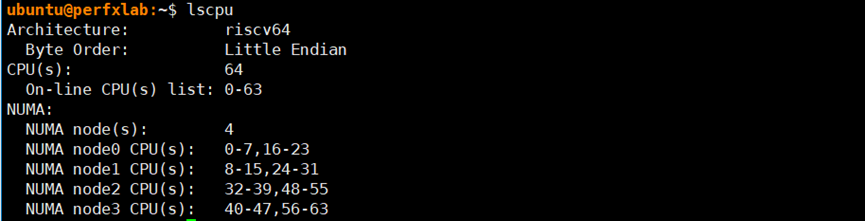

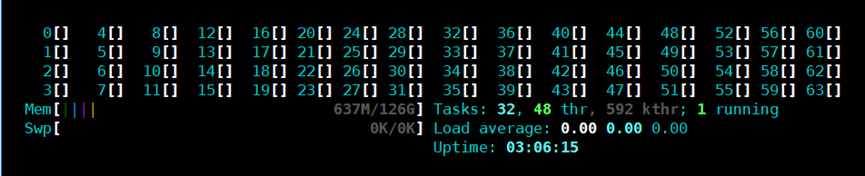

cpu 信息

cpu 信息 64核示意

64核示意

参数含义

我们先来了解下测试参数的具体用法。

1. ARRAY_SIZE:

用于指定测试期间使用的数组大小。该参数定义了测试中要操作的内存块的大小,通常以字节为单位。通过更改 array_size 的值,可以评估系统在不同内存工作负载下的性能表现,关于设置的大小,我们可以从官网上查看到说明:

The general rule for STREAM is that each array must be at least 4x the size of the sum of all the last-level caches used in the run.

Useful links:

也就是我们需要设置为最后一级缓存总和的 4 倍。

2. OpenMP :

-gcc编译器添加“-fopenmp” 选项多线程支持。

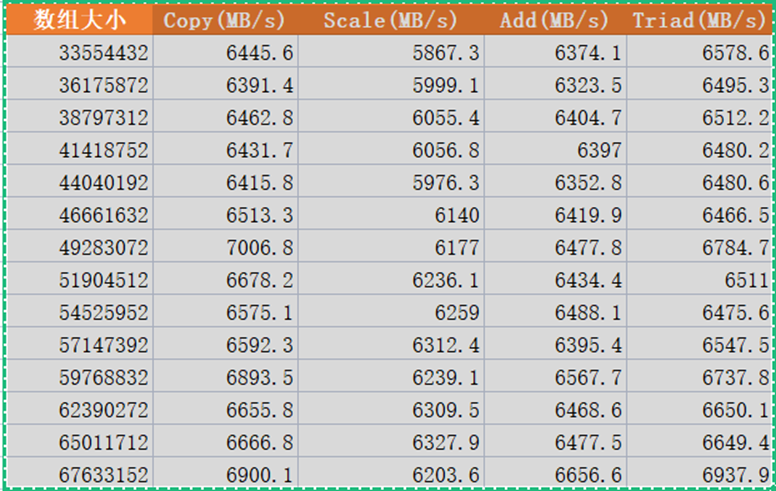

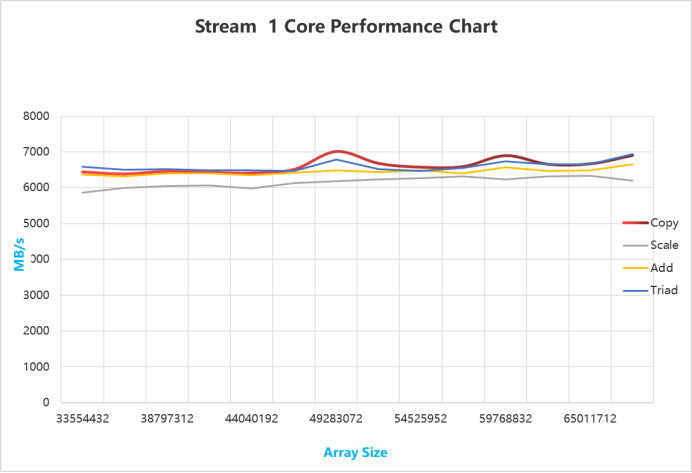

单线程Stream测试

我们的L3 Cache大小是64M,参考官方文档的建议,为了测试的准确性,选取了4倍大小的数据,也就是数组大小33554432作为基准,以2621440为梯度,依次增加数组大小,考察数组大小对测试结果的影响。选用的是gcc编译器。

单线程测试命令:

ubuntu@perfxlab:~/STREAM$ gcc -O3 -DSTREAM_ARRAY_SIZE=【ARRAY_SIZE】 stream.c

测试结果如下表:

单线程 gcc -o3

单线程 gcc -o3

多线程Stream测试

和单线程Stream测试一样,同样可以做不同数组大小的多线程Stream 测试,选取的数组大小和单线程一样。

ubuntu@perfxlab:~/STREAM$ gcc -O3 -fopenmp -DSTREAM_ARRAY_SIZE=【ARRAY_SIZE】 stream.c

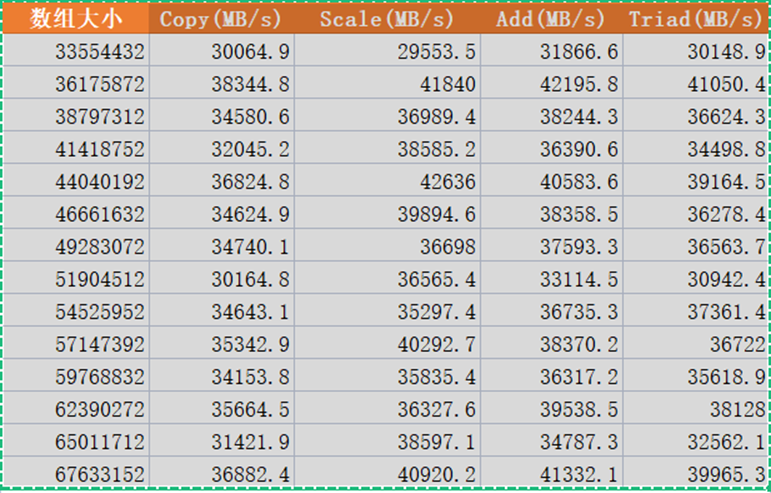

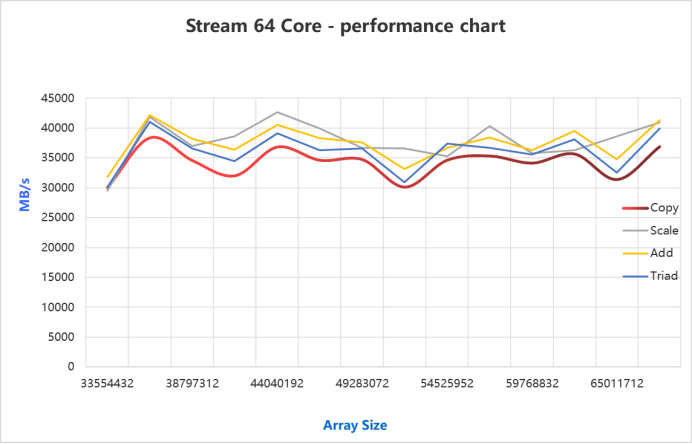

测试结果如下表:

多线程 gcc -o3

多线程 gcc -o3

结论

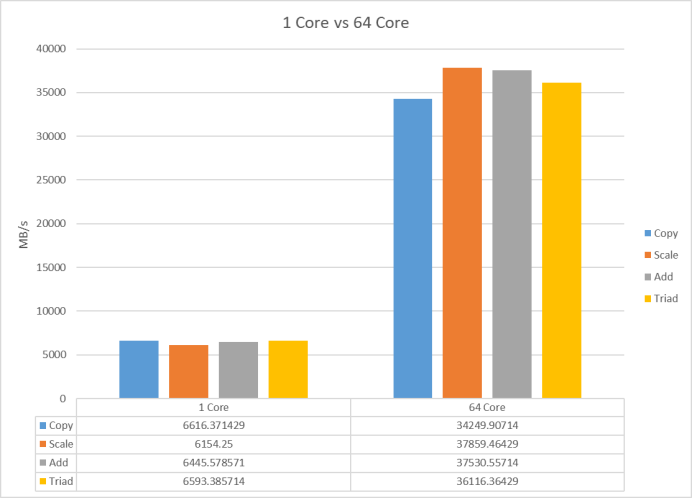

单核vs多核 gcc -o3

单核vs多核 gcc -o3

从结果可以看出,多核测试的结果明显高于单核测试的结果。多核测试利用了多个处理核心并行执行任务,从而表现出更大的数据带宽。在多核测试中,Copy操作的性能是单核测试的大约5倍,Scale操作的性能约为单核测试的6倍。

综上所述,多核测试在Copy和Scale操作中显示出了明显的性能优势,而在Add和Triad操作中的性能提升较小。这与多核处理器的并行处理能力和数据依赖性有关。多核测试结果显示出了多核处理器在并行计算和数据处理方面的优势。

-

带宽

+关注

关注

3文章

1029浏览量

43025 -

计算机

+关注

关注

19文章

7764浏览量

92681 -

Stream

+关注

关注

0文章

21浏览量

8218 -

RISC-V

+关注

关注

48文章

2792浏览量

51903

发布评论请先 登录

RISC-V公测平台发布 · 数据库在RISC-V服务器上的适配评估

RISC-V公测平台发布 · Stream带宽完整测试

RISC-V公测平台发布 · Stream带宽完整测试

评论