USB的众多便利使设计师能将该总线用于许多应用。例如,一个利用现成的便宜器件搭建的基于USB的4步进电机控制器。该电路采用MCU和DSP。它利用简单逻辑电路和应用软件控制步进电机的选择、其顺/逆时针的运行方向以及三种步进幅度:全步、半步和微步。

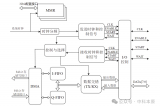

该设计基于一个USB转FIFO的并行接口模块(IC1)。这款名为DLP-USB245M的模块提供8位双向数据总线和诸如WR、RD、RXF和TXE等控制信号,利用这些信号控制PC和任何采用USB协议的外接电路的数据流。

利用该模块免去了需应付繁琐的USB接口的工作。另外,该模块带可通过高级语言容易快速地控制模块功能的驱动器软件,从而无需太多牵挂USB协议。

该控制器电路的其余部分包括诸如8D触发器(74LS273)、反向器(7416)和3/8译码器以及达林顿阵列驱动器(ULN2003)等通用数字器件。USB转FIFO模块采用外接5V供电,5V接至脚3、10和11。

其工作过程如下:当PC不向USB转FIFO模块发送数据时,IC1的发送缓存器为空,且RXF保持逻辑1。这使得D触发器(IC2)的RD和CLK为逻辑0,所以,IC2的输出保持不变。但,若PC向USB转FIFO模块接收缓存器发送一个字节,则RXF被拉低,自动指示最少有1字节数据可用。

经过短暂延时后,它将RD和CLK信号置1,且发送缓存器的数据字节输出(出现在D0-D7)在IC2的输出被锁存。一旦数据传输完成且如果发送缓存器为空,RXF返回逻辑1。这意味着没更多数据可用。此举,又将RD置为逻辑0,以便能进一步传输数据。

锁存数据低4位(IC2的Q0-Q3)驱动其它4个8D触发器(74LS273),而Q4和Q5控制3/8译码器(IC3)。在反向后,译码器的输出(A‘、B’、C‘、D’)作为IC4-IC7的时钟。达林顿阵列驱动器(IC8-IC11)放大IC4-IC7的输出,以便它们可驱动步进电机线圈。这样,通过向IC1写入一个正确字节,PC可选择4个步进电机之一并如愿驱动其电机线圈。

例如,当PC向USB转FIFO模块发送数据0x0A时,步进电机1被选且其线圈以L1 L2 L3 L4 = 1 0 1 0的模式得电。为使步进电机1前转一步,PC发送的下一个字节是0x09;若想使其反转,PC发送0x06。

表中列出的是控制4个步进电机以全步运行的字节值。通过适当变化,用户可以半步和微步操控电机。数据字节写入的速率――也即,连续数据的写入间隔――控制步进电机的速度。

除电流放大器和USB-FIFO转换器外,分立器件可用CPLD/FPGA实现。可以多种方式开发电机控制软件。你可采用C或VB或类似LabVIEW等图形程序。若采用与IC1一道提供的VCP(虚拟COM端口)驱动器软件(免费下载),应用程序将视USB步进电机控制器模块为另一个COM口。但,设置波特率的指令将被忽略且数据将以最快的速度被发送(而不管应用的波特率设置)。你还可采用Windows提供的D2XX直接驱动器,这样,你就可直接控制各项操作,比如“FIFO_写”等。

为对电路功能进行基本测试,你既可利用提供的DLPTEST应用软件或简单借助诸如Hyperterminal等串口程序来不断发送所需字节。在此展示的设计采用12和5V外接电源。所以,你必须留意,当关闭PC或USB集线器(若使用)时,USB总线内的电流也被关断。

责任编辑:彭菁

-

mcu

+关注

关注

147文章

18605浏览量

387047 -

usb

+关注

关注

60文章

8372浏览量

281695 -

触发器

+关注

关注

14文章

2050浏览量

63043 -

接口模块

+关注

关注

0文章

29浏览量

11184 -

反向器

+关注

关注

2文章

24浏览量

11895

发布评论请先 登录

Texas Instruments USB-TO-GPIO2接口适配器技术解析

如何设计具有并行接口的数字输入模块

L-com诺通推出新型工业级USB 3.0转接头

USB转串口模组选购指南:2025主流通信转换设备品牌盘点与应用方案解析

USB协议转换器:USB转TTL/232/485,光电隔离

CYUSB3014从机FIFO接口图显示支持DQ[31:0],但表格仅表明支持DQ[15:0],哪一个是正确的?

UCD9222 具有 4/6/8 位并行 VID 的双相数字 PWM 降压控制器数据手册

如何使用FPGA驱动并行ADC和DAC芯片,使用不同编码方式的ADC与DAC时的注意事项

SDRAM控制器的设计——Sdram_Control.v代码解析(异步FIFO读写模块、读写SDRAM过程)

DSP通用并行端口uPP技术详解

上新 | 超全模块超乎想象,YU系列USB&amp;Type-C多模块工业级连接器新品惊喜上市

基于一个USB转FIFO的并行接口模块设计

基于一个USB转FIFO的并行接口模块设计

评论