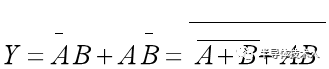

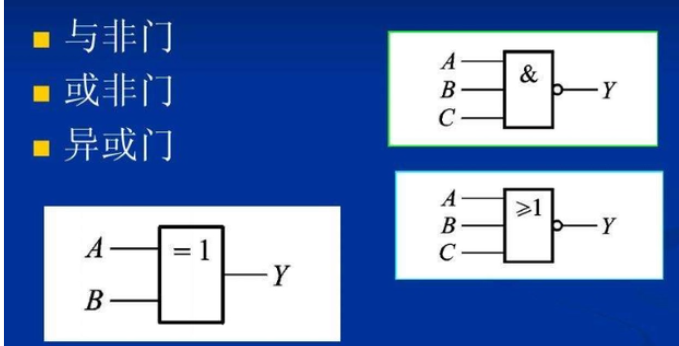

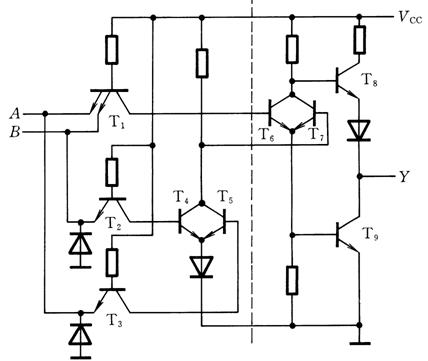

异或门 (简称XOR gate)是数字逻辑中实现逻辑异或的逻辑门。有多个输入端、一个输出端,多输入异或门可由两输入异或门构成。若两个输入的电平相异,则输出为高电平1;若两个输入的电平相同,则输出为低电平0。即如果两个输入不同,则异或门输出高电平1。

虽然异或不是开关代数的基本运算之一,但是在实际运用中相当普遍地使用分立的异或门。大多数开关技术不能直接实现异或功能,而是使用多个门组合设计。

##############################################

##############################################

随着超大规模集成电路的复杂程度不断提高,电路制造后的测试所需的时间和经济成本也不断增加。电路在设计时向电路添加一些特殊的结构(例如扫描链和内建自测试),能够大大方便之后的电路测试。这样的设计被即为可测试性设计,它们使电路更加复杂,但是却能凭借更简捷的测试降低整个项目的成本。

随着超大规模集成电路的集成度不断提高,同时市场竞争压力的不断增加,集成电路设计逐渐引入了可重用设计方法学。可重用设计方法学的主要意义在于,提供IP核(知识产权核)的供应商可以将一些已经预先完成的设计以商品的形式提供给设计方,后者可以将IP核作为一个完整的模块在自己的设计项目中使用。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

CMOS

+关注

关注

58文章

6233浏览量

243407 -

高电平

+关注

关注

6文章

225浏览量

22882

发布评论请先 登录

相关推荐

热点推荐

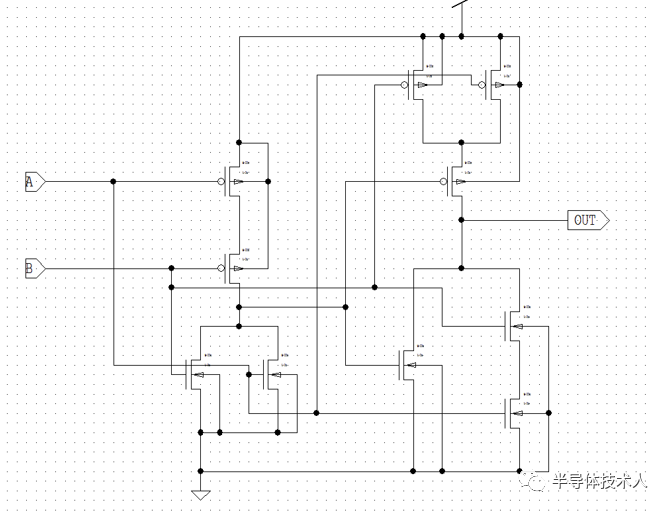

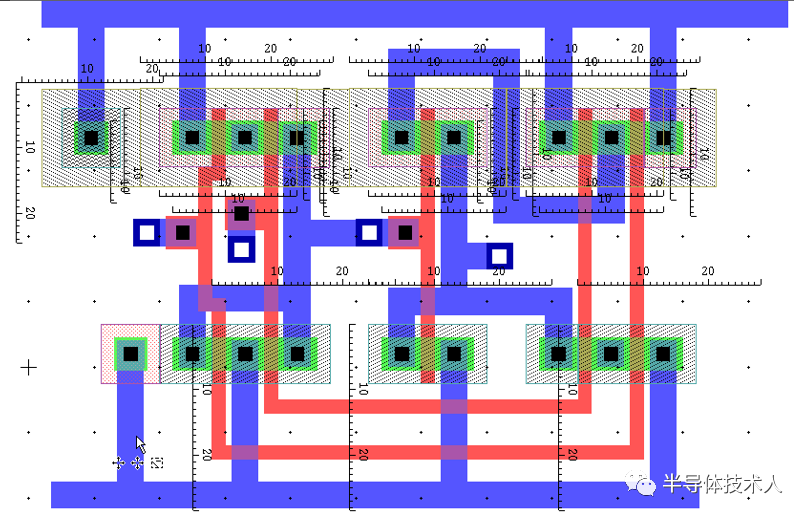

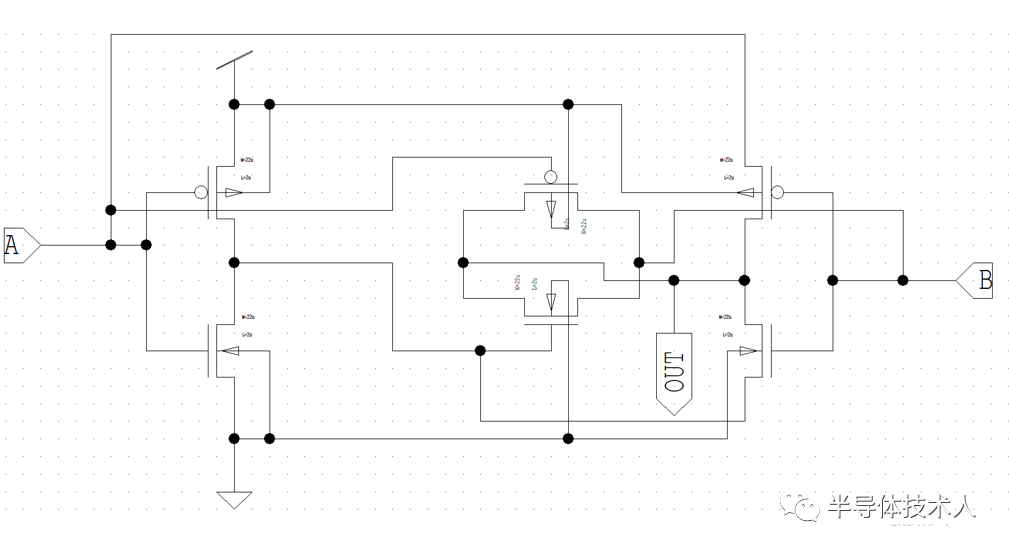

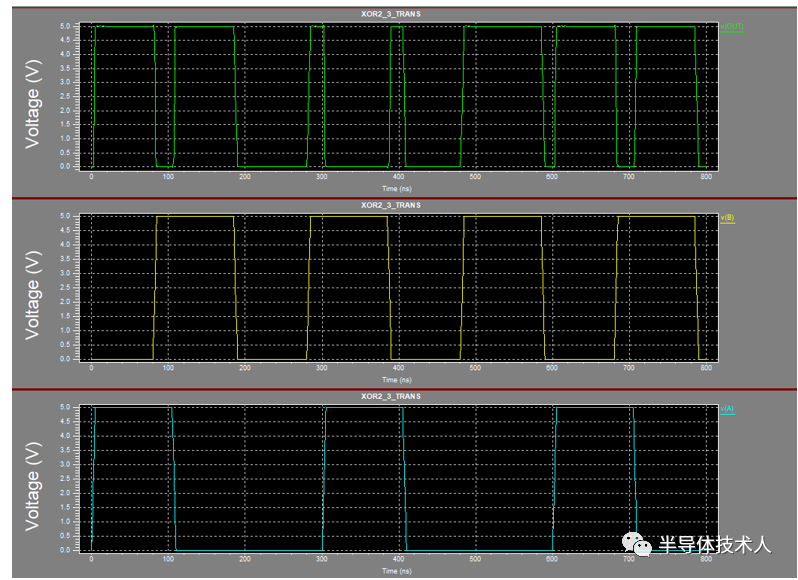

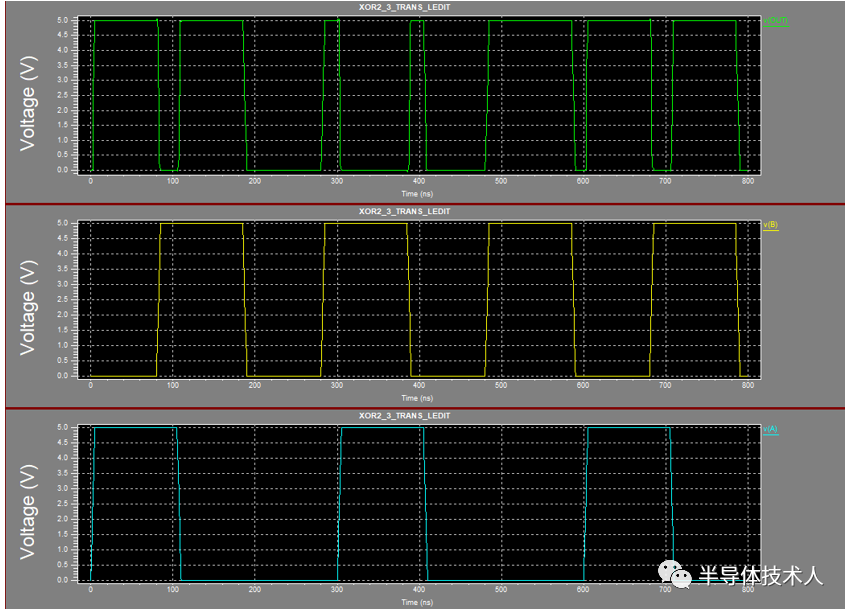

CMOS异或门的设计方法及技巧

CMOS电路因其在在功耗、抗干扰能力方面具有不可替代的优势,以及在设计及制造方面具有简单易集成的优点而得到广泛应用。如今,在大规模、超大规模集成电路特别是数字电路中早已普遍采用CMOS工艺来来进行

【数字电路】关于逻辑异或门基础知识点总结教程

二进制数据,而另一输入提供有控制信号。常用的数字逻辑异或门IC包括:TTL逻辑异或门74LS86四路2输入CMOS逻辑异或门CD4030四路2输入7486四路2输入

发表于 01-23 08:00

异或门,异或门是什么意思

异或门,异或门是什么意思

异或门电路即,有2个输入端、1个输出端。当2个输入端中只有一个是高电平时,输出则为高电平;当输入端都是低电平或

发表于 03-08 12:10

•1.6w次阅读

异或门的逻辑功能解析

异或门 (英语:Exclusive-OR gate,简称XOR gate,又称EOR gate、ExOR gate)是数字逻辑中实现逻辑异或的逻辑门。有多个输入端、1个输出端,多输入异或门可由2输入

发表于 11-19 17:59

•7.4w次阅读

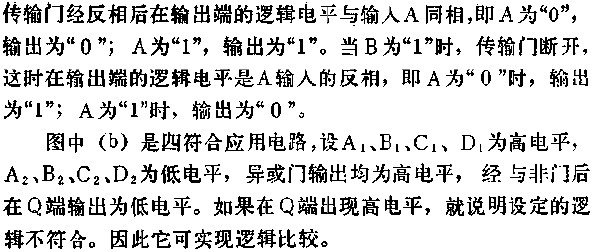

为什么异或门又称可控反相器

为什么异或门又称可控反相器 异或门是一种常见的逻辑门,其中包含两个输入管脚和一个输出管脚。在逻辑运算中,异或门的输出值与两个输入值的逻辑值不同,称为“异或”,也被称为“可控反相器”。 在数

异或门两种常见的实现方式

这两种实现方式都能够实现异或门的功能,具体的选择取决于设计需求和逻辑门的可用性。实际构建异或门时,可以使用离散电子元件(如晶体管、二极管等)或整合电路芯片(如 TTL、CMOS 等)来实现。

低功耗,1.8/2.5/3.3-V输入,3.3-V CMOS输出,2输入 异或门数据表

电子发烧友网站提供《低功耗,1.8/2.5/3.3-V输入,3.3-V CMOS输出,2输入 异或门数据表.pdf》资料免费下载

发表于 05-09 10:37

•0次下载

低功率,1.8/2.5/3.3-V输入,3.3-V CMOS输出,2输入异或门数据表

电子发烧友网站提供《低功率,1.8/2.5/3.3-V输入,3.3-V CMOS输出,2输入异或门数据表.pdf》资料免费下载

发表于 05-09 10:36

•0次下载

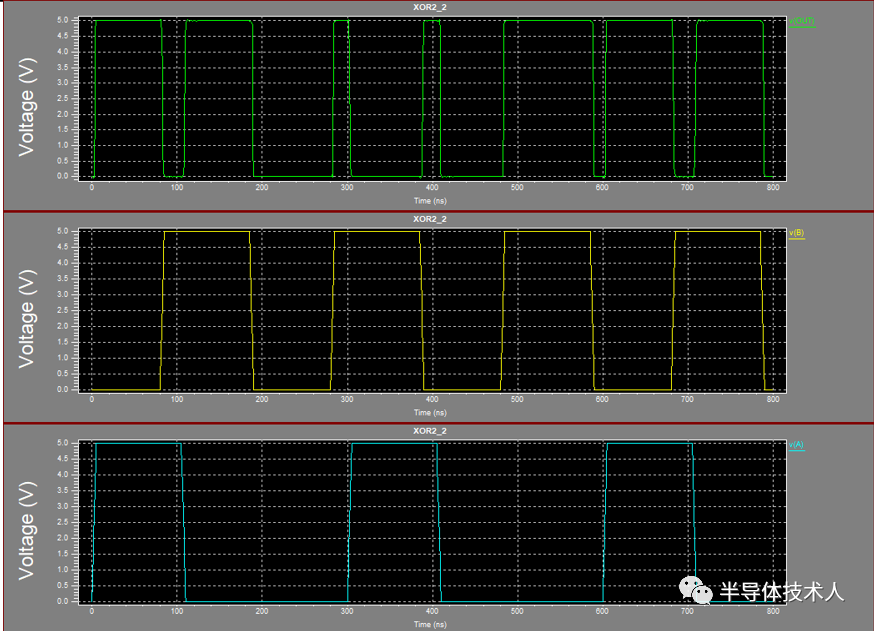

CMOS异或门仿真设计

CMOS异或门仿真设计

评论