本文主要介绍串扰的概念,及其FEXT、NEXT等,以及串扰的消除措施。

串扰串扰是指当信号在传输线上传播时,因电磁耦合对相邻的传输线产生的不期望的电压噪声干扰。这种干扰是由于两条信号线间的耦合,即信号线之间互感和互容耦合引起的。容性耦合(当干扰源产生的干扰是以电压形式出现时,干扰源与信号电路之间就存在容性(电场)耦合,这时干扰电压线电容耦合到信号电路,形成干扰源)引发耦合电流,而感性耦合(当干扰源是以电流形式出现的,此电流所产生的磁场通过互感耦合对邻近信号形成干扰)则产生耦合电压。由于自身的逻辑电平发生变化,对其他信号产生影响的信号线称为“攻击线”(Aggressor),即干扰线。受到影响而导致自身逻辑电平发生异常的信号连线我们称为“受害线”(Victim),即被干扰线。串扰噪声从干扰对象上通过交叉耦合到被干扰对象上,表现为在一根信号线上有信号通过时,在PCB板上与之相邻的信号线上就会感应出相关的信号。

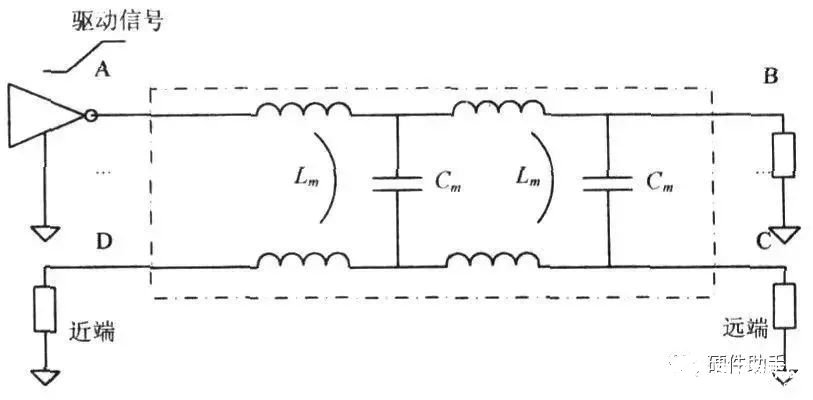

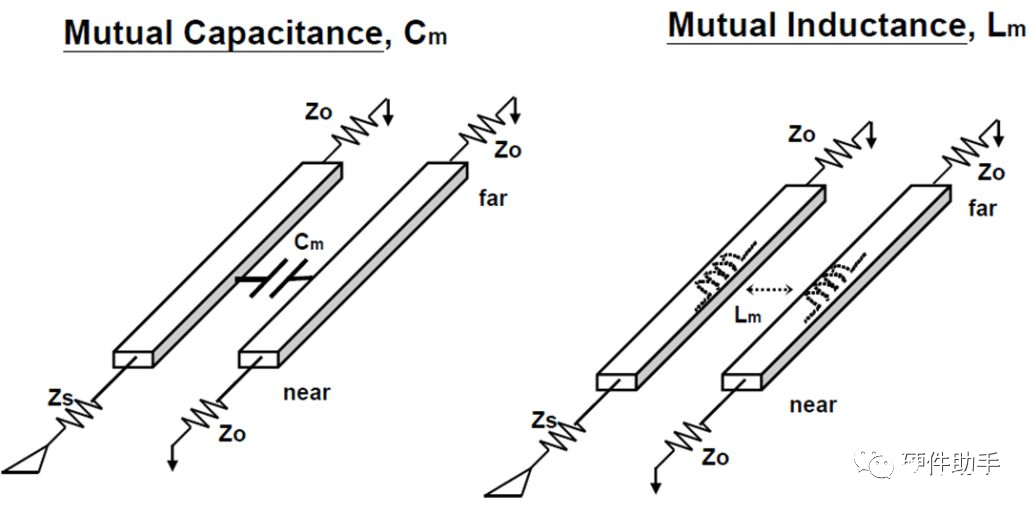

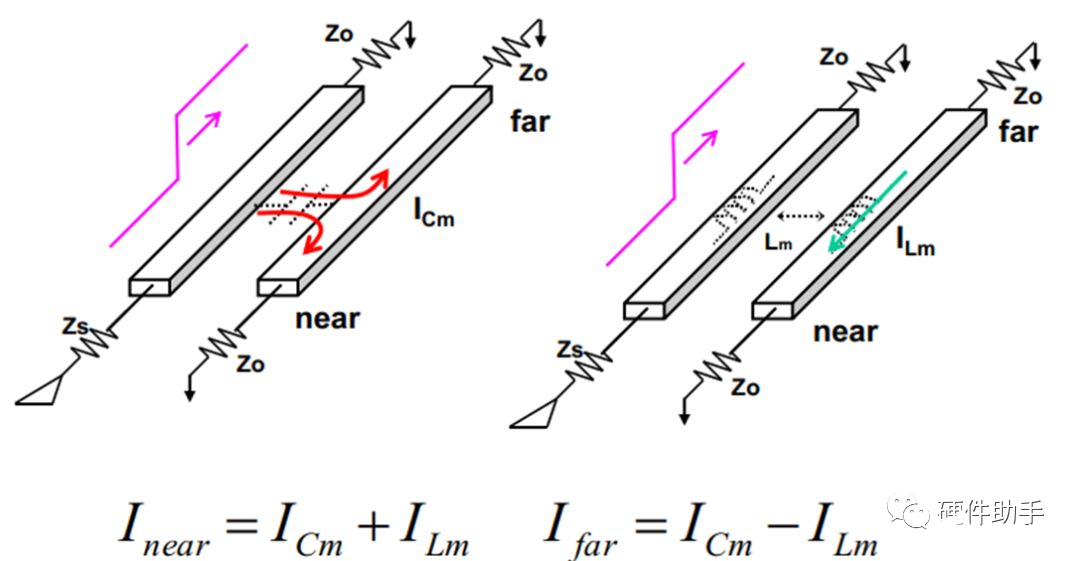

串扰由一条线到另一条线的能量耦合的方式主要分为电场(electric field)和磁场(magnetic field)。由于走线之间存在着互容(Mutual capacitance)和互感(Mutual inductance),一条走线上的AC信号便会从这些分布的互容和互感传递到另一根被干扰线(victim net)上。串扰可分为容性耦合串扰和感性耦合串扰两类。

静态网络靠近干扰源一端的串扰称为近端串扰(也称后向串扰NEXT),而远离干扰源一端的串扰称为远端串扰(或称前向串扰FEXT)。

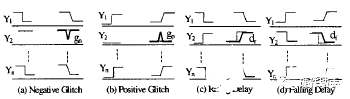

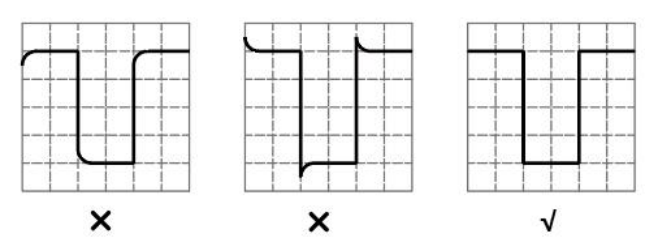

当干扰源状态变化时,会在被干扰对象上产生一串扰脉冲,在高速系统中,这种现象很普遍。通常,依赖于干扰源和被干扰源上信号的跳变,被干扰线上产生四种类型的影响:正的短时脉冲,负的短时脉冲,上升时延,下降时延,如下图所示:

串扰的来源当信号沿着传输线传播时,在信号路径与返回路径之间存在电场和磁场。这些场的分布不仅仅限于信号和返回路径之间的空间内,而是在周围空间延伸。我们把这些延伸出去的场称为边缘场。

如果将两导线的间距加大,可看到边缘场的强度大大减弱。

第2根线处在边缘场的附近时,就有过多的耦合和串扰。归根结底,边缘场是引起串扰的根本原因。减小串扰最重要的方法就是使网络间的间距足够远,使其边缘场降低到可以接受的范围。

在系统中的每两个网络之间,总会有边缘场产生的电感耦合和电容耦合。我们把耦合电感和耦合电容分别叫做互感和互容。

串扰的消除解决容性串扰,主要加大线间距,在PCB上的布线要遵循3W原则,即两个传输线的线中心之间的距离要大于3倍的传输线的线宽。对系统中关键传输线,可以改用差分线传输以减少其它传输线对它的串扰;也可以对关键线的中间加地线保护以减少串扰。

解决感性串扰,主要减小回路面积,减小互感。例如,在芯片的电源的去耦电容,通过电容提供回流通道,可以减少回路面积,减小互感。

尽可能地减少相邻传输线间的平行距离(累积的平行距离),最好在不同层间走线,相邻两层的信号层(中间没有平面层隔离)走线方向应该相互正交,以减少层间的串扰。

在保证传输线特征阻抗的同时,使布线层与参考平面(电源平面或地平面)间的介质层尽可能的薄,这样就加大了传输线与参考平面间的耦合度,从而减少相邻传输线间的耦合。

在保证信号时序的情况下,尽可能选择转换速度低的元器件,这样电场与磁场的变化速度慢一点,从而降低串扰。由于信号上升时间是造成SI 问题的主要原因,所以在满足系统设计指标的情况下,应该尽可能选取信号上升沿较慢的器件。

可能的话,尽量少在表层走线,走带状线或嵌入式微带线,因为表层线的电场耦合比中间层的要强(表层线只有一个参考平面),内层走线可以消除传播速度的变化。

责任编辑:haq

-

电源

+关注

关注

185文章

18976浏览量

264441 -

电容

+关注

关注

100文章

6518浏览量

160024 -

电压

+关注

关注

45文章

5789浏览量

122361 -

网络

+关注

关注

14文章

8330浏览量

95550

发布评论请先 登录

IDT信号完整性产品:解决高速信号传输难题

普源DHO5000系列数字示波器信号完整性分析

信号完整性(SI)/ 电源完整性(PI)工程师的核心技能树体系

了解信号完整性的基本原理

高频晶振的信号完整性挑战:如何抑制EMI与串扰

Samtec虎家大咖说 | 浅谈信号完整性以及电源完整性

受控阻抗布线技术确保信号完整性

信号完整性测试基础知识

信号完整性系列之“串扰”

信号完整性系列之“串扰”

评论