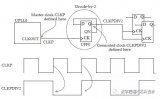

今天我们要介绍的基本sdc是 时序特例 ,也就是我们常说的Path exception。针对一些路径需要的一些特殊设定,常用的有set_false_path, set_multicycle_path, set_max_delay,set_min_delay等

set_false_path : false path是指在正常工作环境下,并不真实存在或者经过的路径,比如说一些静态输入信号产生的path。像这样的path,我们可以指定set_false_path。这样工具在计算timing时就不会去分析它。值得注意的是,设定false path时一定要非常小心,一定要和designer仔细确认下,不要把正常的path给误伤掉。

例: set_false_path-from ff1/CK -through {u1/Y} -to ff2/D

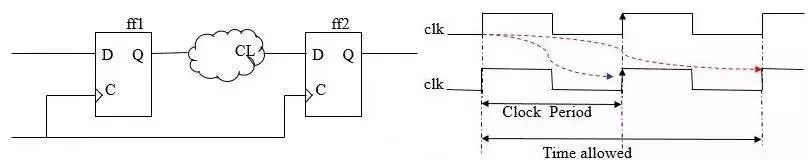

set_multicycle_path : 指的是两个寄存器之间数据要经过多个时钟才能稳定的路径,一般出现于组合逻辑较大的那些路径,也有可能是一些慢时钟去踩快时钟的路径。对于这些路径,我们可以设置multicycle path。同样的,设置multicycle path时,也需要非常谨慎,需要和前端沟通好,该条path要设几个cycle, -start还是-end也要理解清楚,而且默认的hold的multicycle比setup少一个。

例:

set_multicycle_path 2 -setup -from ff1/CP -to ff2/D

set_multicycle_path 1 -hold -from ff1/CP -to ff2/D

set_max_delay: 指定某段path的最大延迟,超过就是violation。用于某些特定的path,限定该path只能走这么长delay.

例:set_max_delay 8.0 -from {ff1/CP} -to {ff2/D}

set_min_delay: 指定某段path的最小延迟,小于该值就是violation。用于某些特定的path,限定该path至少应该走这么长delay.

例:set_min_delay 4.0 -from {ff1/CP} -to {ff2/D}

-

寄存器

+关注

关注

31文章

5619浏览量

130422 -

SDC

+关注

关注

0文章

50浏览量

16333 -

时序分析器

+关注

关注

0文章

24浏览量

5501

发布评论请先 登录

VIVADO时序约束及STA基础

时序约束 专版

介绍系统接口sdc

时序分析基本概念—SDC概述

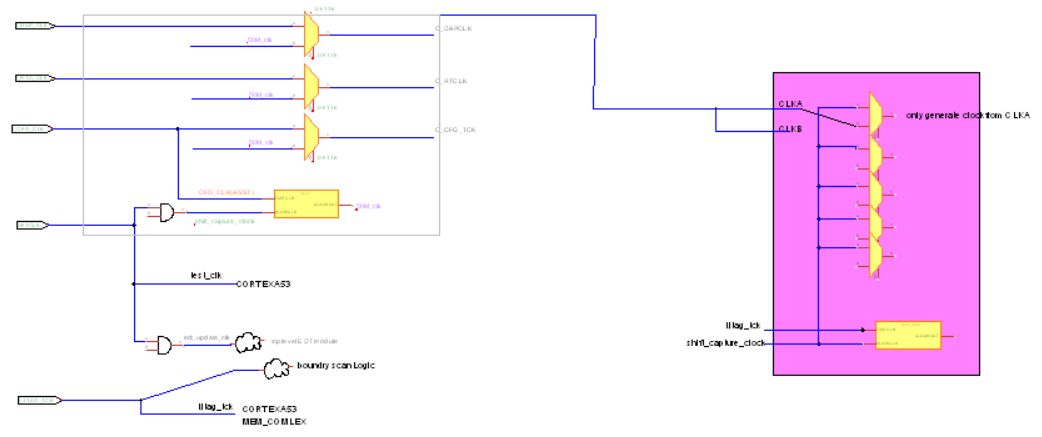

时序分析基本概念介绍<generate clock>

介绍基本的sdc时序特例

介绍基本的sdc时序特例

评论