什么是半加法器?

半加法器是一种执行二进制数相加的数字电路。它是最简单的数字加法器,您只需使用两个逻辑门即可构建一个;一个异或门和一个 AND 门。

半加法器只能添加两个 1 位数字。半加法器和全加法器之间的区别在于,第一个加法器没有进位输入。

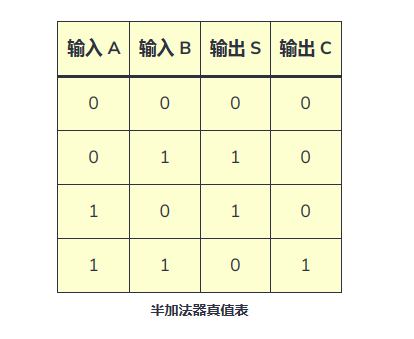

1 位二进制加法的所有可能组合如下所示:

您需要两个位来表示结果,因为将两个 1 位数字相加的最高可能结果是 2(二进制中的“10”)。

您可以使用前面给出的 1 位二进制加法的四种可能组合将其添加到真值表中。加法器接受两个输入,A 和 B,并生成两个输出,一个用于总和

(S),另一个用于进位 (C)。所以真值表变成:

半加法器如何工作?

要了解如何创建半加法器电路,您可以使用其真值表。您需要做的第一件事是分离 S 输出并构建自己的真值表。

如果您知道逻辑门,您可能会注意到这看起来与异或门的真值表完全相同。你是对的。

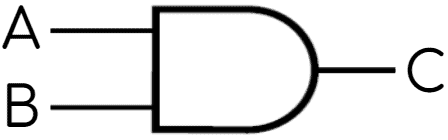

接下来,是时候关注 C 输出了:

如果你仔细检查它,你会发现它的行为与 AND 门相同,因为它只在两个输入都是一个时返回一个。这意味着要创建 C 输出,您可以使用 AND 门:

最后,您可以组合用于产生S和C输出的电路,以构建完整的半加器电路图:

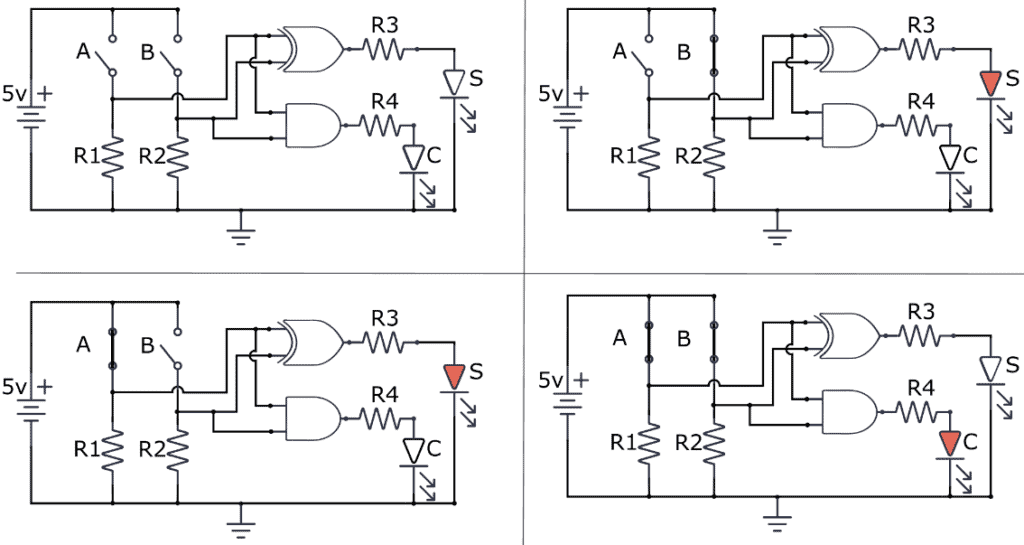

半加法器模拟

为了演示此加法器电路的工作原理,您将在下面找到一个模拟。简单的开关代表 A 和 B 输入。S 和 C 输出由 LED 表示,其中亮起的 LED

表示“1”,未亮起的 LED 表示“0”。

-

加法器

+关注

关注

6文章

183浏览量

31562 -

数字电路

+关注

关注

193文章

1668浏览量

83548 -

二进制数

+关注

关注

0文章

12浏览量

7947

发布评论请先 登录

十进制加法器,十进制加法器工作原理是什么?

同相加法器电路原理与同相加法器计算

同相加法器电路图_反相加法器电路图_运放加法器电路图解析

加法器原理

加法器工作原理_加法器逻辑电路图

半加法器的工作原理及电路解析

半加法器的工作原理及电路解析

评论