什么是全加法器?

加法器可以是半加法器或全加法器。不同之处在于半加法器仅用于将两个 1 位二进制数相加,因此其总和只能从 0 到 2。为了提高这种性能,开发了FullAdder。它能够添加三个 1 位二进制数,实现从 0 到 3 的总和范围,可以用两个输出位 (“11”) 表示。

如果按照上面的真值表,A 和 B 表示要添加的输入变量,而 C在是进位输入。S

是总和输出,C外是指示是否发生了进位的输出。但是在二进制逻辑中,进位是什么意思?好吧,让我们看看下一个示例:

请注意,当您添加“0”和“0”或“1”和“0”时,结果可以用一位表示,但是当您添加“1”和“1”时,您需要两个位,其中一个是进位。

但是,为什么在全加法器中需要进位输入呢?好吧,当您想对超过 1 位数字的输入求和时,例如添加两个 4位二进制数,您需要组合多个加法器并在它们之间提供进位输入,以表示之前不太重要的操作产生了进位。

完整的加法器电路

可以使用两个半加法器电路和一个OR门来构建全加法器。前半加法器有两个 1 位二进制输入,分别是 A 和 B。它产生两个输出;求和和结转。

第一个半加法器的 Sum 输出将是第二个半加法器的第一个输入。第一个半加法器的进位输出将是附加OR门的第二个输入。

第二个半加法器的第二个输入变为进位输入 (C在) 的全加法器。

第二个半加法器还将提供求和和进位输出。其 Sum 输出表示 Full Adder 的 Sum 输出 (S),其 Carry 输出是附加 OR门的第一个输入。最后,OR门将生成进位输出(C外) 的全加法器。

让我们用实际电路替换块:

全加器的应用:4位二进制加法器

假设您要添加以下两个 4 位二进制数 A 和 B:

A = 1111 B = 1111

结果将是一个 5 位数字:

11110

其中,最高有效位表示进位。

因此,为了如上所述添加两个 4 位二进制数,您需要组合四个完整加法器,如下所示:

如您所见,每个加法器的输入 A 和 B 包含两个 4位二进制数的元素,从右到左从其不太重要的位分布。另外,观察一个完整加法器的进位输出如何成为下一个加法器的进位输入。请记住,这是要考虑到之前不太重要的操作是否产生了携带。

查看可以添加两个 4008 位二进制数的 CMOS CD4 芯片。

-

电路

+关注

关注

173文章

6063浏览量

177479 -

加法器

+关注

关注

6文章

183浏览量

31236

发布评论请先 登录

十进制加法器,十进制加法器工作原理是什么?

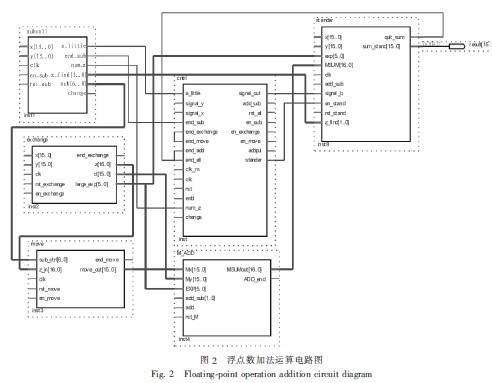

FPU加法器的设计与实现

同相加法器电路原理与同相加法器计算

加法器工作原理_加法器逻辑电路图

全加法器的工作原理和电路解析

全加法器的工作原理和电路解析

评论