芯片封装测试是在芯片制造过程的最后阶段完成的一项重要测试,它主要用于验证芯片的封装质量和功能可靠性。芯片封装测试包括以下主要方面:

1.外观检查:对封装好的芯片进行外观检查,包括观察是否有翘曲、变形、划伤或氧化等问题。

2.尺寸测量:通过使用专业的仪器测量芯片封装的尺寸,以确保其符合设计规格。

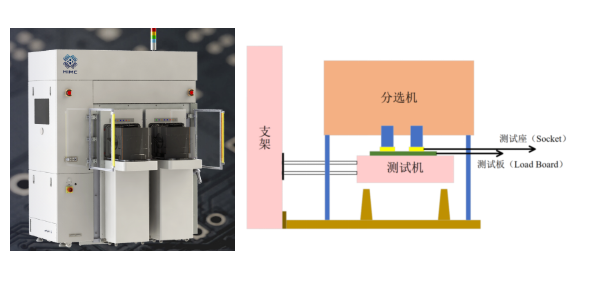

3.引脚连通性测试:通过针对芯片引脚进行连通性测试,检查是否有导通异常或短路等问题。

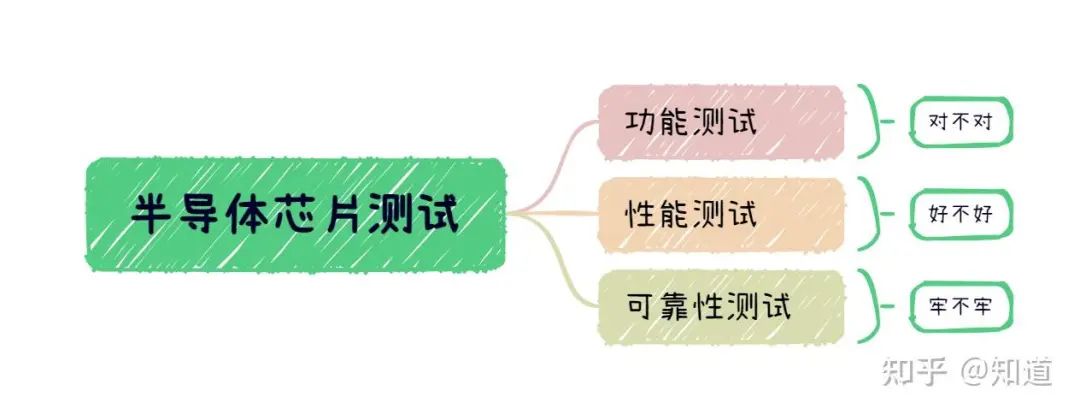

4.功能性测试:通过加载适当的测试程序,对芯片进行功能性测试,以验证其各项功能是否正常运作。

5.温度老化测试:将芯片暴露在高温环境下,持续一定时间进行老化测试,以评估芯片在极端工作条件下的性能和可靠性。

6.环境适应性测试:将芯片置于不同的温度、湿度和振动等环境条件下,进行测试,以验证芯片的稳定性和适应性。

7.可靠性测试:通过模拟芯片在长时间运行中可能遇到的各种异常情况,如电压波动、温度变化等进行测试,以评估芯片的可靠性和抗干扰能力。

以上是关于芯片封装测试的一些常见内容,不同类型的芯片和封装方式可能会有所不同。

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

封装测试

+关注

关注

9文章

161浏览量

24649 -

芯片封装

+关注

关注

14文章

619浏览量

32390

发布评论请先 登录

相关推荐

热点推荐

芯片烧录与芯片测试的关联性:为什么封装后必须进行IC测试?

烧录良率 97%、测试良率仅 82%,根源在于二者工序本质不同:烧录只验证程序写入是否成功,测试则校验芯片电气与功能是否合格。封装过程易引入微裂纹、ESD 损伤等问题,必须通过 FT

先进封装时代,芯片测试面临哪些新挑战?

摩尔定律放缓后,2.5D/3D 封装、Chiplet 成行业新方向,却给测试工程师带来巨大挑战。核心难题包括:3D 堆叠导致芯粒 I/O 端口物理不可达,需采用 IEEE 1838 标准等内置

芯片CP测试与FT测试的区别,半导体测试工程师必须知道

本文聚焦芯片CP 测试与FT 测试的核心区别,助力半导体测试工程师厘清二者差异。CP 测试是封装

当芯片变“系统”:先进封装如何重写测试与烧录规则

先进封装推动芯片向“片上系统”转变,重构测试与烧录规则。传统方案难适用于异构集成系统,面临互联互操作性、功耗管理、系统级烧录等挑战。解决方案需升级为系统验证思维,包括高密度互连检测、系

CoWoS产能狂飙的背后:异质集成芯片的“最终测试”新范式

烧录、封装后故障定位四大难题。解决方案包括设计 - 测试协同、多物理场仿真验证、多协议协同烧录、数据闭环智能诊断。CoWoS 大规模落地的关键,在于突破测试成本、标准及故障分析等瓶颈,

Keithley吉时利6517A静电计如何解决半导体封装测试难题

一、介绍静电计在半导体测试中的应用背景 1.1 半导体封装测试的重要性 在半导体产业链中,封装测试是至关重要的环节。它不仅能将制造好的

可靠性测试包括哪些测试和设备?

在当今竞争激烈的市场环境中,产品质量的可靠性成为了企业立足的根本。无论是电子产品、汽车零部件,还是智能家居设备,都需要经过严格的可靠性测试,以确保在各种复杂环境下都能稳定运行,为用户提供可靠的使用体验。那么,可靠性测试究竟包括哪

芯片封装测试包括哪些?

芯片封装测试包括哪些?

评论