驱动半导体工业发展的动力是什么?是人们对自然学习语言、人工智能、自动驾驶、视频监控、增强/虚拟现实、5G通信、个人医疗、可再生能源以及智能电网的需求。表面上看,这些需求五花八门,但透过现象看本质后,我们可以惊奇地发现他们存在许多共同点,比如数以亿计的计算能力、无线网络的扩展能力、高效的能源管理能力,以及多维感知的能力。而实现这些系统级能力的基础是关键器件的性能升级,比如处理器的堆核升频,网络的异质互联,以及感知层的提精降耗等等。

后摩尔时代,半导体产业面临变革

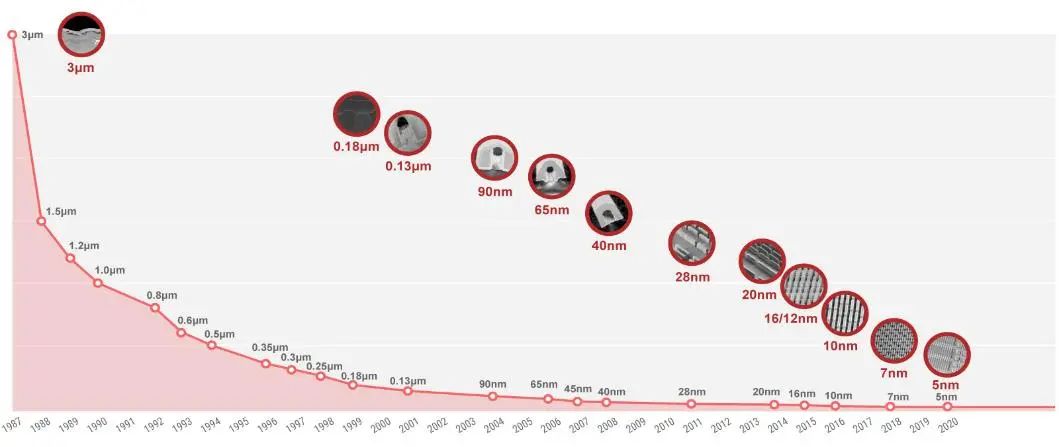

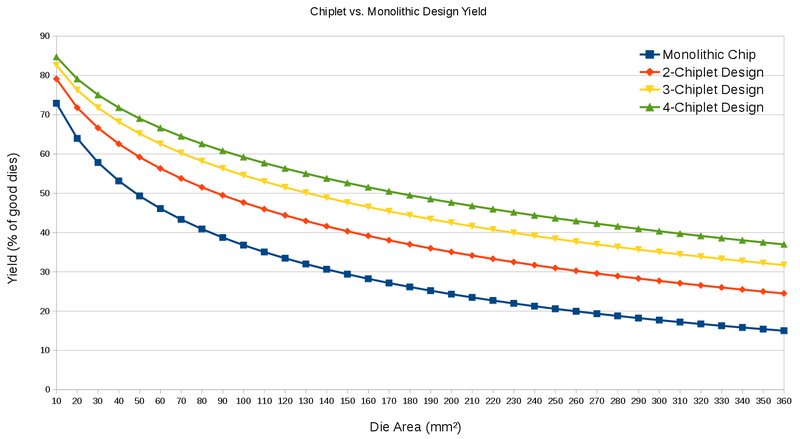

根据Omdia发布的数据显示,目前半导体产业内增长最快速的三个应用领域分别为汽车处理、数据中心服务器处理和高级移动半导体领域,预计未来5年的增长率分别为16%、12%和7%。受高速、高算力和高带宽需求的影响,这些应用领域的处理器工艺制程已经迈向新节点,达到了市场上最先进的5-7nm级别,预计到本世纪末将达到1nm的范畴。 图 | Fab 数字制程节点快逼近1nm工艺节点的提高不仅意味着产品面世周期的延长,成本的指数型增长,还面临随着单芯片集成度不断提高、算力越来越密集、晶圆面积不断增大后,良率和产量开始走下坡的挑战。有数据表明,当单芯片晶圆面积只有10 mm²时,良率可达70%以上,而当单芯片晶圆面积增长到360 mm²时,良率已经降至15%左右。所以业界开始寻求降本增产,加速产品上市的方法。而以chiplet构成的系统可以说是一个“超级”异构系统,给传统的异构SoC增加了新的维度。业内专家称,采用经过充分测试和验证的chiplet可以大大缩短产品的上市时间,降低芯片的研发成本。这样做的好处是可以根据需要利用不同的制程节点来优化目标设计。根据统计数据显示,单芯片面积同为360 mm²时,采用4颗小芯片的方案良率可从上述的15%提升至37%左右。

图 | Fab 数字制程节点快逼近1nm工艺节点的提高不仅意味着产品面世周期的延长,成本的指数型增长,还面临随着单芯片集成度不断提高、算力越来越密集、晶圆面积不断增大后,良率和产量开始走下坡的挑战。有数据表明,当单芯片晶圆面积只有10 mm²时,良率可达70%以上,而当单芯片晶圆面积增长到360 mm²时,良率已经降至15%左右。所以业界开始寻求降本增产,加速产品上市的方法。而以chiplet构成的系统可以说是一个“超级”异构系统,给传统的异构SoC增加了新的维度。业内专家称,采用经过充分测试和验证的chiplet可以大大缩短产品的上市时间,降低芯片的研发成本。这样做的好处是可以根据需要利用不同的制程节点来优化目标设计。根据统计数据显示,单芯片面积同为360 mm²时,采用4颗小芯片的方案良率可从上述的15%提升至37%左右。 图 | 与单片芯片相比,晶粒chiplet技术可实现更高的产量不过有一点是无论如何都避免不了的,那就是先进工艺节点下多样的低核心电压,以及功能堆叠下的峰值电流的增加,因此从处理器到应用系统,所需的电源管理系统也变得愈加复杂。总结下来就是,更强大的数据处理能力将拉动更高复杂性、更高性能的电源管理市场的发展。谈到电源管理,我们不得不说一说当前火热的汽车电子市场。随着汽车智能网联、电动化趋势的不断发展,汽车电子成本占比将达到整车成本的50%,包括AI芯片、MCU、传感器、通信模块、电池管理、DC/DC电压转换器、牵引电机逆变器、车载充电器,以及其他系统的电气化设备等,同时需求总量正呈现指数型攀升趋势。此外,随着汽车电动化和智能化的普及,新能源汽车的持续快速放量,电动汽车中的核心部件——功率半导体的需求量新增巨大。然而Si材料在经历了70年的开发后,到达了它的材料极限,传统的IGBT和HVMOS在效率和功率密度上都存在不足。此时,拥有更快切换速度、温漂损失小、功率密度更高、集成度更高的第三代半导体材料制成的SiC和GaN FET被搬上了汽车电子的舞台,并将逐渐占领市场。

图 | 与单片芯片相比,晶粒chiplet技术可实现更高的产量不过有一点是无论如何都避免不了的,那就是先进工艺节点下多样的低核心电压,以及功能堆叠下的峰值电流的增加,因此从处理器到应用系统,所需的电源管理系统也变得愈加复杂。总结下来就是,更强大的数据处理能力将拉动更高复杂性、更高性能的电源管理市场的发展。谈到电源管理,我们不得不说一说当前火热的汽车电子市场。随着汽车智能网联、电动化趋势的不断发展,汽车电子成本占比将达到整车成本的50%,包括AI芯片、MCU、传感器、通信模块、电池管理、DC/DC电压转换器、牵引电机逆变器、车载充电器,以及其他系统的电气化设备等,同时需求总量正呈现指数型攀升趋势。此外,随着汽车电动化和智能化的普及,新能源汽车的持续快速放量,电动汽车中的核心部件——功率半导体的需求量新增巨大。然而Si材料在经历了70年的开发后,到达了它的材料极限,传统的IGBT和HVMOS在效率和功率密度上都存在不足。此时,拥有更快切换速度、温漂损失小、功率密度更高、集成度更高的第三代半导体材料制成的SiC和GaN FET被搬上了汽车电子的舞台,并将逐渐占领市场。

驱动半导体工业发展的动力,

正让测试面临挑战

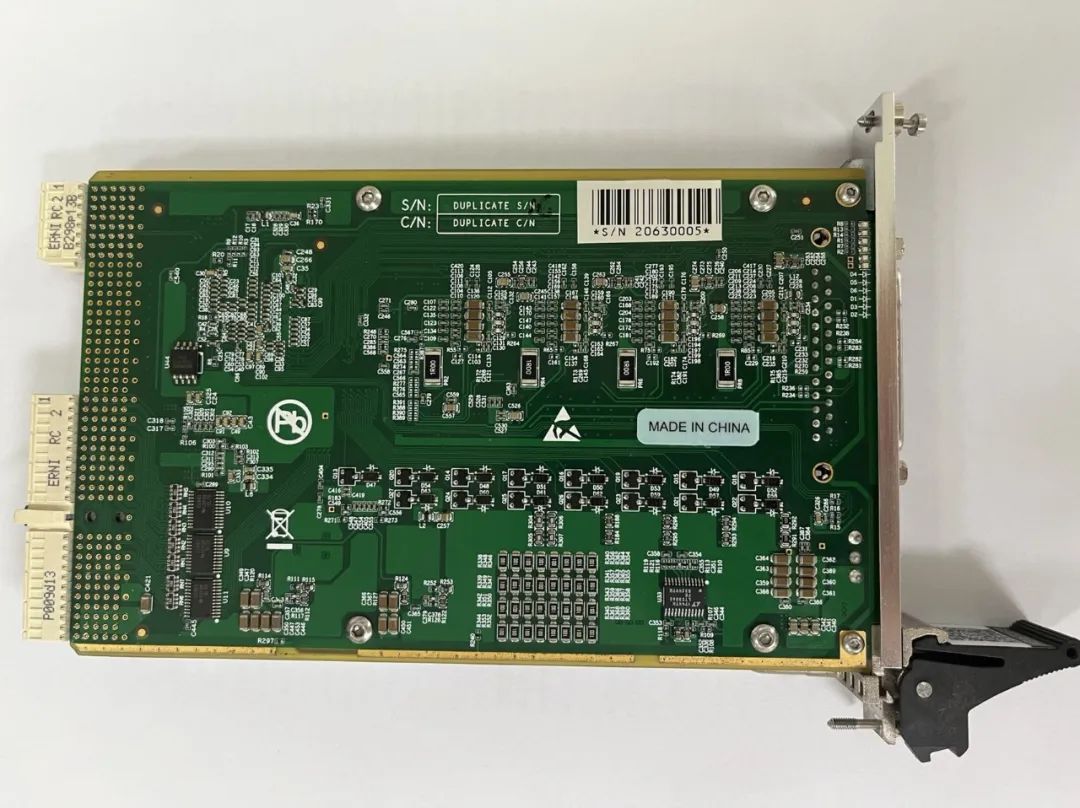

无论是云服务器、5G通信、人工智能还是汽车电动化智能化的发展,都会对半导体测试带来挑战。图 | SoC测试示意图比如SoC工作在多样的低核心电压(<1V)下,但整个系统的峰值电流又很高(10-100A),于是为了满足这个趋势的需求,业界开发出了低噪声、高效率,被称为负载电装置的功率调节器。而这些器件在出厂前需要经过更高水平的负载和过流测试,更低且更精确的导通电阻RDS(on)的测量。再比如电动汽车的BMS,通常单节电池的电压范围是3.6V-4.7V,所以其输出和测量精度就要求在0.1mV左右。同时,在25个单元电池的监控中,其浮地共模电压要达到120V,以适应在最高单元上运行高达120V的现代BMS设计,所以这是一种高共模电压下的高精度电压测量。值得一提的是,针对这些高电压、大电流、高精度的测试,联合仪器的源测量单元板卡UI-X6320是非常完善的。

UI-X6320是标准的3U PXI板卡,具有高精度V/I 源测功能,4个通道。所有通道都具有高精度的可编程电压电流功能,电压电流可以从–24V到+24V@1000mA。所有通道可以直接连到外部DUT上,连接器是25pin的D-Sub标准接口,包括4个force通道,4个sense通道和地。

UI-X6320可以用来构建自动测试系统,测试效率高,可以缩减硬件测试时间,软件集成化高, 开发容易快.基于PXI架构, UI-X6320可以和其他板卡配合使用,比如 数字化仪, RF射频模块,频谱分析仪模块,数字功能模块等搭建混合功能测试系统,这种搭配使用采用的多核效率高,同时响应快。另外Additionally, 这种模块化,集成化多通道的功能,可以对多个器件进行并性测试,从而提高测试产量。

UI-X6320单张板卡,集成有电源功能,高精度源灌功能,以及读写快速响应功能。这个高精度模块可以实现高电压同时电流测试,而且,在保持高精度的同时还具有高响应速率和高采样率,能快 速发送和快速测量,甚至可以通过波形 的方式表现. 同时,板卡配置了继电器,隔离效果好,有被测器件与测试板卡之间的隔离保护功能, 板卡具有remote sense功能,能够进行测试中的校准补 偿,保护小信号完整性同时,减少漏电 流的产生,准确度更高. 这些强大功能 能使得UI-X6320应用到宽电压需求应用,例如研发测试,参数测试,功能测试, 量产测试,可以搭配测试RF,混合IC, ATE, 数据采集, 及控制系统等。

产品特点:

标准PXI总线产品

4通道,高精度V/Isource和measurement

支持电流源灌(四个象限)

FV/MI,FI/MV,FV/MU,FI,MI

+24V/-24V电压量

6个可选测流量程,从5uA到1000mA

16位加压加流精度

18位测压测流精度

可编程钳位电流功能

同步采集功能

继电器关闭状态,测试板和DUT间隔离性能好

可选外部供电

目标应用:

半导体测试

ASICstestin

ATE数字测试

写在最后

我们生活在一个有趣的时代,半导体技术的未来及其在我们共同的未来中将扮演的角色从未如此令人兴奋。今天的半导体产业正在经历转型,业务增长不再由数量或单位数量驱动,而开始关联更多的复杂性和终端市场层面的多种技术集成。这些新兴因素对未来的设计和制造设备提出了一系列新的挑战,比如云、AI处理器、边缘处理器、有线电源转换和电信基础设施的新生和变化,而正是这些变化让我们保持在陡峭的学习曲线上。汉通达团队希望与您一同踏上这段有趣的成长旅程,当您遇到测试挑战时,欢迎联系汉通达,在合作中实现共赢。

-

测试

+关注

关注

9文章

6408浏览量

131675 -

半导体

+关注

关注

339文章

31238浏览量

266562

发布评论请先 登录

华宇电子亮相2026中国半导体先进封测大会

先进封装时代,芯片测试面临哪些新挑战?

携手伏达半导体:RedPKG解决方案助力封装自主,加速产品创新

奥芯明:AI驱动半导体产业迎来“异构集成”新纪元,先进封装成破局关键

Chiplet封装设计中的信号与电源完整性挑战

BW-4022A半导体分立器件综合测试平台---精准洞察,卓越测量

半导体欧姆接触工艺 | MoGe₂P₄实现超低接触电阻的TLM验证

后摩尔定律时代,国产半导体设备的前瞻路径分析

先进封装转接板的典型结构和分类

后摩尔时代破局者:物元半导体领航中国3D集成制造产业

Chiplet与3D封装技术:后摩尔时代的芯片革命与屹立芯创的良率保障

后摩尔时代,半导体测试的挑战与良策

后摩尔时代,半导体测试的挑战与良策

评论