在过去的几年里,数据领域陆续出现重大技术突破,特别是在数据传输和处理速度方面。AI(人工智能)、IoT(物联网)、5G 等科技日益成熟且应用广泛,其中PCI Express(PCIe)技术在这些产业中扮演着重要的角色。PCIe 5.0的出现引起数据领域的高度关注,因为它在性能和速度方面带来重大改进。伴随着最新的PCB模拟技术,PCIe 5.0可以彻底改变我们对数据处理的认知和使用方式。

究竟什么是PCIe?

PCIe 是⼀种高速串行计算机扩展总线标准,作为计算机系统不同组件之间的数据传输,例如CPU与GPU或其它加速处理器之间传输数据都依赖这条PCIe 主要干道。以目前开发主流的PCIe 5.0 为例,其传输速度可达32 GT/s,是PCIe 4.0的两倍。由于在16个通道的配置中能够传输128GB/s(每秒千兆字节),PCIe 5.0不仅可以提供高速、可靠的数据传输通道,同时还具备了灵活的扩展性以满足大量信息的处理需求,包括人工智能、机器学习和信息分析。

延伸阅读:服务器市场洞察,最为产业期待的下一个十年

PCIe 5.0的核心优势

1.增强的速度和性能相较于PCIe 4.0,PCIe 5.0最显著的优势是增强的速度和性能。2倍速度的提升将转化为更快的数据传输率,减少延迟,并提高整体系统性能。

2.更加扩大的带宽PCIe 5.0具有更高的带宽,可以实现更高的数据吞吐量。让它成为需要实时处理大量数据的理想选择,如:数据中心、高性能计算或电竞游戏等。

3.向下兼容PCIe 5.0能够向下兼容PCIe 4.0和PCIe 3.0,意味着它可以与既有接口的设备一起运作。确保用户可以升级他们的系统,而不必更换所有的组件。

PCIe 5.0之PCB设计及挑战

负责制定PCI Express的PCI-SIG组织(Peripheral Component Interconnect Special Interest Group),于2017年便启动了PCIe 5.0规格制定的工作,并于2019年发布了该项标准。

PCIe 5.0的通道损耗设计在16GHz的频率点应小于36 dB,在顾及通道损耗规范及讯号质量的同时,PCB的成本管控也必须一并考虑,搭配合适的PCB材料与铜箔等级,可有效地降低开发成本,并在讯号完整性与成本之间取得平衡点。

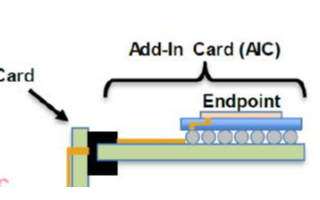

以典型只有一个连接通道的PCIe5为例,扣除掉前端CPU Chip约9 dB损耗、后端的PCIe标准卡(Add-in card)约9.5 dB损耗及保留10%设计余量约3.6 dB,其PCB板端能运用的损耗值只剩约13.9 dB。一般服务器主板的PCIe走线长度约落在8inch(203.2mm)左右,若采用标准的PCB板材及铜箔,其PCB损耗约在18.5 dB,远远大于设计规范,因此需要搭配更高阶的PCB板材及铜箔,成本也将增加,因此准确的掌握高阶PCB板材的损耗将有助于成本的优化。

什么是PCB电性模拟?

PCB电性模拟是指透过软件来模拟和分析印刷电路板(PCB)行为的过程。透过多种软件可以模拟出电路板的电性表现结果,在进入生产之前先找出潜在问题,进一步解决问题、优化设计。例如,模拟电路板对不同电压、电流和频率的反应。通过模拟PCB的行为,工程师可以发现问题并改善电路板的性能及可靠度。

PCB材料损耗验证与检测

PCIe 5.0电性损耗量测

综观整个业界,PCB电性损耗验证具有多种不同方式,过往的主流验证方法是采用SET2DIL (Single-Ended TDR to Differential insertion loss) 或SPP (Short Pulse Propagation)二者,但是这两种方法,受到钻孔(Via)和钻孔残断(Via Stub)的寄生电容与电感的影响,在高频时容易导致量测不准确。于是Intel 开发了Delta-L分析手法,省去繁杂的校正步骤并扣除前述的寄生效应 (Parasitic Effect),并偕同治具供货商开发专属的探针头,建立一套标准的PCB材料损耗 (Loss Per Inch) 量测手法。USI已建立此量测流程,此举将有助于在高速传输接口设计领域中,确保产品质量与最终产品的检测。

USI环旭电子凭借在云端及存储设备拥有多年的设计经验,PCB设计期间提供完整的设计服务及电性模拟服务,利用3D电磁场模拟软件进行PCB阻抗优化,可降低多重反射对讯号的影响,同时也运用时域电路分析工具,有效解决干扰、衰减、串音等相关问题,确保终端的讯号可符合PCI-SIG的标准规范。

延伸阅读:锁定边缘运算领域,抢攻 AI 商机

PCB高速讯号设计检查与模拟

由USI环旭电子自主开发的自动化设计模拟系统(Front-End Design Simulation) ,已成功应用在各大芯片厂商(Intel、AMD、Qualcomm、MTK…等)的设计规范(Design Guideline), 主要用于确保电源设计的完整性。此外,也开发自动检查PCB布线Design Rule,除了有效取代人工繁琐的检查及大大缩短开发时程之外,自动化检查带来快速且优良的PCB布线质量。例如:多数服务器的讯号线有2000~5000条,难以人眼确认布线质量,经过自动化的检查,更能加以确保并提升PCB布线质量。

PCIe现在即是未来

PCIe的重点向来都聚焦在提高带宽和数据传输速度。PCI-SIG 在2021的开发者大会正式发布PCI 6.0的规范,调变技术由NRZ (Non-Return-to-Zero) 改为PAM4 (Pulse Amplitude Modulation),传输速率可到达64GT/s。此外,PCIe 6.0还引入一些新功能,如PAM4编码,它可以实现四级信令以提高数据传输速率,以及低延迟的前向纠错(FEC), 可以同步改善错误检测和纠正,以实现更快和更可靠的数据传输。来年(2022) 随即着手制定PCIe 7.0 标准,让传输速率又再度翻倍至128GT/s的高性能。

另一个趋势是PCIe在汽车和工业系统等新应用中的使用越来越多。这些系统需要高速数据传输和实时处理,使PCIe成为其通信和控制系统的理想选择。PCIe 5.0和PCB模拟技术的结合可以为下一代技术提供更高的性能和更快的数据处理速度。

设计师可以利用这些技术来减少设计缺陷,提高系统性能,并在更短的时间内将新产品推向市场。虽说 PCIe 5.0要大规模投入到消费市场还需要一段时间,但USI 会持续精进高速接口相关技术的设计及优化以提供高竞争力的产品来满足客户的需求。

FAQs1.PCIe 5.0和PCIe 4.0之间有什么区别?

与PCIe 4.0相比,PCIe 5.0提供2倍的传输速度以及更扩大的带宽。这使得PCIe 5.0更适合于处理海量数据和实时应用。

2.PCB模拟技术能够帮助什么?

利用PCB模拟技术,你可以更好地了解设计中的潜在问题,并在实际生产前对其进行优化。这有助于提高系统性能,降低成本,并节省时间。

3.PCB损耗验证是必要的吗?

是的,藉由测量PCB的电性损耗结果,可以评估信号在PCB线路中的衰减情况,确定是否需要采取进一步的设计优化措施,如改变PCB材料、线路布局或采用增强信号传输技术等。当PCIe 5.0 传输速度达到了32 GT/s,损耗量测是重要且必要的步骤。

4.PCB模拟技术能否检测出所有的设计缺陷?

PCB模拟技术可以检测出大多数设计缺陷,但并不是万无一失。重要的是,要结合使用模拟和物理测试,以确保你的设计在性能和可靠性方面得到优化。

5.PCB高速讯号设计自动化检查与模拟与过去差异为何?

一般服务器多数使用Intel or AMD平台,讯号线有2000~5000条,难以人眼确认布线品质。因此,透过开发并导入自动化检查,更能加以提升PCB的布线质量。电源完整性模拟必须等PCB设计近乎完成才能开始执行,而模拟设定皆需一定人工时间,因此导入电源完整性模拟自动化,即能在有限时间内,达到优化电源设计进而符合设计目标,确保各芯片组可以正常工作。

编辑:黄飞

-

pcb

+关注

关注

4417文章

23965浏览量

426178 -

模拟技术

+关注

关注

17文章

472浏览量

40888 -

PCIe

+关注

关注

16文章

1479浏览量

88924

原文标题:【PCIe 5.0】深入PCB设计及验证 掌握高速传输核心

文章出处:【微信号:环旭电子 USI,微信公众号:环旭电子 USI】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

[讨论]PCB设计面临的新挑战

【汉普观点】PCB设计面临的挑战

PCB设计之电容

PCB设计软件(Sprint Layout) 5.0 汉化版

什么是 PCIe 5.0? PCIe 5.0规范以及挑战

PCB设计面临的挑战

什么是PCIe?PCIe有什么用途?PCIe 5.0有何不同?

PCIe 5.0之PCB设计及挑战

PCIe 5.0之PCB设计及挑战

评论