在博客 DDR VIP 模型的无缝快速初始化中,我们讨论了内存 VIP 模拟可以选择快速完成重置和初始化过程并进入空闲状态并开始读取和写入内存位置的重要性。我们提出了一种方法来实现这一点,即在完成重置和初始化所需的所有JEDEC标准步骤时缩小所需的时序。

在这篇博客中,我们将讨论 Synopsys Memory VIP 如何允许完全跳过初始化,同时保持模型的正确行为。

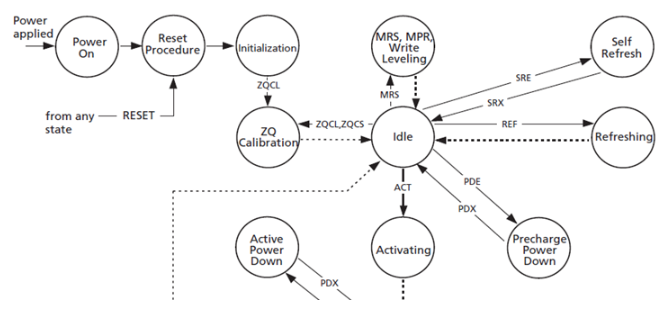

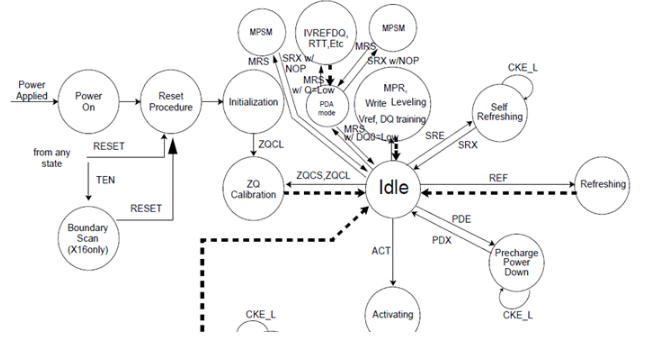

使用 Synopsys 内存 VIP 的 Skip 初始化功能可确保模型处于空闲状态,从而绕过重置过程的要求。在该状态下,VIP 已准备好接受 REF、MRS 和 ACT 等命令。允许的命令如图 1 – DDR3 SDRAM JEDEC 标准 JESD79-3F 状态图和图 2 – DDR4 SDRAM JEDEC 标准 JESD79-4 状态图所示。

图 1 – DDR3 SDRAM JEDEC 标准 JESD79-3F 状态图

图 2 – DDR4 SDRAM JEDEC 标准 JESD79-4 状态图

跳过初始化功能适用于 DDR3、DDR4。应该注意的是,使用skip init在后门设置后重置将清除所有设置并设置回默认值。

对于离散设备,我们可以使用以下方法将VIP设置为跳过初始化模式:

|

// dram_cfg is handle of class svt_ddr_confitugation dram_cfg.skip_init = 1 |

对于 DIMM 设备,我们可以使用以下步骤将 VIP 设置为跳过 DIMM 型号上的初始化序列:

|

// dimm_cfg is handle of svt_ddr_dimm_configuration and // configuring the skip_init setting for individual DRAM // configurations with DIMM structure foreach(dimm_cfg.data_lane_cfg[i]) begin foreach(dimm_cfg.data_lane_cfg[i].rank_cfg[j]) begin dimm_cfg.data_lane_cfg[i].rank_cfg[j].skip_init = 1; end end // Skip initialization setting for RCD component within an // RDIMM and LRDIMM dimm_cfg.ca_buffer_cfg.skip_init = 1; |

在通过config_db机制传递配置对象之前,应在构建阶段完成离散和 DIMM 型号的跳过初始化设置。

此外,这些设置可以在构建阶段之后完成,但用户必须调用 reconfigure() 方法来更新模型中的设置。这必须在接口上执行任何命令之前完成。

以下是 reconfigure() 方法调用的语法:

|

// For Discrete Device Model env.mem_agent.reconfigure(dram_cfg); // For DIMM Model env.dimm_env.reconfigure(dimm_cfg); |

在随后的博客中,我们将讨论如何使用前门和后门访问设置模式寄存器。

审核编辑:郭婷

-

寄存器

+关注

关注

31文章

5620浏览量

130440 -

DDR4

+关注

关注

12文章

351浏览量

43343 -

Ref

+关注

关注

0文章

20浏览量

28775

发布评论请先 登录

6657的DDR3初始化不成功

如何从.mem文件初始化加密的ddr4内存模型?

手机模块初始化向导

如何让KeyStone DDR3接口初始化的详细资料概述

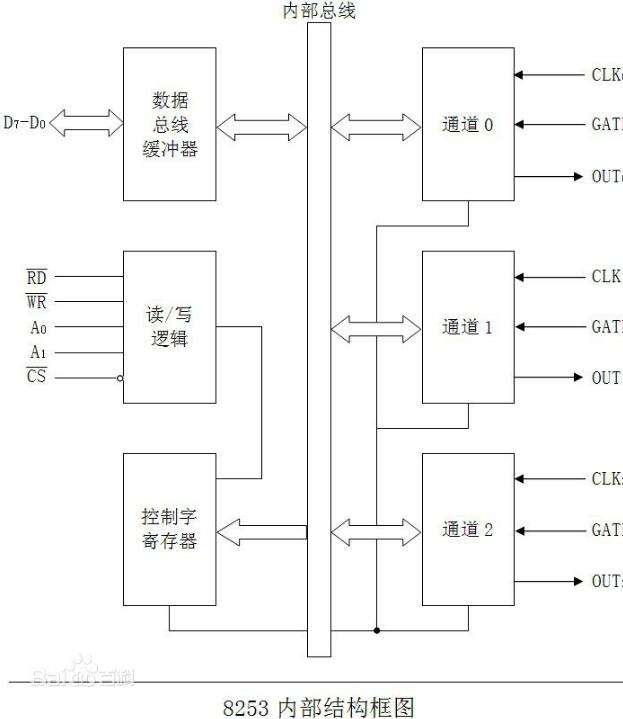

8253初始化程序分享_8253应用案例

在51平台下初始化文件的引入导致全局变量无法初始化的问题如何解决

DDR VIP模型的无缝快速初始化

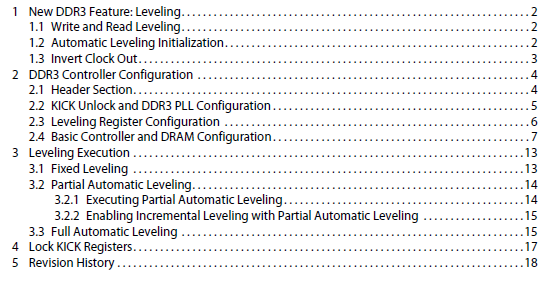

DDR4-初始化、训练和校准

GraniStudio:初始化例程

跳过DDR VIP模型的初始化

跳过DDR VIP模型的初始化

评论