一、综合理论基础

综合理论,称为综合目的编码风格(Coding Style for Synthesis),和非综合目的编码风格(Coding Style for NonSynthesis)。

综合目的编码,是指:

什么样的代码或代码块,对应综合结果的什么样的电路(What Statements is What Circuit)

需要什么电路,应该使用什么样的代码描述(What Circuit is What Statements)

根据综合理论的发展和HDL语言的发展,西方理论界提出综合友好的概念,即EDA的工程师,必须知道代码的综合意义。与西方科学技术体系的“形式逻辑”相同,综合理论也是诞生与“形式逻辑”。

1.1代码模型分析CMA(Code-Model Analysis)

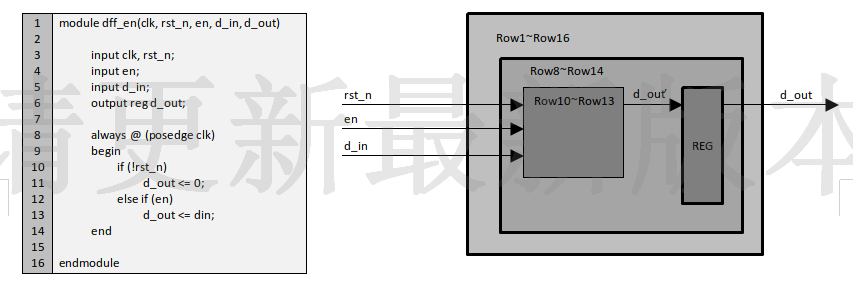

综合理论的基础是代码模型分析:

代码行中,被驱动的信号(赋值号左侧的信号),对应所综合电路的输出信号

代码行中,被引用的信号(赋值号右侧的信号),对应所综合电路的输入信号

根据电路的实际物理,进行资源分配。

代码或代码块CB(Code Block),所综合得到的电路模型,称为代码模型CM(Code Model)

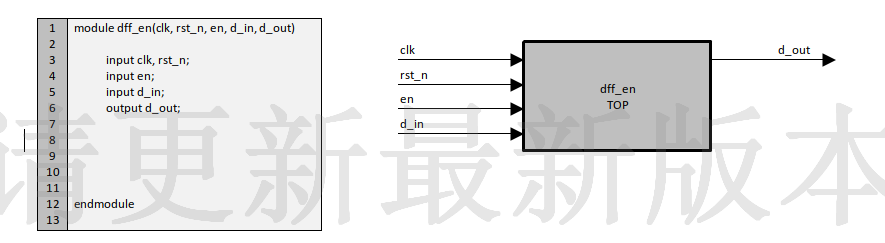

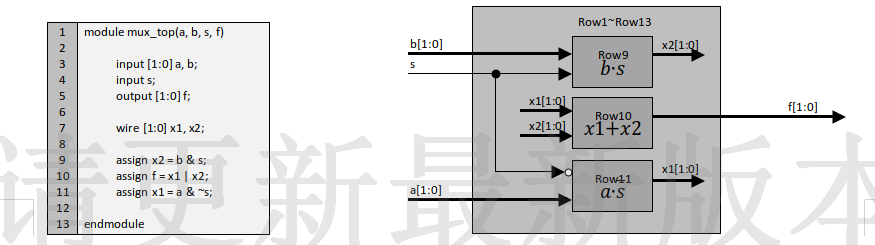

例一(显模Explicit Model):

1.1.1顶层电路模型

1.1.2顶层描述

1.2并发语句和顺序语句的可综合性

HDL语言与算法语言类似,需要讨论研究编码顺序与综合意义之间的关系。在HDL的早期理论界,是这样定义的:

在HDL的编码顺序中,编写顺序发生改变,不会影响综合结果的代码,称为并发语句CAS(Concurrent Assignment Statements)

在HDL的编码顺序中,编写顺序发生改变,将会影响综合结果的代码,称为顺序语句SAS(Sequential Assignment Statements)

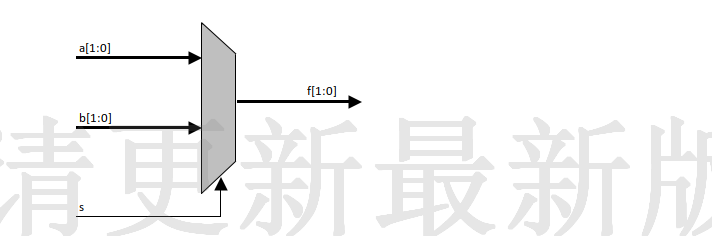

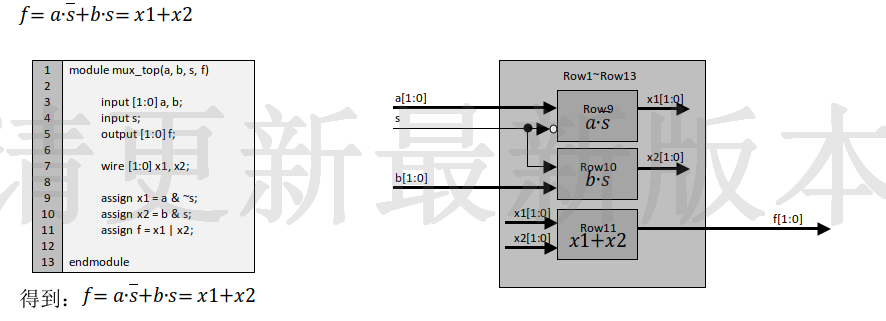

例二(并发语句例子):

一个二选一多路器的逻辑:

布尔表达式:

改变编码顺序后:

得到:

综合意义相同,是并发语句CAS

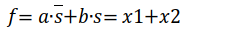

例三(顺序语句例子)

译码逻辑真值表:

rst_n | en | sel | Note |

0 | 0 | SEL_ROW6 | 复位选择 |

0 | 1 | SEL_ROW6 | |

1 | 0 | SEL_ROW10 | |

1 | 1 | SEL_ROW8 |

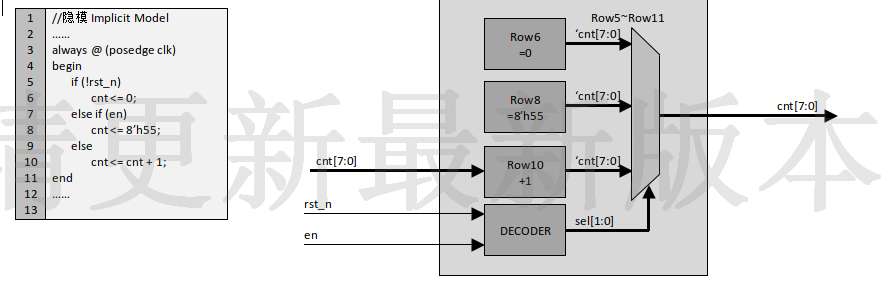

译码逻辑真值表:

rst_n | en | sel | Note |

0 | 0 | SEL_ROW8 | 复位选择 |

0 | 1 | SEL_ROW6 | |

1 | 0 | SEL_ROW10 | |

1 | 1 | SEL_ROW6 |

综合意义不同,是顺序语句SAS

常用语句的并发和顺序类型表:

语句块 | 描述方式 | 类型 | Note |

module | module-endmodule | CAS | 显模描述 |

begin | begin-end | CAS | 隐模描述 |

behaviour | always | CAS | |

datflow | assign | SAS | |

if | if-else if-else | SAS | |

case | case-endcase | SAS | |

loop | while for | CAS | for语句可综合 |

sub/fuc | task-endtask function-endfunction | CAS | |

二、循环语句的可综合性

2.1循环语句的可综合性描述

循环语句中的循环体,在算法语言中,循环体的执行时一个典型的顺序过程,但在HDL语言中,用于综合目的时,这些循环体却是一个并发过程,此时,这些循环体被综合器重复描述,以提高编码效率。

循环体中的输出,不同的循环变量引用时,得到不同的输出,则称为:并发循环,对应的电路框架称为并发循环框架。

循环体中的输出,在不同的循环变量引用时,得到相同的输出,则称为:顺序循环,对应的电路框架称为顺序循环框架。

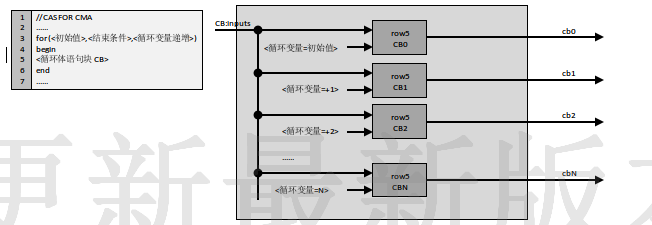

行为并发循环框架CMA:

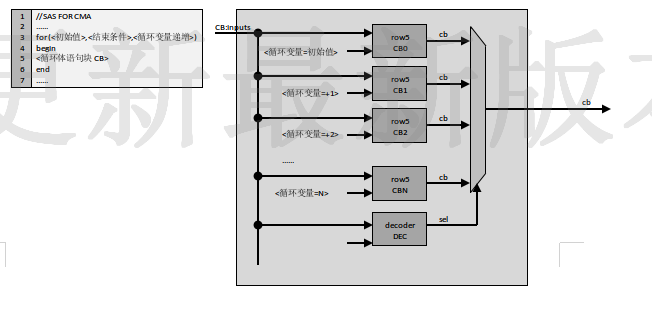

行为顺序循环框架CMA:

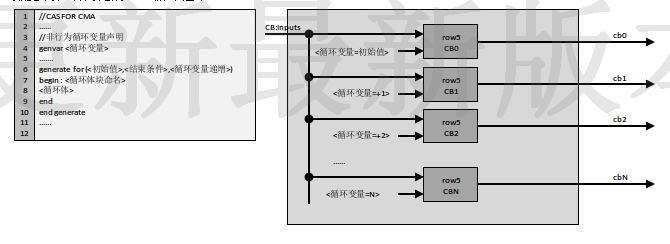

数据流和结构化的CAS循环框架:

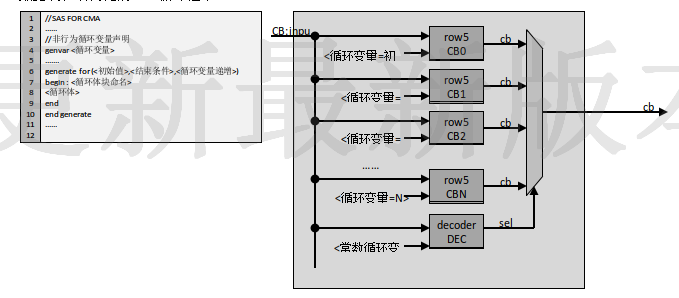

数据流和结构化的SAS循环框架:

2.2循环语句设计例子一

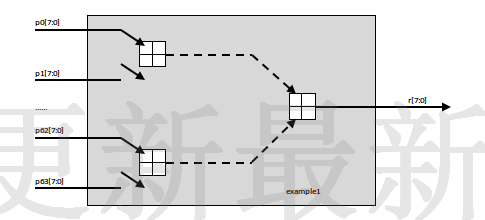

设计一个如下图所示的具有宽度为8的64输入端口的异或二叉树电路:

使用数学归纳法,证明循环语句实现的可综合性:

首先将循环变量修改为一个很小的基数,使用结构化建模描述,加以验证。

将基数加一,仍然使用结构化建模模型,加以验证。

将循环变量修改为LPM定制,加入循环变量,加以验证

将LPM定制的循环变量加以,加以验证

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:至芯FPGA课程之综合理论分享

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

-

FPGA

+关注

关注

1664文章

22502浏览量

639231

原文标题:至芯FPGA课程之综合理论分享

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

磁环电感计算:从理论公式到应用的关键跨越

智能制造综合实训平台数据采集综合解决方案

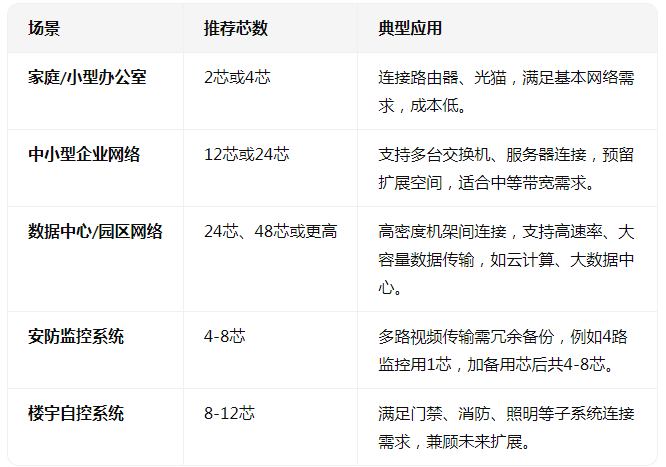

单模光纤理论速率是多少

梦之墨蓝牙音响工程实践课程开启电子专业实训新体验

基于瑞芯微 RK3588 的 ARM 与 FPGA 交互通信实战指南

开源RISC-V处理器(蜂鸟E203)学习(二)修改FPGA综合环境(移植到自己的Xilinx FPGA板卡)

学以致用 虚位以待|玄铁RV学院课程正式上线,玄铁与PLCT实验室邀您创“芯”未来

FPGA开发板vivado综合、下载程序问题汇总

光纤芯数怎么确定选多少芯的

监控光缆双层钢铠用几芯的?

易灵思与南京大学集成电路学院暑期课程圆满结课

利好!芯动联科预计上半年净利润同比暴增144.46%至199.37%

思尔芯携手南京大学开展暑期协同课程,产教融合共育集成电路英才

蔡司培训|提升技能必看——AUKOM 一级/二级课程培训

至芯FPGA课程之综合理论分享

至芯FPGA课程之综合理论分享

评论