今天我们将围绕交错式 ADC 转换器展开。当 ADC 转换器交错时,两个或多个具有定义的时钟关系的 ADC 转换器用于同时对输入信号进行采样并产生组合输出信号,从而导致采样带宽为多个单独的 ADC 转换器。

交错式 ADC 转换器无疑是推动更高效接口的一部分。交错式 ADC 转换器为系统设计人员提供了多项优势。然而,额外的转换器带宽带来了大量需要在 FPGA 或 ASIC 中处理的数据。必须有一些有效的方法来处理来自转换器的所有数据。在采样率在千兆采样范围内的转换器中继续使用 LVDS 接口变得不切实际。因此,JESD204B 是将大量数据从转换器获取到 FPGA 或 ASIC 的一种很好、高效的方法。

让我们花点时间离开界面,看一下交错。在通信基础设施中,除了对 DPD(数字预失真)等线性化技术的更宽带宽要求之外,还不断推动更高采样率的 ADC 以支持多频段、多载波无线电。在军事和航空航天领域,更高采样率的 ADC 支持多用途系统,可用于通信、电子监控和雷达等等。在工业仪器仪表中,对更高采样率 ADC 的需求一直在增加,以便能够准确测量更高速度的信号。让我们从了解交错式 ADC 的基础知识开始讨论。

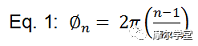

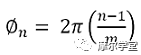

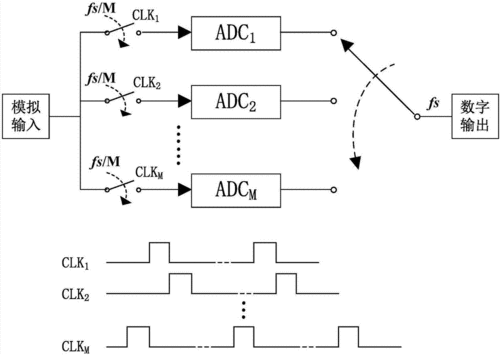

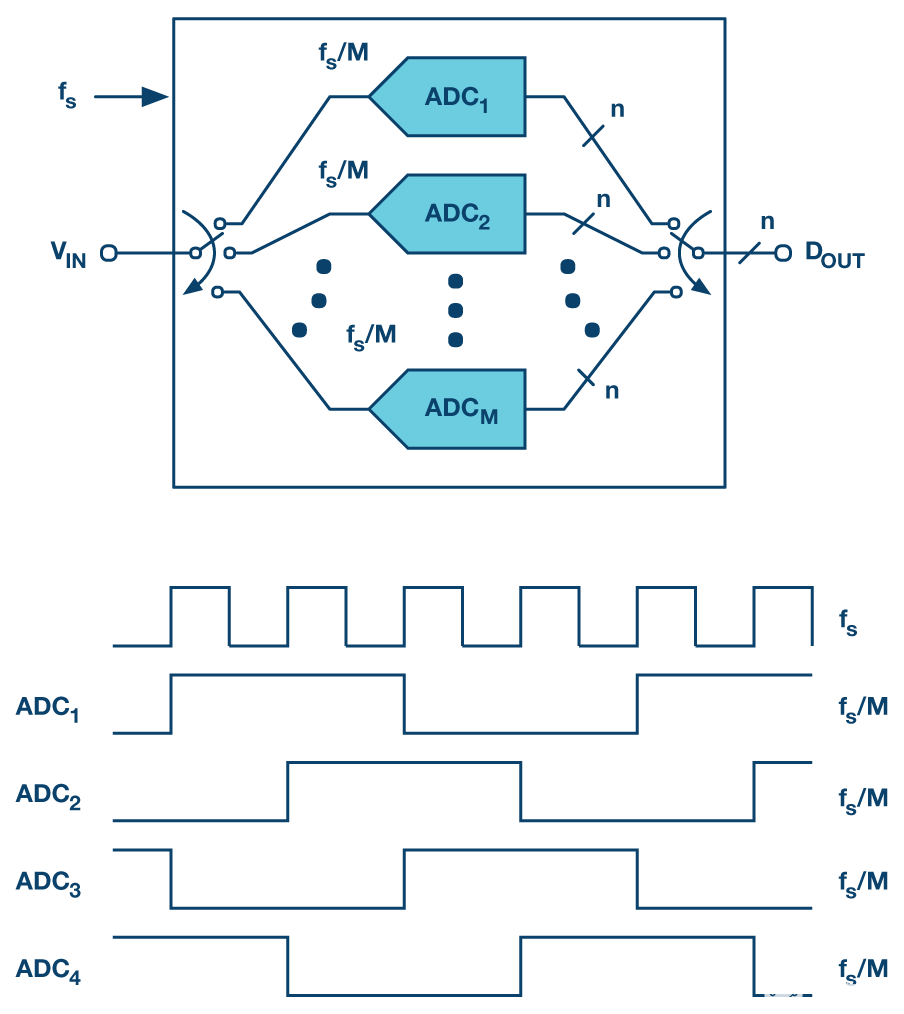

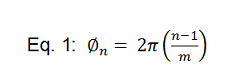

使用m 个 ADC 可以将有效采样率提高 m倍 。为了简单易懂,我们只关注两个ADC的情况。在这种情况下,如果两个采样率均为 f S的 ADC 交错放置,则最终采样率仅为 2f S。这两个 ADC 必须具有时钟相位关系才能正确交错。时钟相位关系由等式 1 控制,其中n 是特定的 ADC,m 是 ADC 的总数。

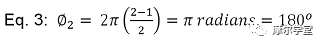

例如,两个采样率为 250MSPS 的 ADC 交错以实现 500MSPS 的采样率。在这种情况下,可以使用等式 1 推导两个 ADC 的时钟相位关系,并由等式 2 和 3 给出。

既然我们知道了时钟相位关系,就可以检查样本的构造了。图 1 直观地表示了两个 250MSPS 交错式 ADC 的时钟相位关系和示例结构。

图1

两个交错式 250MSPS ADC——基本图

请注意 180° 时钟相位关系以及样本是如何交错的。输入波形由两个 ADC 交替采样。在这种情况下,交织是通过使用除以二的 500MHz 时钟输入来实现的。分频器负责将所需的时钟相位发送到每个 ADC。

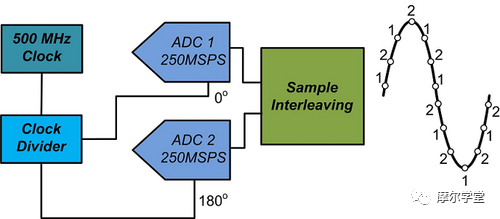

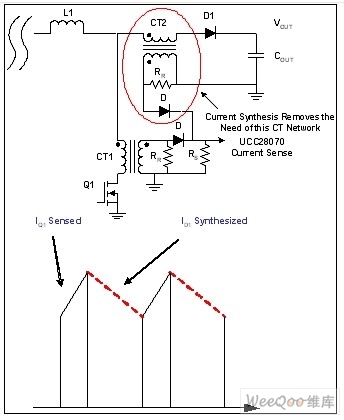

这个概念的另一种表示如图 2 所示。

图 2

两个交错式 ADC——时钟和采样

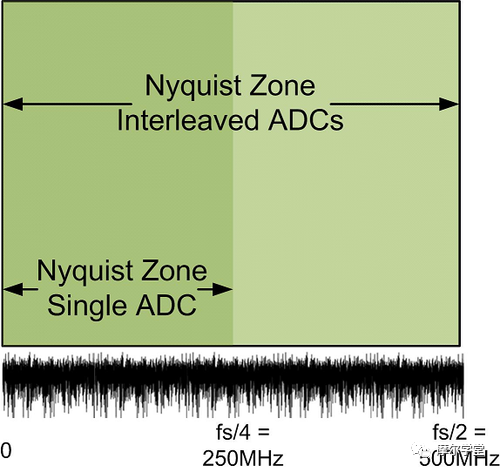

通过交错使用这两个 250MSPS ADC,采样率提高到 500MSPS。这将转换器奈奎斯特区的宽度从 125MHz 扩展到 250MHz,使工作可用带宽加倍。增加的操作带宽带来了许多优势。无线电系统可以增加支持的频段数量;雷达系统可以提高空间分辨率,测量设备可以实现更大的模拟输入带宽。

还有一些关于可以交错多少个转换器的问题,所以我想我会简要介绍一下。还有一些关于交错 ADC 挑战的问题。在我们看一看之前,让我们讨论一些好处。

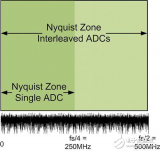

交错的好处跨越市场的多个部分。最理想的好处是交错式 ADC 的更宽奈奎斯特区可以增加带宽。我们将再次以两个 500MSPS ADC 交错创建 1000MSPS 采样率为例。这是交错两个 ADC 所允许的更宽带宽的表示。请注意,f S 显示的是一个转换器;交错式转换器采样率为 2 X f S。

两个交错的 ADC — 奈奎斯特区。

这为许多不同的应用创造了优势。许多设计中的系统要求天生就领先于商业 ADC 技术。无论 ADC 采样率有多高,市场似乎都需要更快的速率。交织允许关闭一些这种差距。军事和航空航天应用正在推动更高的带宽以实现更好的空间识别。此外,后端通信需要增加信道带宽。

随着蜂窝标准增加信道带宽和工作频段的数量,对 ADC 中可用带宽的要求也越来越高。在某些市场和应用中,还希望转向直接 RF 采样,这样无线电设计的级数就会更少,并且可以去掉解调器。在 ADC 上具有足够高的采样率也开启了放宽时钟要求的可能性。对齐 ADC 和 DAC 时钟以简化系统设计成为可能。在仪器仪表和测量应用中,需要更高的带宽来采集和测量信号。

增加的采样率为这些应用程序提供了更多的带宽。它允许更轻松的频率规划,并降低了通常用于 ADC 输入的抗混叠滤波器的复杂性和成本。

有了所有这些巨大的好处,人们不得不对价格感到疑惑。与大多数事情一样,天下没有免费的午餐。交错式 ADC 提供更高的带宽和其他好处,但也带来了一些挑战。

我们可以将多少个转换器放在一起?让我们简单了解一下交错式 ADC 的时钟要求。您可能还记得我上一篇博客中的等式:

当m等于 2 时,求解这个方程非常容易 。然而,当m等于 8 时,时钟要求变得更加困难 。代入m 并求解八个转换器的方程式可得到所需的时钟相位 0、45、90、135、180、225、270 和 315 度。如果输入时钟频率较低,那似乎还不算太糟糕,但交错的全部意义在于实现高采样率。

时钟频率的实际情况是 1GHz。这意味着时钟电路必须能够将输入时钟向下分频并创建相隔 125ps 的相位,而且必须准确地做到这一点。时钟上的任何错误或抖动都会降低性能。

还有其他事情需要考虑。当两个或多个转换器交错放置时,各个转换器之间会出现不匹配。我们还必须考虑转换器的模拟输入带宽。如何处理这些不匹配?我们如何处理模拟输入带宽?

-

转换器

+关注

关注

27文章

9447浏览量

156928 -

adc

+关注

关注

100文章

7946浏览量

556872 -

时钟

+关注

关注

11文章

1999浏览量

135226

发布评论请先 登录

用于PFC的交错式升压转换器的优势

交错式DC/DC转换器拓扑改进方案

改进交错式DC/DC转换器

交错式模数转换器ADC的原理是什么?

一文带你了解交错式ADC(数据转换器)

一文带你了解交错式ADC(数据转换器)

评论