声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

新思科技

+关注

关注

5文章

716浏览量

50067

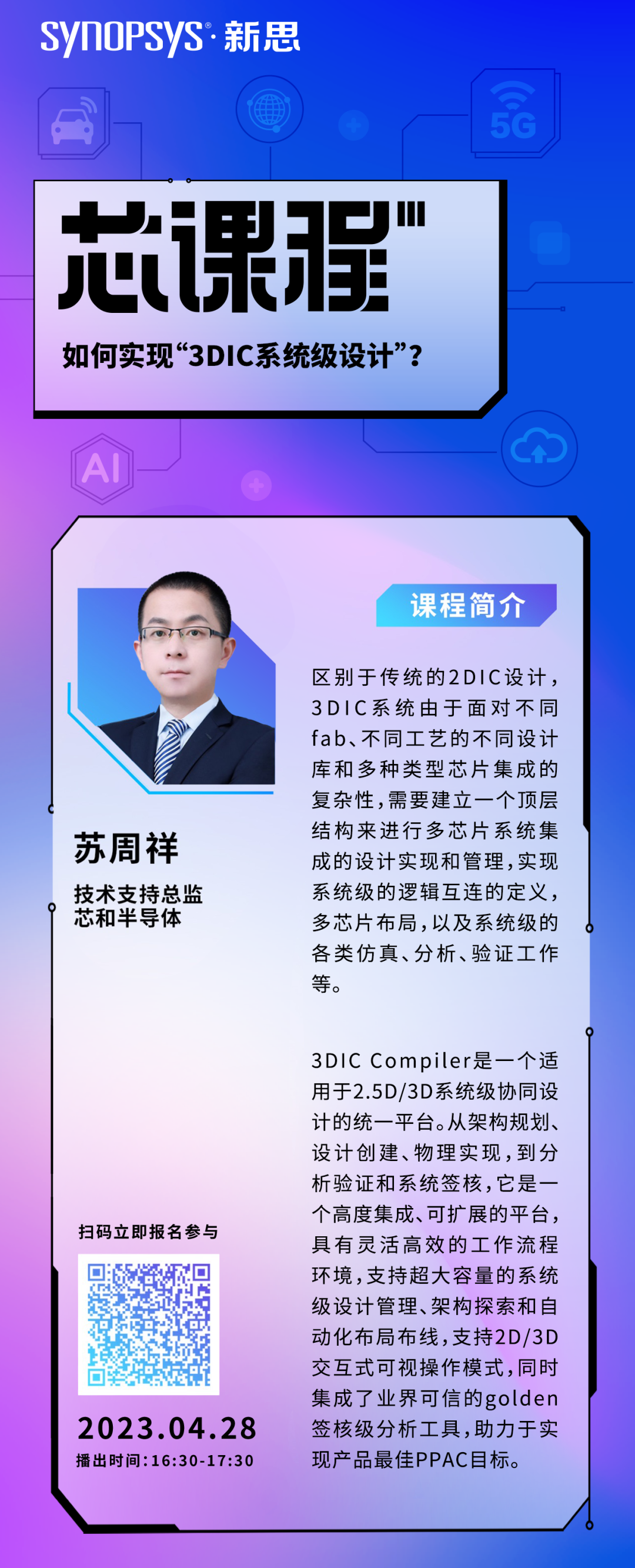

原文标题:下周五|谁说3DIC系统设计难?最佳PPAC目标轻松实现

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Multi-Die系统,掀起新一轮技术革命!

利用Multi-Die系统能实现异构集成,并且利用较小Chiplet实现更高良率,更小的外形尺寸和紧凑的封装,降低系统的功耗和成本。Ansys半导体产品研发主管Murat Becer指

大算力时代下,跨越多工艺、多IP供应商的3DIC也需要EDA支持

电子发烧友网报道(文/周凯扬)随着摩尔定律越来越难以维系,晶体管扩展带来的性能与成本优势逐渐减弱,半导体行业已经面临着新的拐点。Chiplet和3DIC集成的方案相较传统的单片技术相比,占用空间更小

新思科技3DIC Compiler获得三星多裸晶芯集成工艺流程的认证

新思科技经认证的多裸晶芯片系统设计参考流程和安全的Die-to-Die IP解决方案,加速了三星SF 5/4/3工艺和I-Cube及X-Cube技术的设计和流片成功。 新思科技3DIC

下周五|PHY IP如何助力开发者抢跑1.6T以太网新赛道?

原文标题:下周五|PHY IP如何助力开发者抢跑1.6T以太网新赛道? 文章出处:【微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

下周五|复杂芯片更要踩好节拍,一站式搞定SDC开发、验证和管理

原文标题:下周五|复杂芯片更要踩好节拍,一站式搞定SDC开发、验证和管理 文章出处:【微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

新思科技携手力积电,以3DIC解决方案将AI推向新高

3DIC设计的重要性日益凸显。当今市场对AI应用的需求在不断增加,而摩尔定律的步伐却在放缓,这使得芯片开发者不得不寻求其他类型的芯片架构,以满足消费者和领先服务提供商的预期。3DIC设计并不是简单

下周五|TSO.ai:打通AI应用“最后一公里”,降低芯片测试成本

原文标题:下周五|TSO.ai:打通AI应用“最后一公里”,降低芯片测试成本 文章出处:【微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

下周五|1+1>2?3DIC+Metis助力实现协同设计和仿真分析

原文标题:下周五|1+1>2?3DIC+Metis助力实现协同设计和仿真分析 文章出处:【微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

下周五|谁说3DIC系统设计难?最佳PPAC目标轻松实现

下周五|谁说3DIC系统设计难?最佳PPAC目标轻松实现

评论