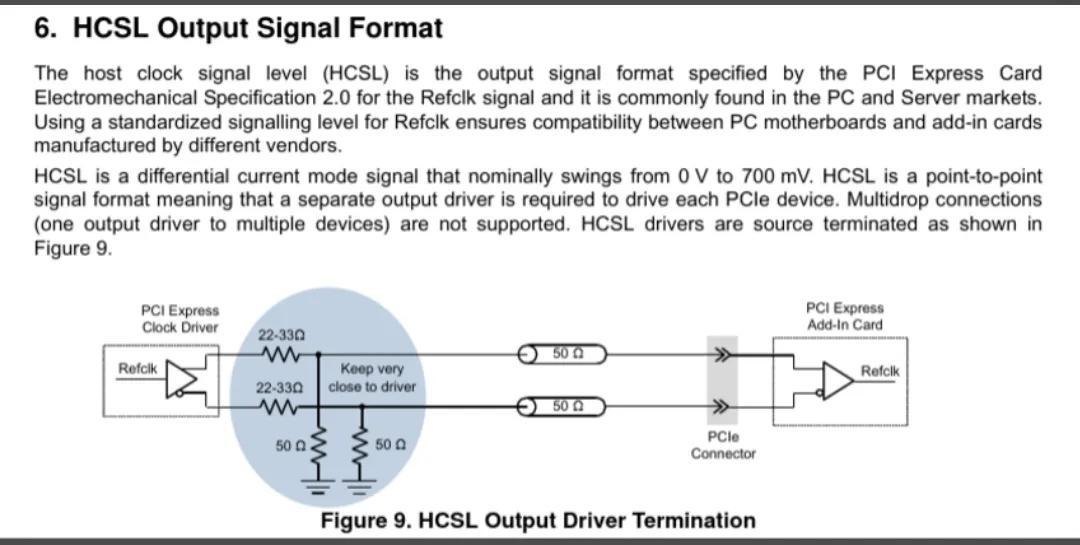

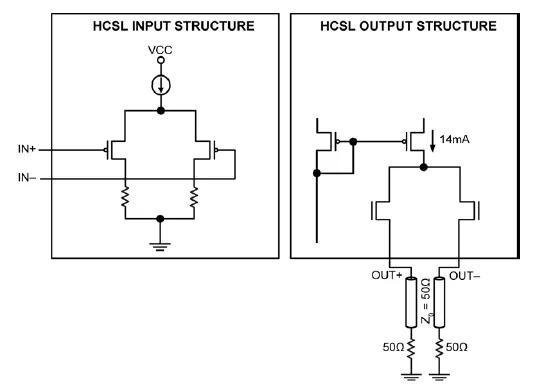

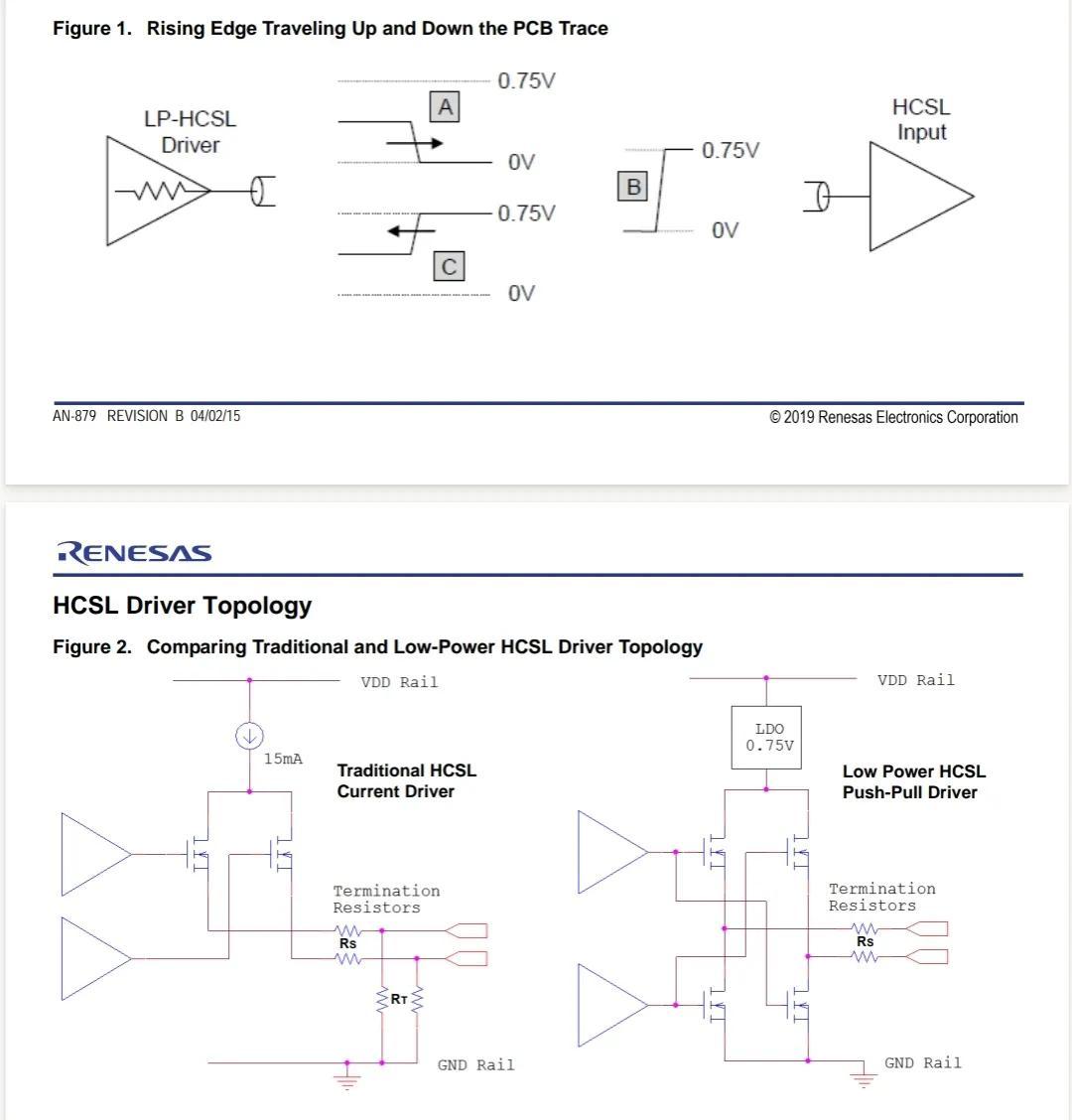

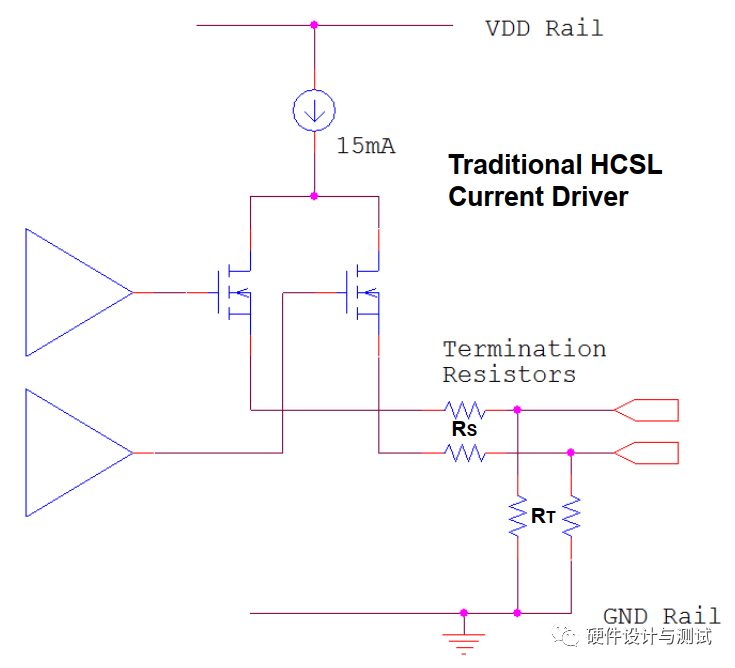

HCSL(HCSL--High−speed Current Steering Logic)一般用于PCIE参考时钟的电平类型,根据规范需要下拉电路,如下图HCSL之间的DC耦合。HCSL为电流输出驱动,输出结构由通常通过50Ω电阻器接地的15 mA开关电流源驱动。 标称信号摆幅为750 mV。

HCSL规范

HCSL输入输出拓扑

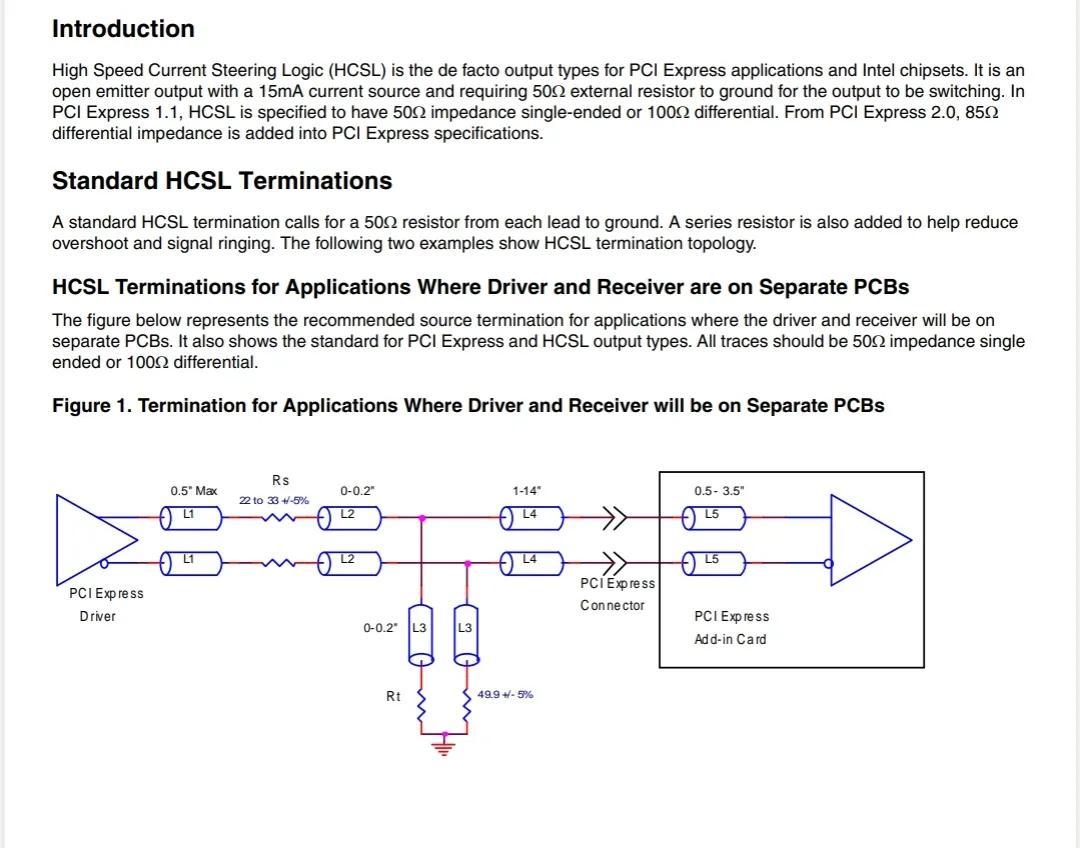

1-HCSL端接匹配

HCSL接口通常以50Ω负载源极端接,其中Rs大小一般为33Ω,匹配50Ω阻抗。 一般在输出端位置。驱动器本身具有17欧姆的输出阻抗,所以,需要串联一个33欧姆的电阻,以获得与50欧姆传输线的匹配。对于传统的HCSL,为了避免出现过度的振铃,串联电阻RS是必须要的。

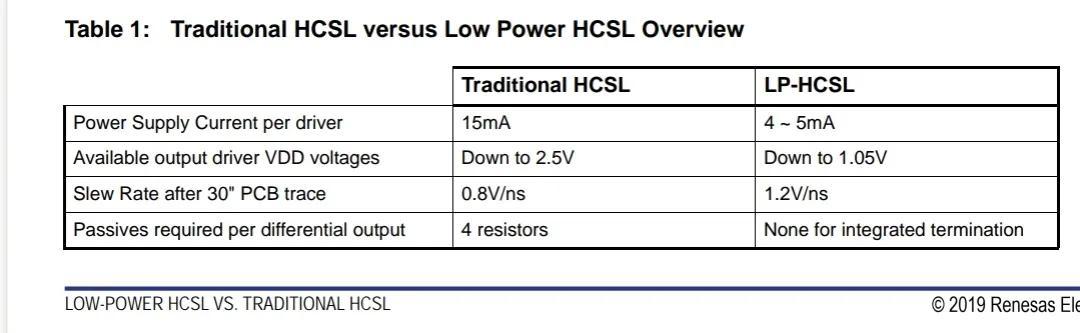

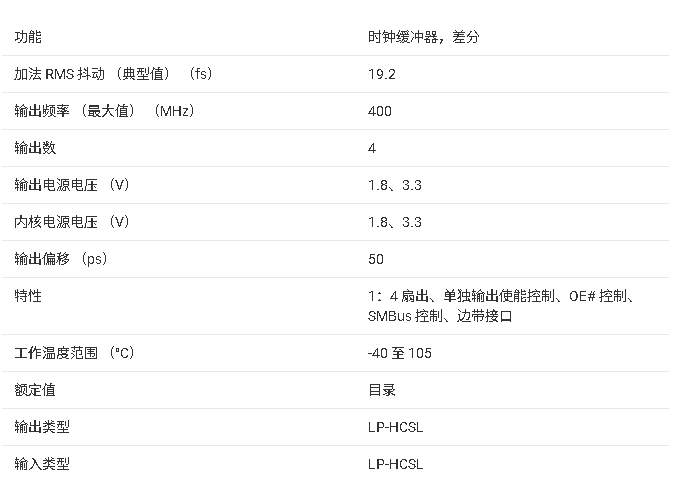

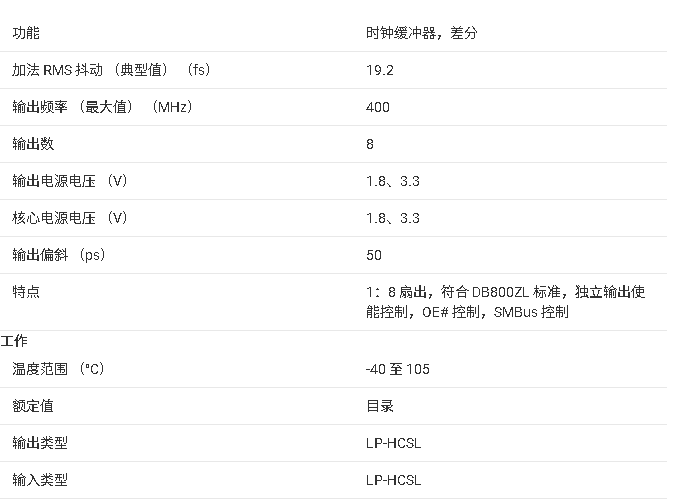

2-LP-HCSL比较

LPHCSL(Low-Power HCSL)是为了降低传统的HCSL驱动器的功耗而开发的。采用推-拉(push-pull)电压驱动,电流消耗大约4到5mA。

LP-HCSL输出功能与幅值对比

HCSL与LP-HCSL端接方式:

LP-HCSL直连即可,少了四个电阻效率高,速度快,支持AC耦合。

-

驱动器

+关注

关注

54文章

9012浏览量

153282 -

电阻器

+关注

关注

22文章

4231浏览量

64933 -

耦合

+关注

关注

13文章

605浏览量

102518 -

接口

+关注

关注

33文章

9443浏览量

156108 -

时钟

+关注

关注

11文章

1953浏览量

134532

发布评论请先 登录

替代PI6C557-05B,RS2CG5705B支持PCIe3.0之4HCSL输出的时钟生成器

LMK03328使用Code Loader 4,输入25M晶振请问如何配置输出HCSL电平?

CDCDB400 HCSL时钟作为输入是否支持?缓冲器的输出是否支持HCSL的设备?

27MHz HCSL晶体振荡器选型与PHY对接设计指南

差分逻辑电平,LVDS、xECL、CML、HCSL/LPHCSL、TMDS等

求助LVDS电平转HCSL的转换电路

求分享符合LS1028A要求的任何HCSL部件

I/O接口标准解析系列教程(3):HCSL和LPHCSL

核芯互联推出全新20路LP-HCSL差分时钟缓冲器CLB2000

HCSL基本电路结构及其相互转换

MG7050HAN 基于声表的差分多输出 晶体振荡器(HCSL)

LMKDB1120和LMKDB1108超低抖动PCIe第1代到第6代LP-HCSL时钟缓冲器数据表

LMKDB1104 用于 PCIe Gen 1 至 Gen 7 的 4 输出 LP-HCSL 时钟缓冲器技术手册

LMKDB1108 用于 PCIe Gen 1 至 Gen 7 的 8 输出 LP-HCSL 时钟缓冲器技术手册

HCSL与LP-HCSL的比较分析

HCSL与LP-HCSL的比较分析

评论