前面小编对纯软件性能分析的理论与实践的分享,希望给大家找到了豪华待遇的感觉。当然了,自己当土豪爽一下也就过去了,但是性能的问题还摆在那里等待解决,接下来怎么办呢?

改善性能可以改进代码的写法或算法,这就要结合实际问题,各显神通了。但毕竟大牛人是来仰望的,咱们还需要更加立竿见影的招数,那就是给CPU占用最大的一些函数提供VIP的待遇,把它们放在VIP区中——执行性能更高的存储器。

以前介绍性能分析时曾提到,VIP区其实也是分等级的。不同的单片机,在存储器的设计,总线连接方式,访问控制策略都各有特色,对性能的影响也不一而足。嵌入式和IoT的开发,处处彰显出碎片化和粉末化的特色,这可让人怎么整?

幸好,即使世界这么纷纷扰扰,还是有大类可循的。小编也试着结合NXP的LPC54000系列和i.MX RT1050系列,给各类VIP区分了5类VIP特权等级。

VIP:C级(小V)

这主要是针对外置QSPI Flash的升级。

对于LPC540xx和LPC18x0/43x0系列,它们没有内置Flash。如果跑不动了,可以考虑升级到其对应的有内置Flash的pin2pin型号,比如LPC546xx,LPC18xx/43xx(尾号非0)。内置Flash跑血常规(CoreMark)的性能一般在外置QSPI的1.5倍以上,对于查表较多的程序甚至在数倍以上。内部Flash的带宽往往在128位甚至256位,还带有专用于加速循环结构的特制小cache,执行程序的性能还是很棒的。

为了呈现更高的性价比,i.MX RT系列全部没有内置Flash。不过,i.MX RT的FlexSPI支持高性能的DDR模式、双Flash交火、以及8线Flash模式。就拿EVK上的hyper flash为例,可高达332MB/s,而一般的QSPI Flash通常不过60MB/s。此外,i.MX RT的SEMC对于从SDRAM执行代码的性能也比较给力,如果系统中存在SDRAM,也可以使一些数据表和代码放在SDRAM中。

VIP:B级(中V)

各型Flash和SDRAM对于小循环体的性能尽管还可以,但是当程序跳转不规则,或者顺序结构较长时,以及数据访问随机性强时,性能的表现就变得很不均匀,让人有“虽然我表达不了太多的爱,唯有好多眼泪流出来”的感觉。

这个时候,可以使用单片机片上的系统RAM。对于LPC54系列的Cortex-M4/M0+单片机,可以放在内存地址为0x2000-0000开头的RAM中,对于i.MX RT系列则是地址为0x2020-0000的OCRAM中。这些RAM的工作频率和随机访问性能比Flash好得很多。但是因为在这个地址范围使用的AHB (LPC)或AXI (i.MX RT)系统总线的启动时序开销大,总线往往又比较忙,还要和诸多带DMA的总线主机抢带宽,性能加速可能得不到保证,因此充其量也就算是中V级吧。

VIP:A级(大V)

和中V级相比,大V的待遇就更好了,有了专属的紧密耦合RAM区。

以LPC5411x为例,它有32KB的”SRAMX”,这块SRAMX和192KB的全部容量相比只占1/6,但绝对配得上大V的待遇。它直接连接到Cortex-M4的I-Code和D-Code总线上。这两条总线也是“特供”于快速代码执行的绿色通道,其它总线主设备是没资格用的。

再看i.MX RT,它的Cortex-M7内核更是有过之而无不及,把I-Code和D-Code升级到64位的ITCM(指令紧密耦合存储器)和DTCM(数据紧密耦合存储器),并且片上的512KB内存可以自由分割,全部配置成ITCM和DTCM也可以。那没有了其它RAM,外设要访问怎么办呢?Cortex-M7留了个小后门——AHB-Slave给其它DMA主机访问TCM,当然是看M7脸色行事。

总之,大V待遇对于大多数程序代码已经相当有面儿了,性能提升也是杠杠的!

VIP:S级(超V)

啥,还有超V级?难道还有比TCM更快的,莫非小编你疯到想把R0-R14也给卖了?

倒也不是,超V级其实可以看作是上述VIP的组合,给最关键的模块提供服务,占用多块RAM。比如一个压缩jpeg的模块,它既有代码又有只读数据。如果把代码与只读数据全放在一块RAM,就不能发挥M4/M7双总线的优势,比如没法取指令的同时访问数据。小编于是把代码放ITCM,只读数据放DTCM,相当于它自己左手一个右手一个拥抱了整个芯片中性能最强的两块RAM,让600MHz的M7火力全开,跑到QVGA分辨率下60帧每秒以上的图片压缩性能。

VIP:PS级(公共超V)

(仅适用于Cortex-M7)

在Cortex-M7内核的i.MX RT系列中,支持指令高速缓存(I-Cache)和数据高速缓存(D-Cache),各有32KB。这两个Cache的性能完全是TCM级别的。这是一项超V级水准的平民福利,献给全部没有享受到大V和超V待遇的代码和数据,就称作公共超V级吧。

有趣的是,它是全自动的——不管是什么代码和数据,上镜率越高,就越有机会多享受超V级待遇。但若是如果什么时候起受冷落了,就最终会被扫出门。

打个不严谨的比方,这就好比假设高铁中以商务座的标准建餐车,即使没买一等座和商务座,只要抢到了餐车座席吃饭,吃饭期间也享受商务座待遇。只不过,若是吃完饭想再歇会,又没空位子了,那就祈祷别人不要来吃饭吧,否则就会被赶走。

因此,这项复用型超V待遇是按需分配的。值得注意的是,在替换cache内容时会花时间,既对确定性产生影响,也降低平均性能。所以虽然比超V级弱一点,但它把福利普照给公众,这是前面任何VIP特权也提供不了的。

审核编辑:刘清

-

嵌入式

+关注

关注

5209文章

20657浏览量

337071 -

FlaSh

+关注

关注

10文章

1759浏览量

155904 -

存储器

+关注

关注

39文章

7756浏览量

172199 -

QSPI

+关注

关注

0文章

55浏览量

13402

原文标题:VIP也分高低——存储器对执行性能的影响

文章出处:【微信号:pzh_mcu,微信公众号:痞子衡嵌入式】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

怎么做高低温试验?高低温试验有哪些内容、方法和标准?

如果手机高低温测试不到位,你敢用吗?手机高低温测试要做些什么

高低温试验怎么做?有哪些功能、设备和标准?

维信诺召开ViP智能像素化技术成果研讨鉴定会

机场气源机为什么要做高低温试验?-40℃到+55℃的生存挑战

高低温试验是什么?测试标准有哪些?

评选十大高低温试验箱有哪些标准?高低温试验箱厂家性价比怎么看?

芯原NPU IP VIP9000NanoOi-FS获ISO 26262 ASIL B认证

高低压隔离器:电力网络的可靠防线

高低温循环测试对电子元件寿命有什么影响

普科差分探头PKDV5151助力客户完成高低压电机驱动波形测量

激光焊接技术在焊接高低压断路器工艺中的应用

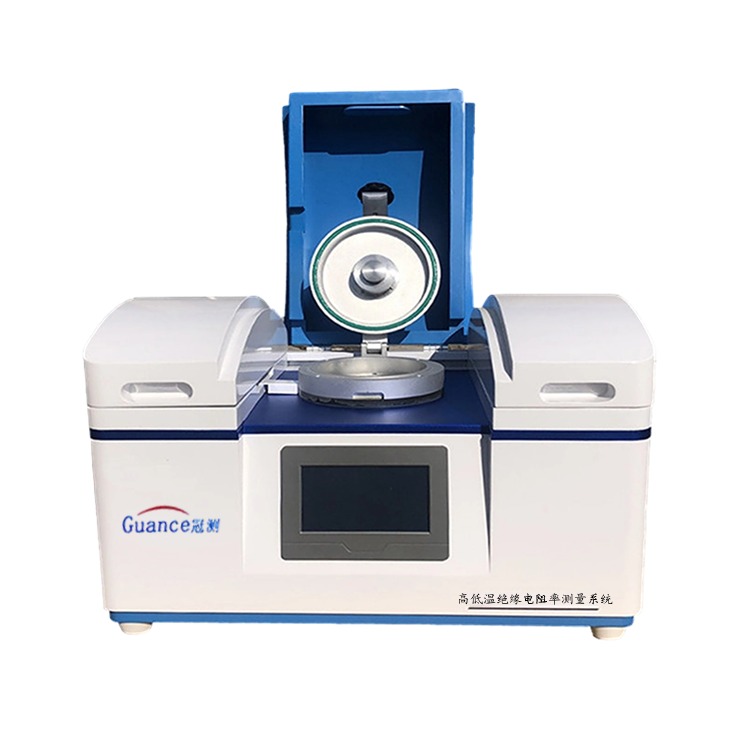

高低温绝缘电阻率测量系统:原理、应用与测试技巧

VIP也分高低?

VIP也分高低?

评论