Vitis AI 是AMD 开发套件,用于在 AMD 硬件平台上进行 AI 推断。机器学习中的推断是计算密集型流程,需要大量存储器带宽以满足各种应用的低时延和高吞吐量要求。

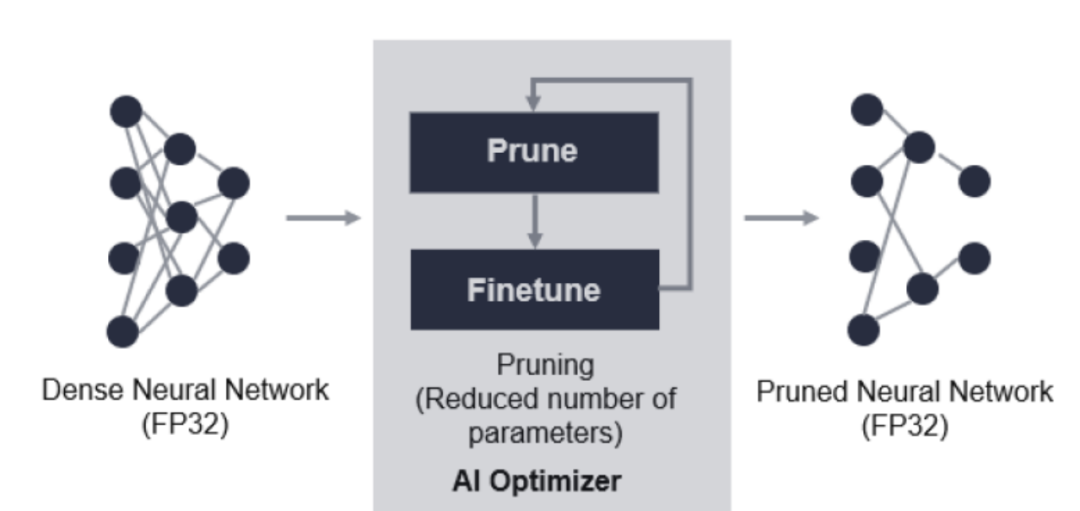

Vitis AI Optimizer(优化器)支持对神经网络模型进行最优化。当前,Vitis AI 优化器仅包含一项工具,称为“pruner”(剪枝器)。Vitis AI 优化器用于移除神经网络中的冗余内核,从而减少推断的总体计算成本。由 Vitis AI 剪枝器所生成的剪枝后的模型随后由 Vitis AI 量化器进行量化,然后部署到 AMD FPGA、SoC 或 ACAP 器件。

VAI优化器

本文档涵盖了以下设计进程:机器学习和数据研究——将机器学习模型从 PyTorch、TensorFlow 或其它热门框架导入 Vitis AI,然后对其有效性进行最优化和评估。本文档中适用于此设计进程的主题包括:

•第 2 章:剪枝

•第 3 章:处理 Vitis AI 优化器

由于版面有限,本文选取了剪枝章节中的部分内容进行分享。如果您希望获取完整版用户指南,请至文末扫描二维码下载完整版进行浏览。

剪枝

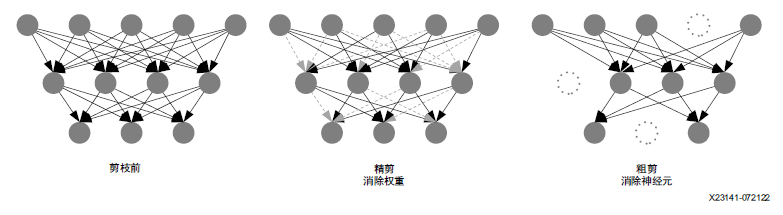

神经网络通常过度参数化,具有大量冗余。剪枝是消除冗余权重同时尽可能使准确度损失保持处于低位的进程。

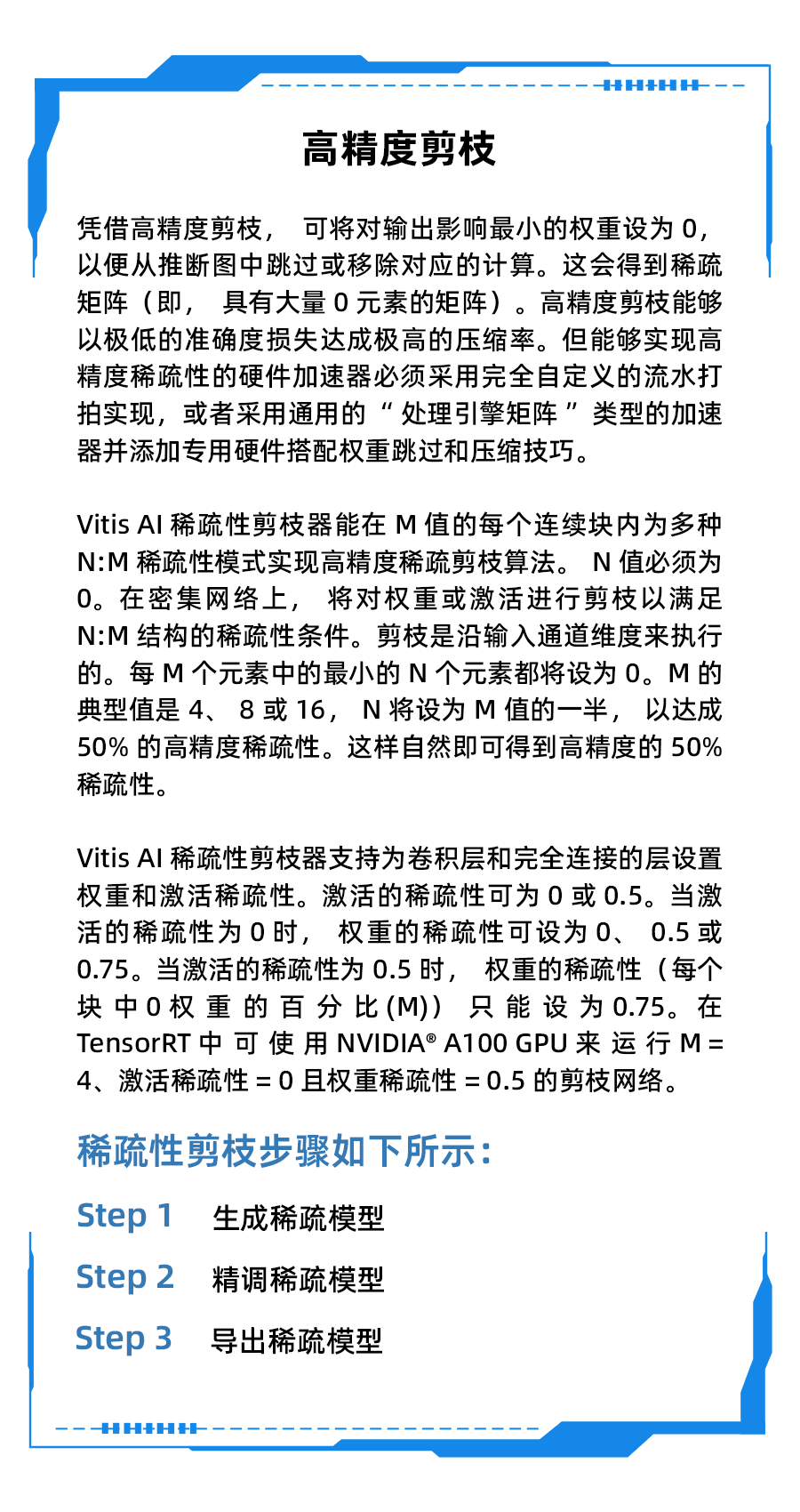

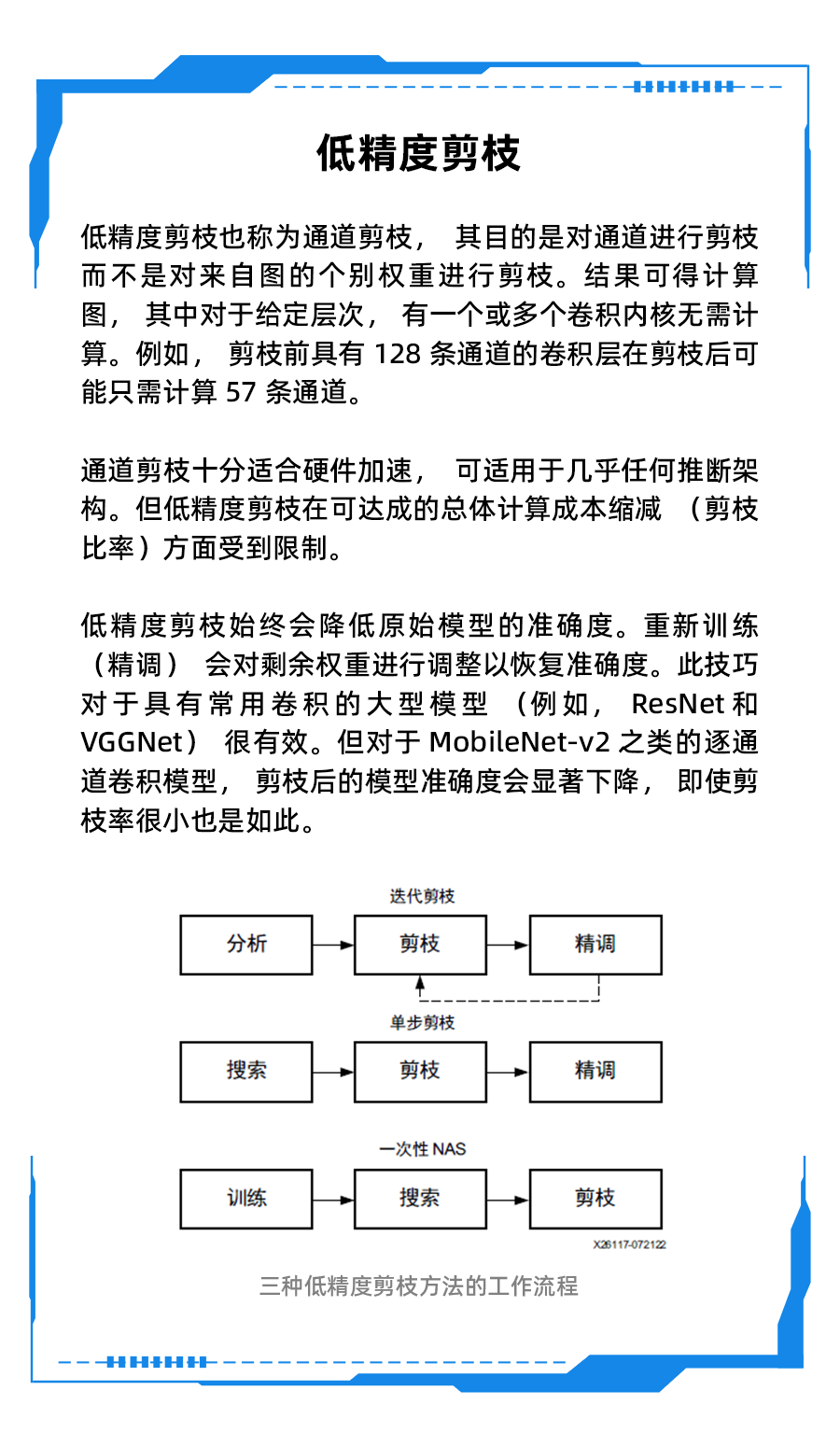

低精度剪枝和高精度剪枝

行业研究带来了多项有助于降低神经网络推断成本的技术。这些技术包括:

点击查看详细内容

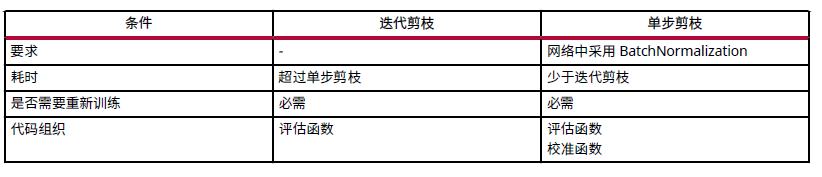

迭代剪枝与单步剪枝的对比

下表中显示了这两种方法的对比。

迭代剪枝

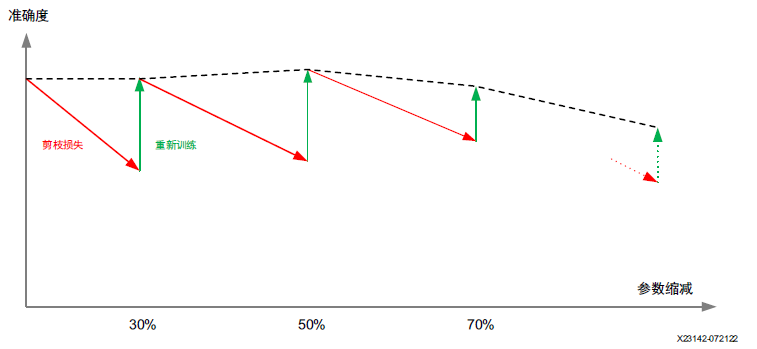

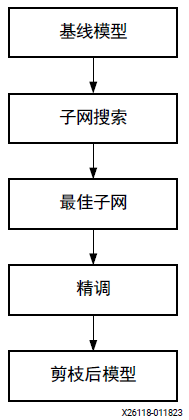

剪枝器旨在减少模型参数数量,同时尽可能降低准确度损失。这是通过迭代方式来完成的,如下图所示。剪枝导致准确度降低,重新训练可恢复准确度。剪枝随后重新训练即构成一次迭代。在剪枝的首次迭代中,输入模型是基线模型,并且已经过剪枝和精调。在后续迭代中,从先前迭代所获取的精调后的模型会变为新的基线。此进程通常会重复数次,直至获取期望的稀疏模型。迭代方法是必需的,因为在单次传递中无法在维持准确度的同时进行模型剪枝。如果一次迭代移除的参数过多,那么准确度损失可能过于剧烈,可能无法恢复。

利用迭代剪枝的进程,可以达到更高的剪枝率,同时模型性能不会出现显著损失。

迭代剪枝

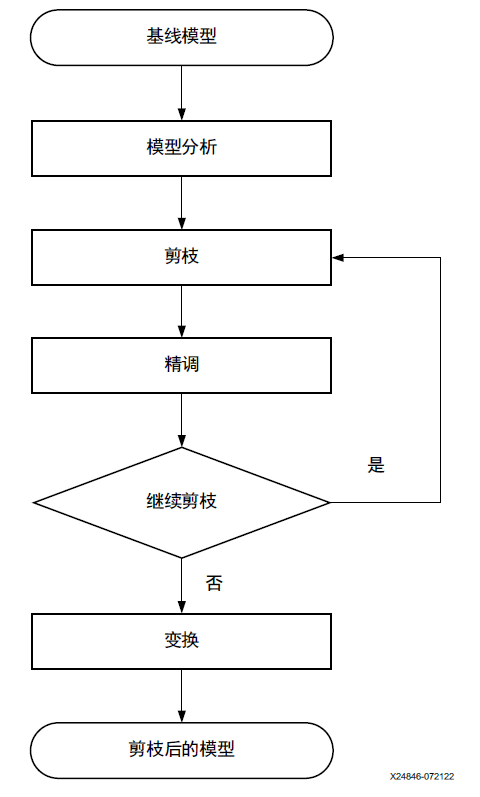

以下描述了迭代剪枝的 4 个主要阶段:

分析:对模型执行敏感度分析,判定最优剪枝策略。

剪枝:减少输入模型中的计算次数。

精调:重新训练已剪枝的模型以恢复准确度。

变换:生成含更低权重的密集模型。

迭代剪枝工作流程

步骤1

分析原始基线模型。

步骤2

对模型进行剪枝。

步骤3

对剪枝后的模型进行精调。

步骤4

多次重复步骤 2 和 3,直至在准确度与稀疏度之间达成期望的平衡。

步骤5

将剪枝后的稀疏模型变换为最终密集加密的模型,以供在 Vitis AI 量化器中使用。

单步剪枝

单步剪枝会实现EagleEye1算法。它仅通过采用了一个简单而又高效的评估组件,就得以在不同的已剪枝模型及其对应精调准确度之间引入强大的正关联,这个组件名为自适应批量归一化。它使您无需实际进行模型精调,即可获取可能达成的准确度最高的子网络。简而言之,单步剪枝方法会搜索一群满足所需模型大小的子网络(即,生成的剪枝后模型),并选择其中最有潜力的子网络。随后,通过对所选子网络进行重新训练来恢复准确度。

| 剪枝步骤如下所示: | |

| 1 | 搜索满足所需剪枝率的子网络。 |

| 2 | 从一群具有评估组件的子网络中选择潜在网络。 |

| 3 | 对剪枝后的模型进行精调。 |

单步剪枝工作流程

注释:

1.Bailin Li et al., EagleEye: Fast Sub-net Evaluation for Efficient Neural Network Pruning, arXiv:2007.02491

剪枝方法的选择指南

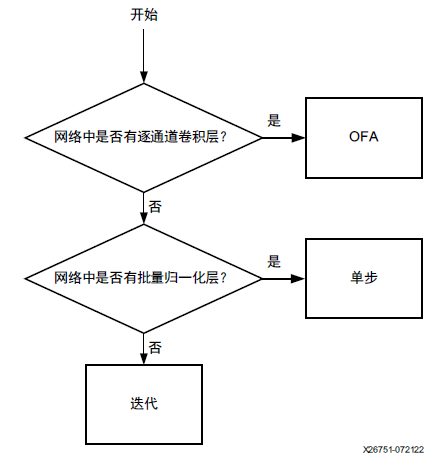

Vitis AI 优化器中为 PyTorch 提供了 3 种剪枝方法。请参阅以下决策树以选择适合您的网络的方法。

在PyTorch中选择剪枝方法的流程图

审核编辑 :李倩

-

神经网络

+关注

关注

42文章

4842浏览量

108184 -

模型

+关注

关注

1文章

3819浏览量

52272

原文标题:Vitis AI 优化器用户指南

文章出处:【微信号:赛灵思,微信公众号:Xilinx赛灵思官微】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Microchip TC1303B双输出稳压器用户指南详解

AI端侧部署开发(SC171开发套件V2-FAS)

AI端侧部署开发(SC171开发套件V3)2026版

基于Vitis Model Composer完成全流程AI Engine开发

全新AMD Vitis统一软件平台2025.2版本发布

如何在AMD Vitis Unified IDE中使用系统设备树

AMD Vitis AI 5.1测试版现已开放下载

AMD Vitis AI 5.1测试版发布

AI赋能6G与卫星通信:开启智能天网新时代

从何处获取 CYBLE-416045-02 用户指南?

全新AMD Vitis统一软件平台2025.1版本发布

使用AMD Vitis Unified IDE创建HLS组件

如何使用AMD Vitis HLS创建HLS IP

Vitis AI优化器用户指南

Vitis AI优化器用户指南

评论