1 运行平台

硬件:CRD500数字信号处理板

系统:win7/64;win7/32;win10/64

软件:Quartus/ModelSimSE/Verilog/Matlab

2 主要功能及性能指标

3.2.1主要功能

1)产生基带原始数据

2)帧同步信号提取

3.2.2主要性能指标

1) 发送端

系统时钟:50MHz

基带数据码率:195.3125kbps

数据内容:帧长16位,帧同步字长7位,同步字为1011000

2) 接收端

系统时钟:发送端送来的数据时或信号,195.3125kbps

同步方式:具有搜索、校验、同步三种状态:帧长、帧同步字、搜索容错位数、校核容错位数、同步容错位数可通过修改程序参数快速设置。

3 程序结构框图说明

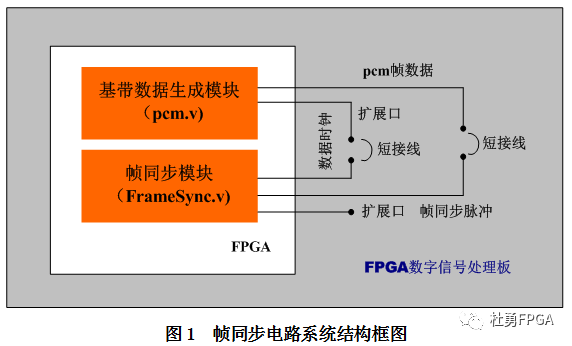

帧同步电路系统主要由基带数据生成模块(pcm.v)、帧同步模块(FrameSync.v)模块组成。

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

数字信号处理

+关注

关注

16文章

580浏览量

47898 -

系统时钟

+关注

关注

1文章

32浏览量

10236 -

帧同步系统

+关注

关注

0文章

2浏览量

5922

原文标题:插值法帧同步(Quartus/Verilog/CRD500)

文章出处:【微信号:杜勇FPGA,微信公众号:杜勇FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

基于LabVIEW的心电信号插值算法分析

为了在LabVIEW平台下更方便的处理非均匀采样的心电信号,文中研究了心电信号的时域和频域插值算法。首先采用了拉格朗日插值法、牛顿

发表于 03-15 17:10

•61次下载

插值法帧同步ISE/Verilog/CXD301介绍

同步方式:具有搜索、校验、同步三种状态:帧长、帧同步字、搜索容错位数、校核容错位数、同步容错位数

插值法帧同步(ISE/Verilog/CXD301)

基带数据生成模块生成的原始数据(1.5625Mbps)送至开发板上扩展口,经短接线由第35脚送回FPGA芯片;数据生成的同步时钟信号也经扩展口硬件环回至帧同步模块。为便于测试环路同步及

基于事件相机的统一帧插值与自适应去模糊框架(REFID)

)的解决方案。团队提出了一种基于事件相机的统一帧插值与自适应去模糊框架(REFID)。该框架基于双向递归网络,结合事件流和图像信息,自适应地融合来自不同时间点的信息,从而能够在模糊的输入帧

插值法帧同步解析

插值法帧同步解析

评论