最新有客户在询问soc的片上RAM启动方案。于是有了本篇文章。如果soc不使用外部存储而是使用片上RAM的话,文档上似乎没有给出详细的说明,那这里我们就来介绍一下。

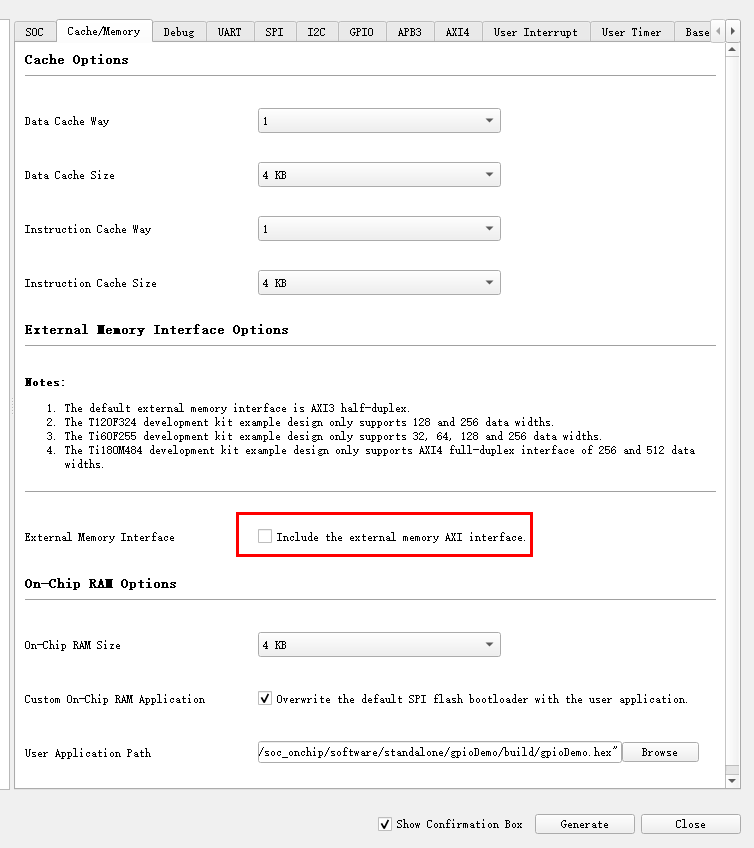

首先片上RAM启动要在IP上关闭外部存储,如下图,Include the external memory AXI interface。

这里要说,on chip RAM的启动方式与外部存储方式的启动方式有个很大的区别就是不需要bootloader从flash中搬运数据到存储器。on chip RAM启动方式不需要bootloader或者说应用程序就是bootlaoder。

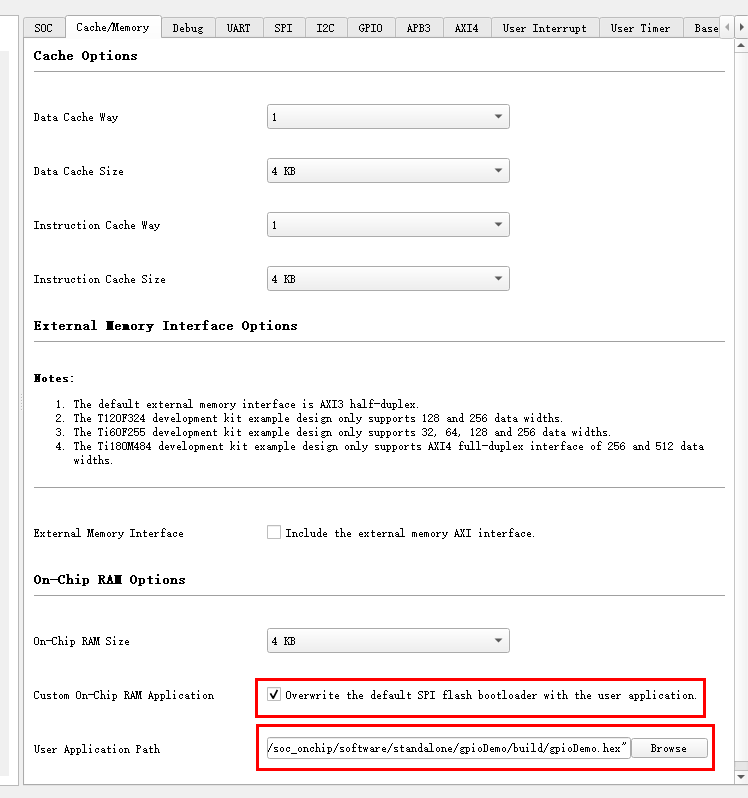

另外,在新版本的sapphire IP中,已经支持把应用程序的hex文件直接添加到IP,相对于老的版本来说方便了很多。这时只需要勾选Overwrite the default SPI flash bootloader with the user application并且在User Application Path中添加用户程序生成的hex文件即可。

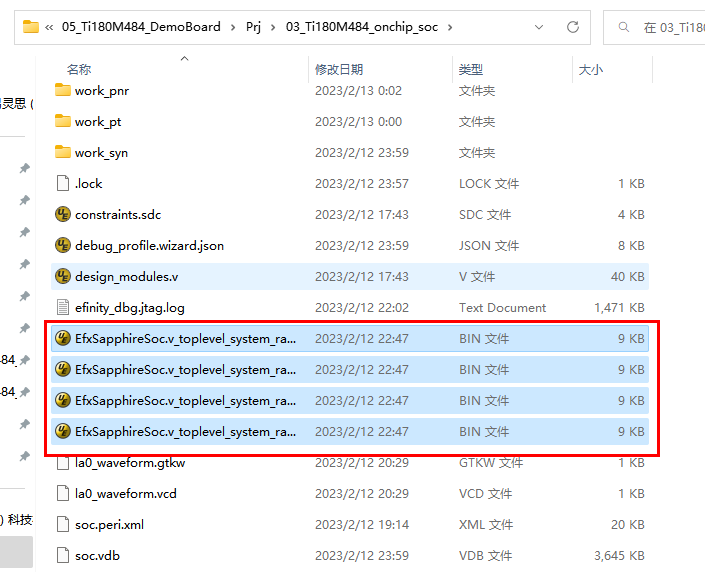

但是这样重新编译之后可能不能运行。因为soc RAM的初始化文件默认是工程目录下的bin文件,所以最好把这个工程目录下的bin文件先删除掉,然后再重新编译。当然也可能是别的原因,先不必深究。

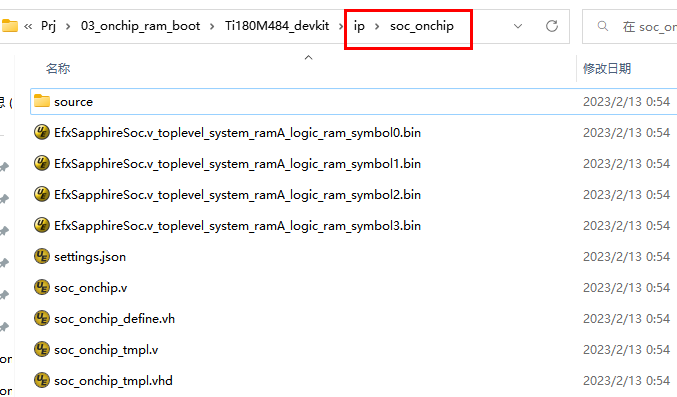

在生成IP的过程中应该是把hex文件转换成了4个bin文件,与IP同一个目录。所以每次修改程序并生成hex之后,都要打开IP重新生成IP,这时才会重新生成bin文件。

这样之后重新编译就可以了。

有一个问题:我们每次修改RISCV的工程,重新生成hex文件。都需要重新编译工程,这是很耗时的。所以需要一个办法把修改后的hex——也就是RAM的初始化文件使用一个简单的方法合成bit文件,以避免重新编译。这个方案需要晚点提供。

审核编辑:刘清

-

RAM

+关注

关注

8文章

1400浏览量

120975 -

soc

+关注

关注

40文章

4621浏览量

230088 -

Flash存储

+关注

关注

0文章

40浏览量

8621 -

BIN文件

+关注

关注

0文章

27浏览量

9052 -

易灵思

+关注

关注

6文章

66浏览量

5578

原文标题:易灵思SOC onchip RAM启动操作

文章出处:【微信号:gh_ea2445df5d2a,微信公众号:FPGA及视频处理】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

易灵思FPGA产品的主要特点

易灵思SOC的片上RAM启动方案

易灵思SOC的片上RAM启动方案

评论