USB3.0和USB2.0相比,在线缆上从4根线(Vbus、GND、D+、D-)变为了8根线(Vbus、GND、D+、D-、SSRX+SSRX-SSTX+SSTX-),可见增加的4根线都是和超速相关的,新增加的超速有两类,分别为:超速Gen 1(5.0 Gbps), 超速+Gen 2(10 Gbps),还兼容USB2.0的3类速率:low-speed (1.5 Mbps), full-speed (12 Mbps), and high-speed (480 Mbps)。从设计可以看出,USB3.0的重点解决的问题是速率,最高10Gbps。

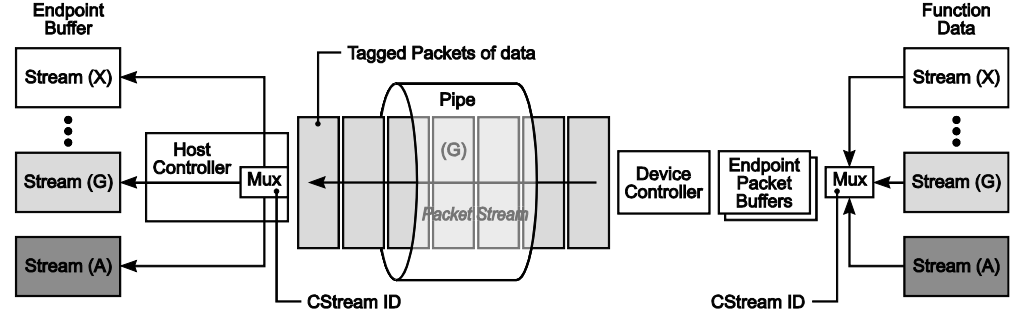

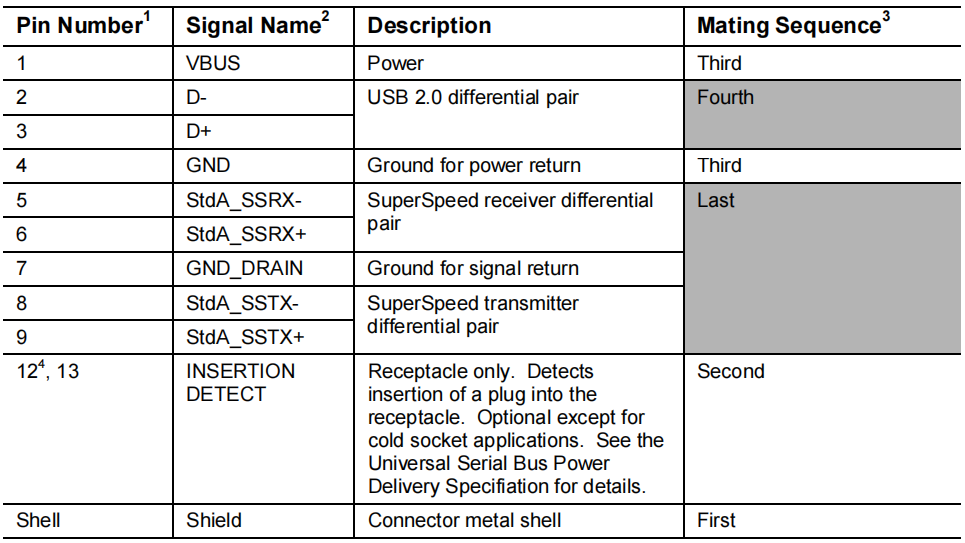

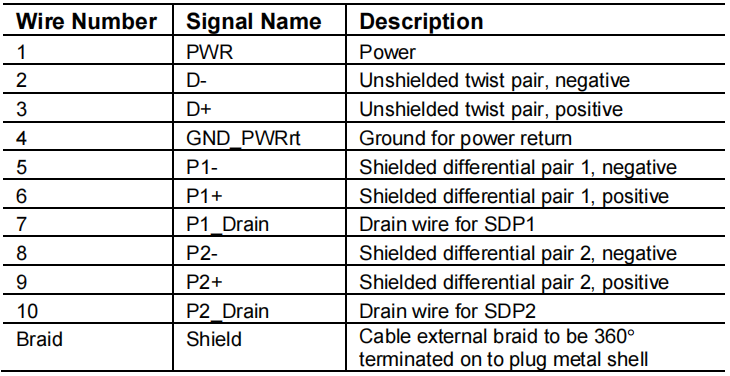

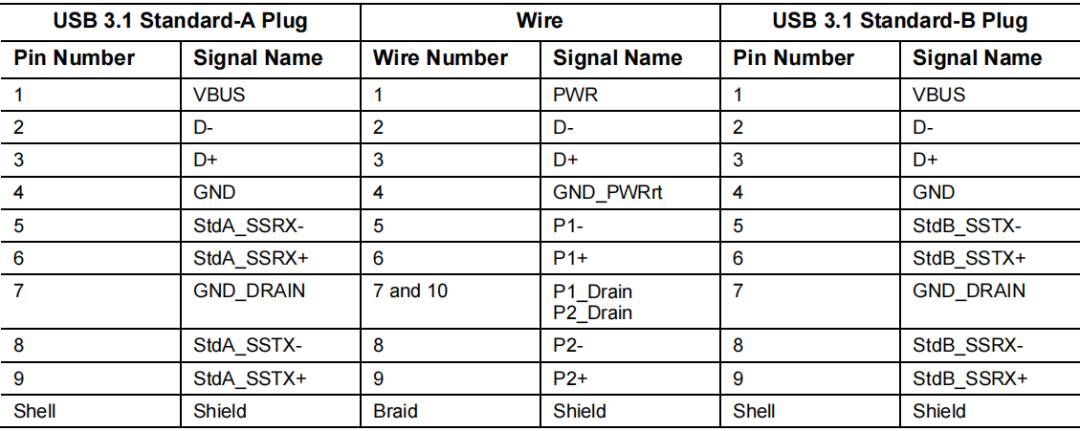

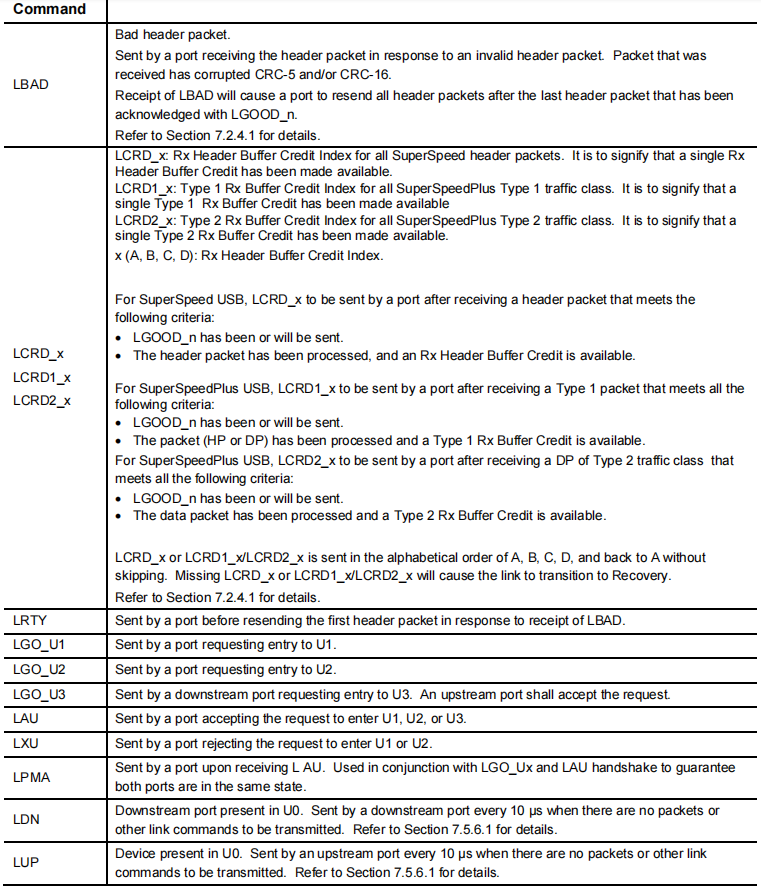

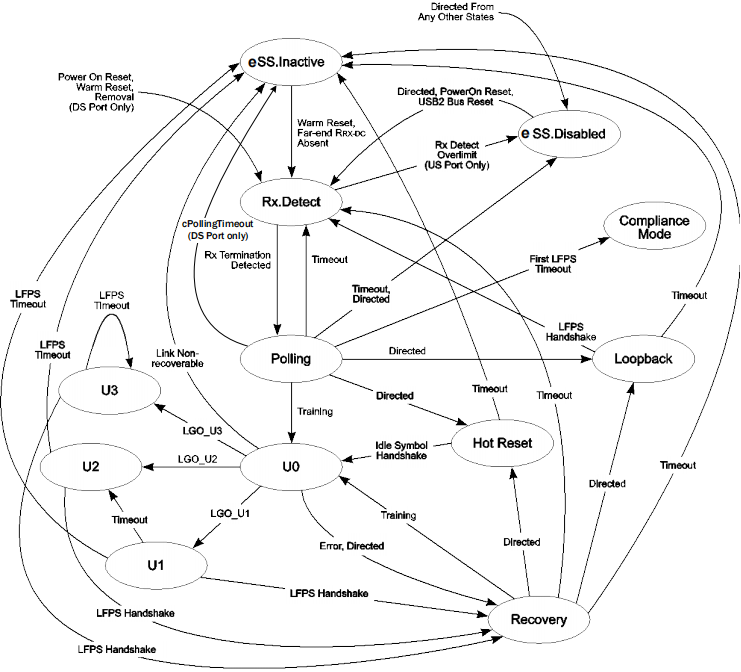

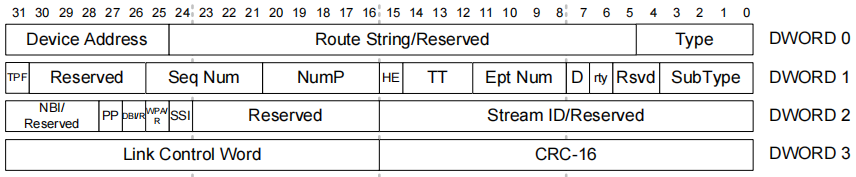

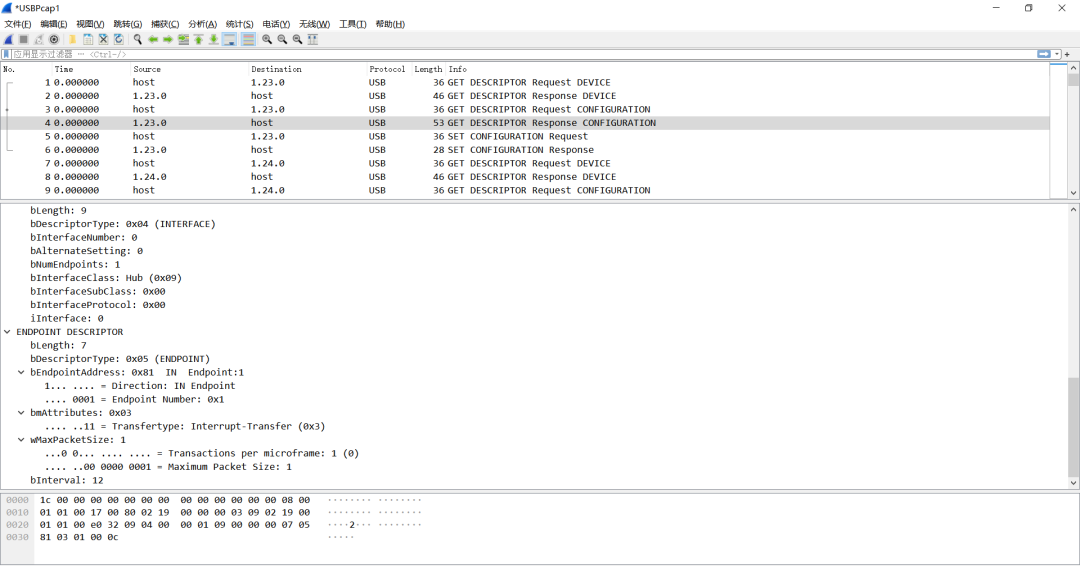

所有增强的超高速设备都与USB2.0共享它们的基本架构。通信模型视图保留了USB2.0分层架构和通信流的基本组件(即,点对点、相同的传输类型等)增强的超高速协议提供了在主机和设备端点之间的应用程序数据信息交换。这种通信关系被称为管道。它是一个主机导向的协议,这意味着主机决定何时在主机和设备之间传输。增强的超高速协议不是一个轮询的协议,因为设备能够代表特定的端点从主机异步请求服务。所有协议层通信都是通过包交换来完成的。数据包是具有特定控制序列的数据字节序列,它们作为由链接层管理的分隔符。主机传输的协议包通过中间集线器直接路由到外设设备。它们不遍历不属于主机和目标外围设备之间的直接路径的一部分的总线路径。- USB2.0使用三部分事务(令牌、数据和握手),而增强的超高速协议使用相同的三个部分则不同。对于OUTs,令牌将被合并到数据包中;而对于INs,令牌将被握手替换。- USB2.0不支持bursting,而增强的超高速协议支持连续bursting。- USB2.0是一个半双工广播总线,而增强的超高速总线是一个双单工单播总线,它允许并发的IN和OUT事务。-- USB2.0使用了一个轮询模型,而增强的超高速协议则使用了异步通知。- USB2.0没有流媒体功能,而增强的超高速协议支持批量端点的流媒体功能- USB2.0以固定的1ms/125μs的间隔传输SOF/uSOF,具有非常严格的持续时间和抖动规范。增强的超速度链路也有一个类似的机制,称为等时时间戳包(ITP),它由主机传输。USB主机可以在从总线间隔边界的放松定时窗口内发送同步时间戳包(ITP)。USB3.0增加了一种机制,供设备发送总线间隔调整消息,主机用来将其125μs总线间隔调整至+/-13.333μs。一个设备可以通过较小的有限调整来改变时间间隔。- USB3.1为以Gen1速度运行的主机和集线器定义了一个可选的规范,并且需要以Gen2速度运行的主机和集线器,为增强的超高速设备提供精密时间测量(PTM)能力,使主机、集线器和设备能够通过USB拓扑准确地确定传播延迟。- USB2.0电源管理,包括链路电源管理,总是由主机直接启动。增强的超高速总线支持链路级电源管理,可以从链路的两端启动。因此,每个链路都可以独立地进入低功耗状态数据包有四种基本类型:链接管理数据包LMP、事务数据包TP、数据数据包DP和同步时戳数据包ITP。发送到接收方的每个非等时数据包都通过握手(称为ACK事务包)进行确认。然而,由于增强的超高速总线具有独立的传输和接收路径,发射机不必在发送下一个数据包之前等待所传输的每个数据包的显式握手。增强的超高速总线保留了USB2.0中定义的所有基本数据流和传输概念,包括传输类型、管道和基本数据流模型。这本质上意味着主机在开始下一个事务之前启动并完成一个总线事务{令牌、数据、握手}。拆分事务也遵循相同的模型,因为它们由完整的高速事务{令牌、数据、握手}组成,这些事务在与所有其他事务在相同的模型下完成。增强的超高速协议通过使用独立的传输和接收路径,改进了USB2.0事务协议。其结果是,增强的超高速USB事务协议本质上是一个分割事务协议,通常允许在总线上同时有多个IN或OUT总线事务活动。请注意,一个超高速链接有一个限制,最多有一个在“总线事务”可以在该超高速总线实例上激活。分割事务协议可以很好地扩展到(跨多个事务到多个函数端点),因为它不受传播延迟的影响。USB2.0协议在继续到下一个预定功能端点的下一个总线事务之前,先完成整个IN或OUT事务{令牌、数据、握手}。所有来自主机的传输基本上都在USB2.0总线上广播。相比之下,增强的超速度协议不广播任何数据包(ITPs除外),而数据包只遍历到达预期收件人所需的链路。主机通过发送握手或数据来启动所有事务,设备以数据或握手进行响应。如果该设备没有可用的数据,或不能接受该数据,它会响应一个数据包,声明它不能这样做。随后,当设备已经准备好接收或传输数据时,它会向主机发送一个通知,表明它已经准备好恢复事务。此外,增强的超高速总线提供了转换链接到和退出特定的低功率状态的能力。低功率链路状态在被软件启用后,可以在软件控制或自主硬件控制下输入。- Interrupt Transfers中断传输- Isochronous Transfers异步传输接口形式有Standard-A、Standard-B、Micro-B、Micro-A、Micro-AB接口如下:USB3.1 Standard A到USB3.1 Standard B的连接如下:Gen 1采用8b/10b K-Code编码,Gen 2采用128b/132b编码。包的帧格式、链路指令、链路初始化和流控制、错误检测与控制、复位。U1:一种低功率状态,不传输数据包,两个端口都同意进入一个链路状态,其中一个增强的超高速PHY可以置于低功率状态。U2:一种链接状态,与U1相比,允许有更多的节能机会,但退出延迟增加U3:一种使设备处于暂停状态的链路状态。保存了重要的链路和设备电源。Recovery:恢复链路状态,以重新训练链路,或执行热重置,或切换到回载模式。Loopback:可用于测试和故障隔离。回载功能包括一个位误码率测试(BERT)状态机这一层建立在链路层保证头数据包交付的假设之上,并且该层根据传输类型增加了其余数据包的端到端可靠性。如果没有特别说明,则要求协议层同时适用于超高速和超高速+架构。- Link Management Packets (LMP): + Port Configuration Response + Precision time Measurement- Transaction Packets (TP)- Isochronous Timestamp Packets (ITP)对于USB协议,可以通过WireShark抓取通信数据包:

欢迎关注至芯科技

至芯官网:www.zxopen.com

至芯科技技术论坛:www.fpgaw.com

至芯科技淘宝网址:

https://zxopen.taobao.com

至芯科技FPGA初级课程(B站):

https://space.bilibili.com/521850676

至芯科技FPGA在线课程(腾讯课堂):

https://zxopenbj.ke.qq.com/

至芯科技-FPGA 交流群(QQ):282124839

更多资料下载欢迎注册http://www.fpgaw.com

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

FPGA学习-USB 3.0协议理解

FPGA学习-USB 3.0协议理解

评论