数字门级电路可分为两大类:组合逻辑和时序逻辑。锁存器是组合逻辑和时序逻辑的一个交叉点,在后面会作为单独的主题处理。

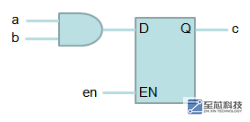

组合逻辑描述了门级电路,其中逻辑块的输出直接反映到该块的输入值的组合,例如,双输入AND门的输出是两个输入的逻辑与。如果输入值发生变化,输出值将反映这一变化,组合逻辑的RTL模型需要反映这种门级行为,这意味着逻辑块的输出必须始终反映该逻辑块当前输入值的组合。

SystemVerilog有三种在可综合RTL级别表示组合逻辑的方法:连续赋值语句、always程序块和函数。接下来几篇文章将探讨每种编码风格,并推荐最佳实践编码风格。

always和always_ff

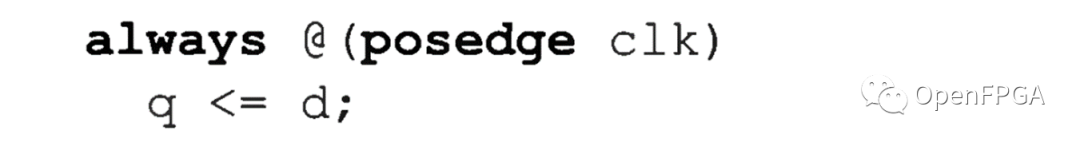

通用的always程序可以用来为任何类型的逻辑建模,包括组合逻辑、时序逻辑(触发器)和电平感应的时序逻辑(锁存器)。为了让通用的always程序对触发器行为进行建模,always关键字后面必须紧跟一个敏感度列表,指定时钟信号的posedge或negedge,如:。

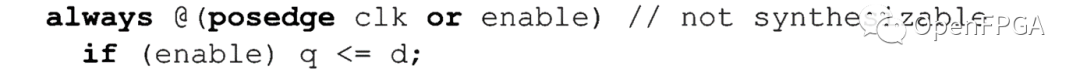

尽管这个例子在功能上是准确的,但是通用的always程序并不要求也不强制执行前面一节中列出的任何综合要求。下一个例子在语法上是合法的,但是不可综合。

这个例子可以在仿真中编译和运行,没有任何警告或错误提示,但是综合编译器在试图编译这个例子时,会报告一个错误。它不符合要求,即除了时钟和异步置位或复位的边沿之外,其他信号都不能包含在灵敏度列表中。对RTL仿真的仔细验证会发现,即使在没有发生时钟触发的情况下,触发器的状态也会在每次enable改变值时更新其内部存储。门级的触发器没有这个功能。

always_ff过程也需要一个敏感度列表,指定一个时钟的posedge或negedge,但是always_ff也执行上一节中列出的许多综合要求。SystemVerilog标准要求所有软件工具在以下情况下报告错误。

过程的主体包含#,wait,或者@时间控制延迟时,将阻止过程的执行,直到要求的仿真时间。

在程序中,有一个对任务的调用(因为任务可以包含延迟)。

任何其他存储过程、连续赋值或输入端口的赋值与always_ff存储过程的变量相同。

IEEE标准还建议(但不要求)软件工具检查其他综合限制,如不正确的灵敏度列表。设计工程工具,如综合编译器和lint检查器(检查编码风格)执行这些可选的检查,但大多数仿真器不对always_ff程序执行额外的检查。这些错误和可选的额外检查有助于确保具有时序逻辑的RTL模型既能正确仿真,又能正确综合(仿真和综合后功能相同)。

always_ff过程之后必须有一个符合综合要求的敏感性列表。灵敏度列表不能像always_comb可以推断灵敏度列表那样从程序的主体中推断出来。原因很简单:时钟信号在always_ff过程的主体中没有命名。时钟的名称,以及时钟的哪个边沿触发了存储过程,必须由设计工程师在灵敏度列表中明确指定。

| 最佳实践指南8-1 |

|---|

| 使用SystemVerilog always_ff RTL专用存储过程来模拟RTL时序逻辑。请不要使用通用的always过程。 |

always_ff RTL专用程序强制执行上一篇文章中所要求的综合风格,以正确模拟时序逻辑行为。

审核编辑:刘清

-

锁存器

+关注

关注

8文章

747浏览量

41042 -

RTL

+关注

关注

1文章

377浏览量

59077 -

Verilog语言

+关注

关注

0文章

113浏览量

8162 -

门级电路

+关注

关注

0文章

15浏览量

1933

原文标题:数字硬件建模SystemVerilog-时序逻辑建模(2)always和always_ff

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

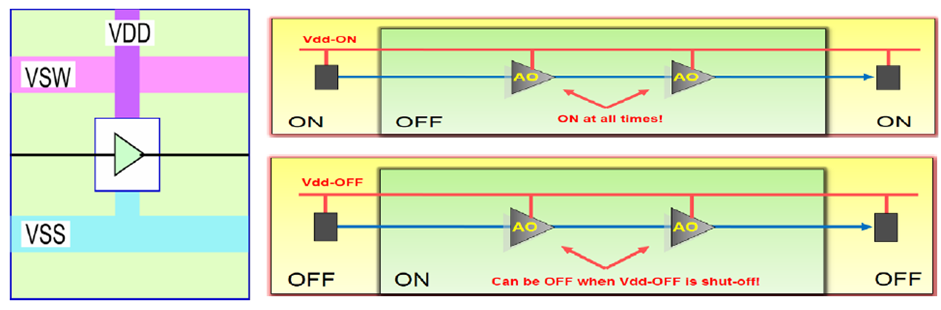

什么是always on buffer?什么情况下需要插always on buffer?

什么是AO/DI (Always On-line/Dynam

verilog中单/双/三always块状态机写法

always block內省略else所代表的電路 (SOC) (Verilog)

initial和always两者的关系分析

你们知道always,assign和always@(*)之间的区别吗

assign组合逻辑和always@(*)组合逻辑的区别

数字硬件建模SystemVerilog篇OpenFPGA介绍

SystemVerilog中的always语句块

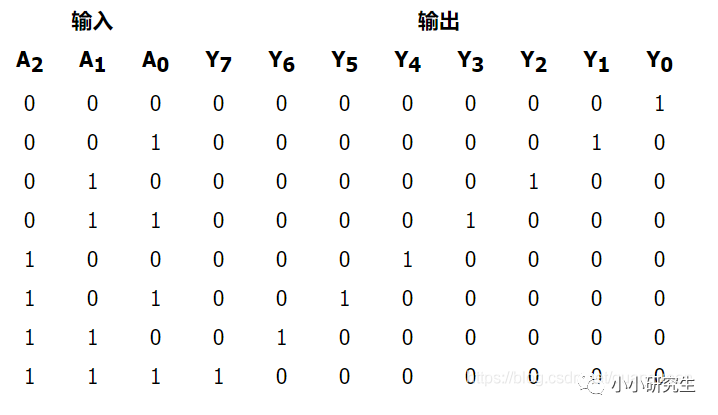

always组合逻辑块的讲解和译码器的实现

SystemVerilog相比于Verilog的优势

探讨always和always_ff的编码风格

探讨always和always_ff的编码风格

评论