Abstract

在Verilog中,always block可以用來代表Flip-Flop, Combination Logic與Latch,本文比較在不寫else下,always block所代表的電路。

Introduction

在C語言裡,省略else只是代表不處理而;已但在Verilog裡,省略else所代表的是不同的電路。

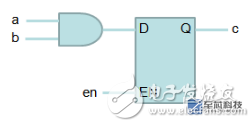

always@(a or b or en)

if (en)

c = a & b;

在combination logic中省略else,由於必須在~en保留原本的值,所以會產生latch。

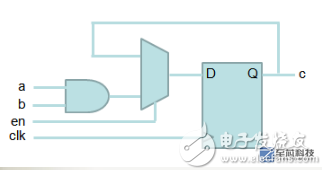

always@(posedge clk)

if (en)

c <= a & b;

雖然也必須在~en保留原本的值,但由於flip-flop就有記憶的功能,所以不會產生latch。if將產生mux,並將flip-flop的值拉回給mux。

Conclusion

在Verilog中,雖然只是小小的差異,但結果卻有天大的差異。

全文完。

-

FPGA

+关注

关注

1655文章

22288浏览量

630340

发布评论请先 登录

利用蜂鸟E203搭建SoC【1】——AXI总线的配置与板级验证

【米尔-安路MYD-YM90X 创意秀】点灯也是入门绝活

26 路触控按键和 PWM 的增强型 8051SOC RM1221A数据手册

200w开关电源__功率级电路设计总结

FPGA Verilog HDL语法之编译预处理

浅谈Verilog和VHDL的区别

数字集成电路 Verilog 熟悉vivado FPGA微电子、电子工程

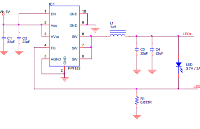

手电筒控制IC,LED手电筒驱动芯片FP7153同步降压LED驱动IC应用说明与电路设计原理

FP7153應用說明-V01

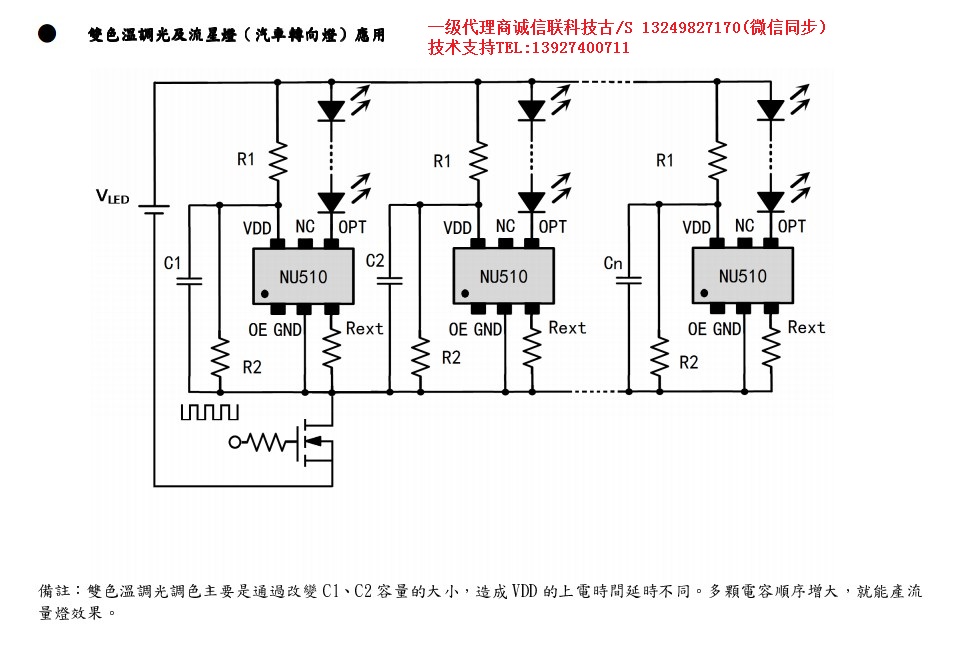

汽车仪表盘车灯照明驱动芯片NU510

always block內省略else所代表的電路 (SOC) (Verilog)

always block內省略else所代表的電路 (SOC) (Verilog)

评论