验证和testbench

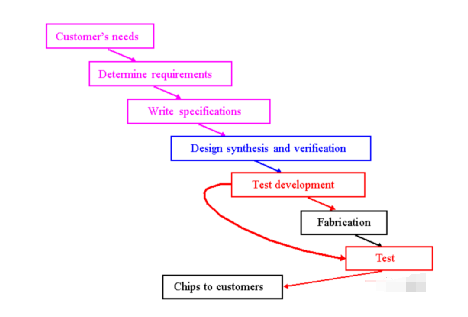

Design Verication(DV)是任何产品开发中必不可少的步骤。 作为质量测试的一部分,DV确保设计的产品是与预期的产品spec相同。 不幸的是,许多设计项目没有完成彻底的DV导致产品不符合客户要求期望并需要昂贵车成本去修改设计。

可以和DV结合使用的质量测试手段:Requirements Management、Configuration Management、FMEA(Function Safety)、Formal(形式验证)、DFT。

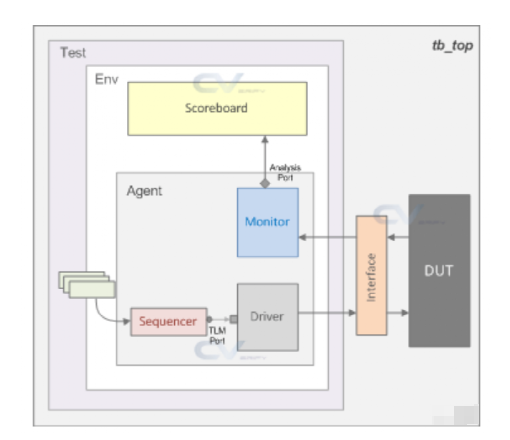

testbench是一种验证的手段。 首先,任何设计都是会有输入输出的。 但是在软环境中没有激励输入,也不会对你设计的输出正确性进行评估。 那么此时便有一种,模拟实际环境的输入激励和输出校验的一种“虚拟平台”的产生。 在这个平台上你可以对你的设计从软件层面上进行分析和校验,这个就是testbench的含义。

testbench里面包含了两个东西。 1激励生成:这个只用来生成输出,他自己没有输入,只是按照一定的规律去给你的设计激励,激励通过设计的输入端口送到你的设计中。 其余的事情不管。 这里的激励,都是预先设想好的,比如根据某个协议,或者某种通信方式传递。 2输出校验:校验你的输出。 他所管的事情就是,接收你设计的输入,然后通过校验输出,找出对应的问题。

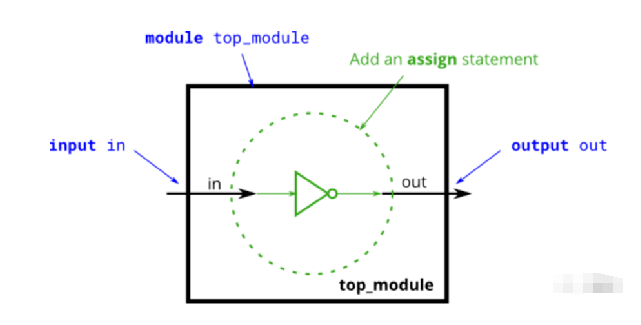

如大家所知,verilog是模块化设计,设计的时候我们首先需要考虑:模块名、模块的功能、端口数量和端口的input/output/inout属性。 然后需要思考:用什么语句和命令实现该模块。

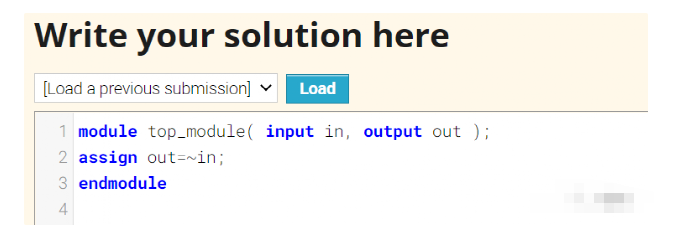

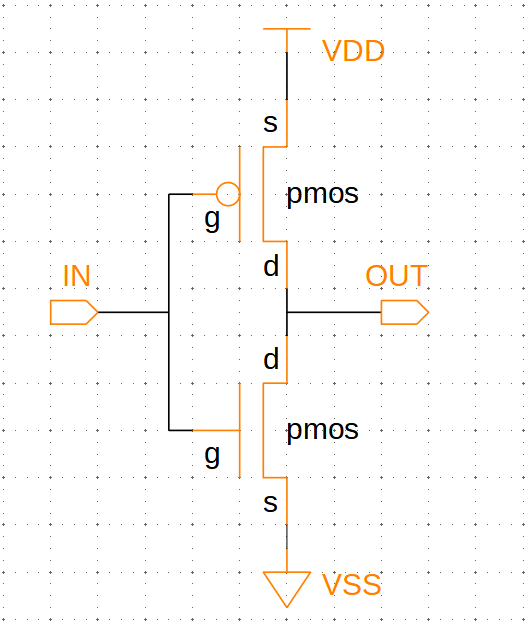

对于反相器,一共只有两个端口,分别是输入和输出,输入和输出之间就是一个单纯的取反关系,可以用数据流描述语句assign对其进行描述,用取反运算符“~”对其进行数据运算。

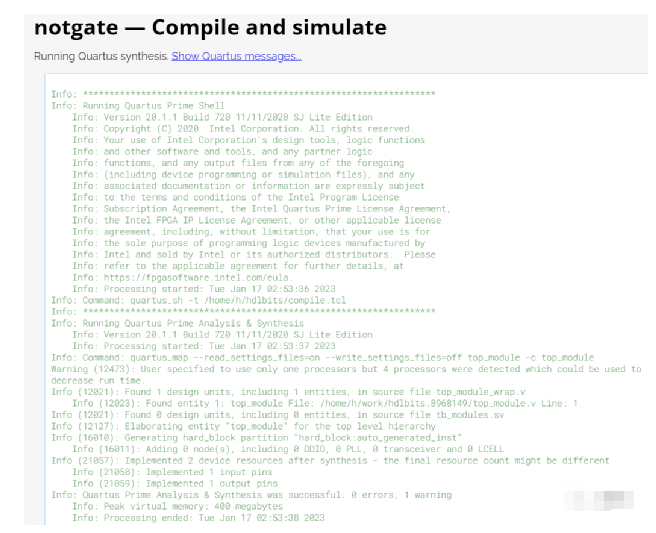

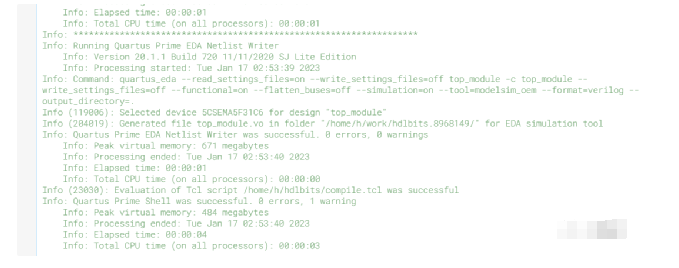

使用在线综合器对其进行综合

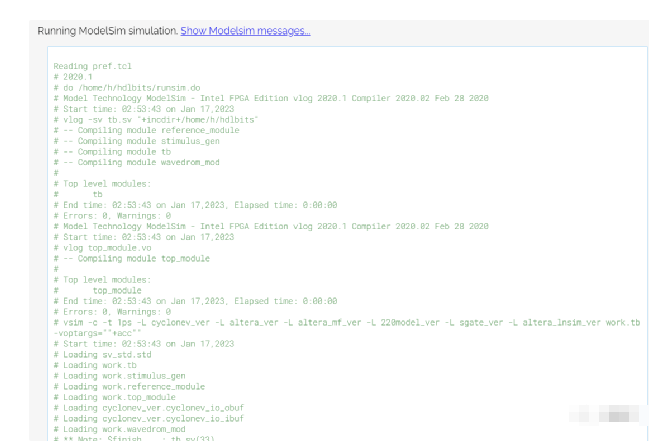

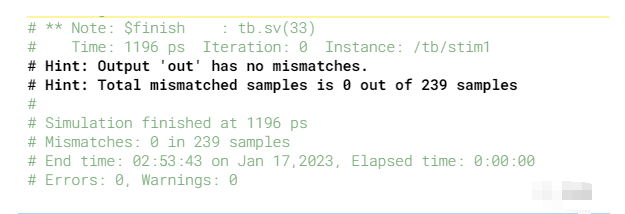

使用在线仿真器对其进行仿真

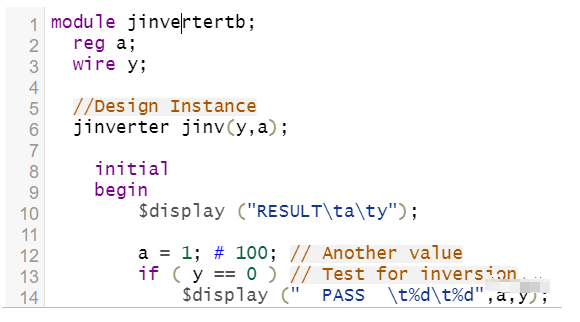

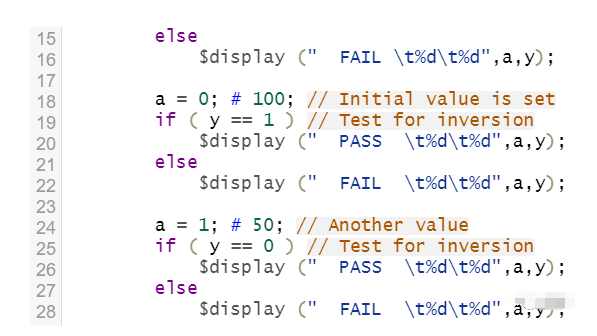

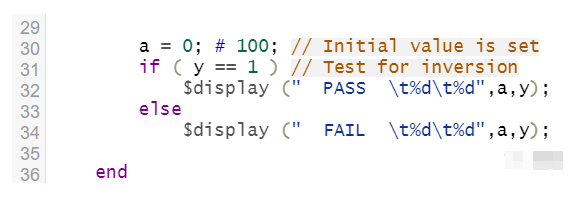

一种反相器testbench示例:

在线仿真器使用的是其内置的testbench进行仿真:

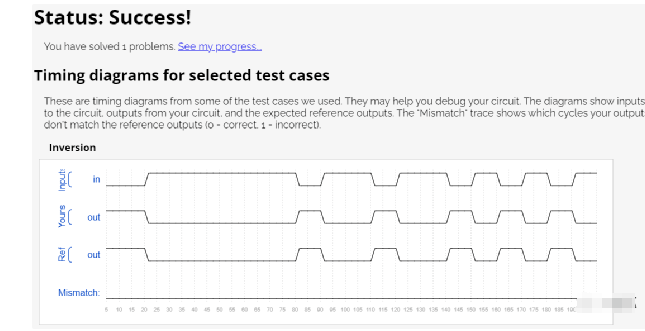

仿真波形

-

反相器

+关注

关注

6文章

240浏览量

42707 -

仿真

+关注

关注

50文章

3872浏览量

132161 -

DV

+关注

关注

0文章

25浏览量

33785 -

Verilog

+关注

关注

28文章

1326浏览量

109302 -

design

+关注

关注

0文章

152浏览量

45531

发布评论请先 登录

相关推荐

窗口电压比较器和反相器连接问题

请问CML转CMOS时钟接在反相器输出端首尾相接的反相器作用是什么?

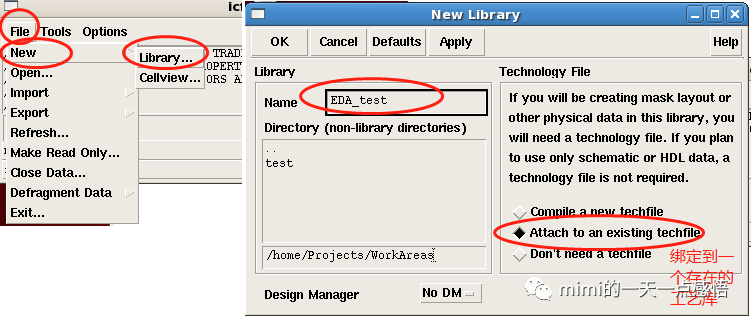

virtuoso中进行CMOS反相器和静态寄存器的电路设计

反相器的输出不对!

cmos反相器设计电路图

MOS反相器和CMOS反相器的详细资料说明

反相器的verilog设计和仿真

反相器的verilog设计和仿真

评论