对于刚接触SV的小伙伴来说,SV有几种不怎么能引起关注,但在实际工作中又经常会用到的数据类型。它们就是枚举(enumeration)、结构体(structures)和自定义类型(typedef)。

这三种数据类型的合理应用能够处理不同逻辑结构的数据,提高代码编写效率和可读性。本文先讲枚举类型的使用语法和一些注意的点。

认识枚举类型

枚举指的是一组有限的被赋予了名字的值的集合。在默认情况下,集合中元素的数据类型是int类型,元素值的大小是从0开始的递增关系。当然,元素的数据类型和值都是可以用户自定义的。

枚举类型在日常生活中很常见,比如春夏秋冬就是表示季节的枚举集合,周一到周天就是表示星期的枚举集合。可以看出,枚举的重要作用,就是为了方便区分和使用。

打个比方,在正常交流时,我们会说现在在冬天,而不会故意去说现在是第4季。同样,当我们使用代码来描述有限集合,比如描述状态机各个状态的时候,使用名字可以大致表达不同状态的行为,代码可读性自然也就提高了。

枚举在代码中实现的功能跟使用宏类似,都可以用名字来代替数值。宏是在预处理阶段将名字换成了值,而枚举是在编译阶段将名字换成值。也就是说,枚举类型的这些名字不是变量,它们不会占据任何内存。且这些名字的有效范围是全局的,如果有变量等命名冲突了可能导致编译不过。

枚举类型的使用

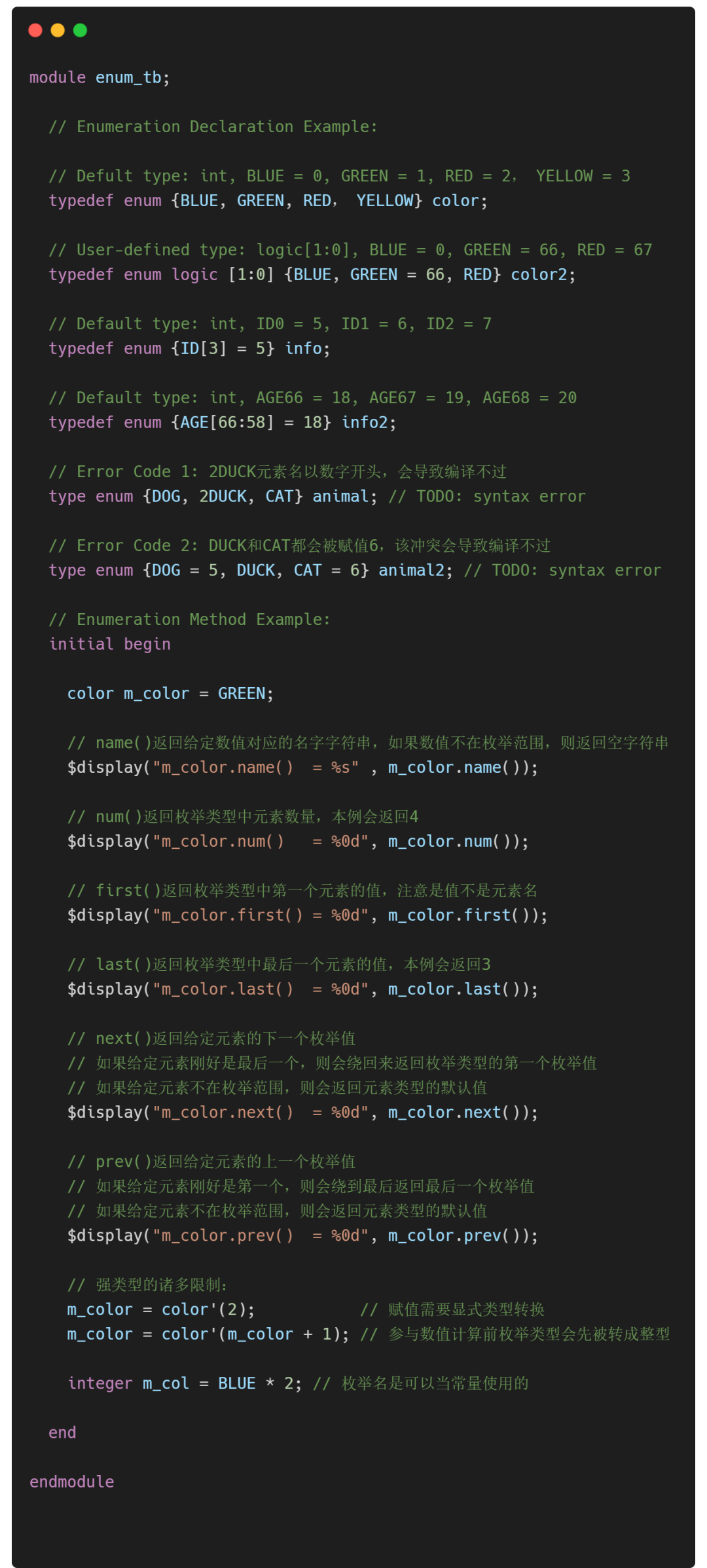

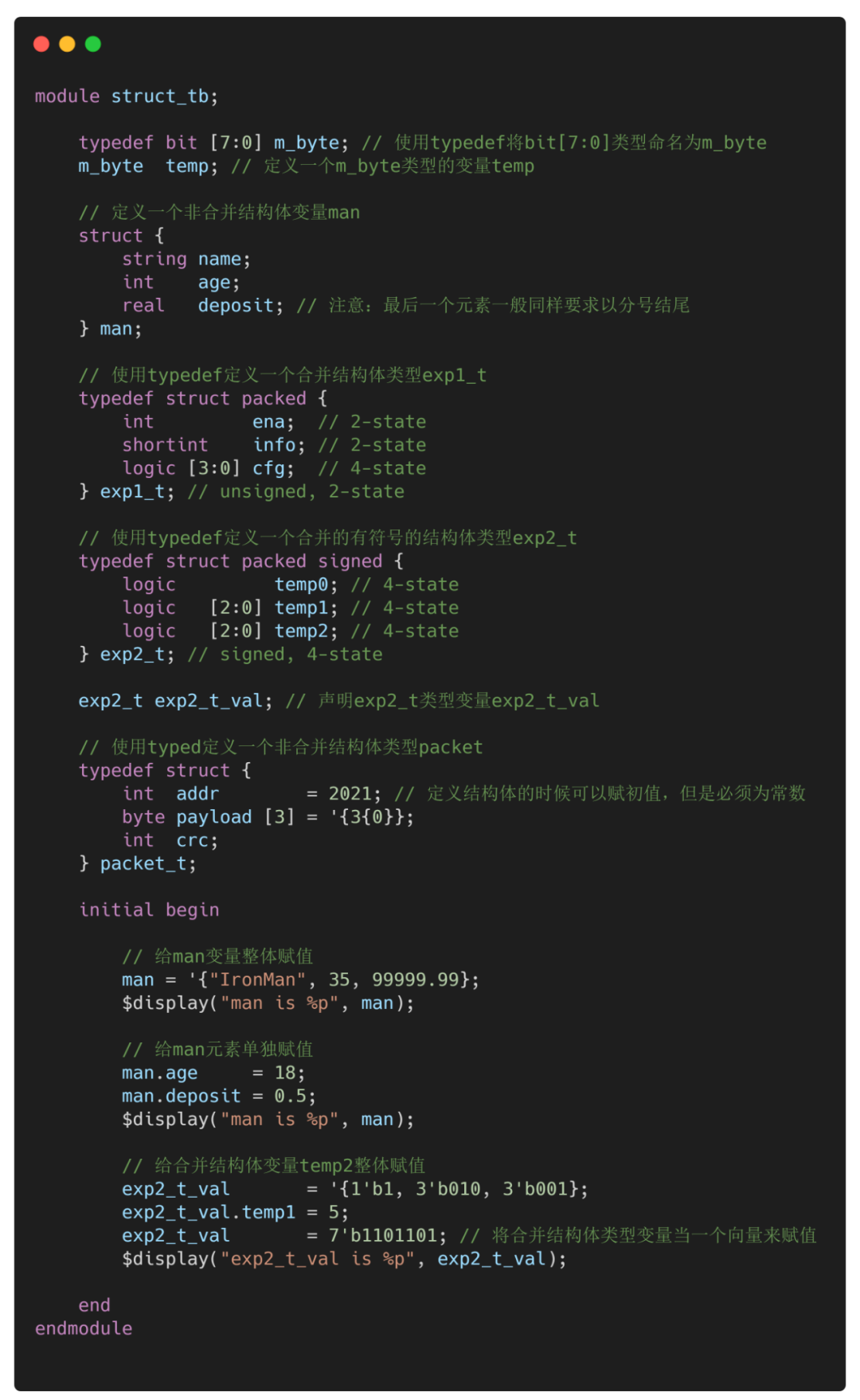

SV的枚举类型声明语法跟C语言很像。如果自增的值与已经自定义的值产生冲突,会导致编译不过;如果枚举名以数字开头,也会导致编译不过。另外,SV为枚举变量还提供了一系列的内建方法(first/last/next/prev等),用来方便对枚举变量进行索引等操作。

在SV中还明确说明了枚举类型是一种强类型(strongly typed)的数据类型。如果给一个枚举变量直接赋一个数值,这个数值不管是不是在枚举范围内,都是不允许的。这种类型检查是为了防止用户乱赋值。不过,SV是允许使用显式类型转换(explicit cast)来完成这种赋值的。

此外,SV允许枚举变量写到数值表达式中进行数值计算,枚举名可以当常量使用。这个时候枚举变量会被自动转换成对应的整型数字之后,再继续完成数值计算。不过当计算结果想要重新赋值给枚举变量的时候,依然需要进行显式的类型转换。

都在代码里

下面代码和注释总结了以上介绍的枚举类型的使用方法和限制,个人觉得掌握例程中的内容对工作来说已经完全足够啦,但例程我还没有经过编译哈。

参考文献

[1] IEEE Standard Association. "IEEE Standard for SystemVerilog-Unified Hardware Design, Specification, and Verification Language." (2013).

-

数据类型

+关注

关注

0文章

238浏览量

14233 -

结构体

+关注

关注

1文章

131浏览量

11413 -

枚举

+关注

关注

0文章

16浏览量

4878

发布评论请先 登录

SystemVerilog中至关重要的的数据类型

SystemVerilog中至关重要的的数据类型

评论