1.XILINXISE传统FPGA设计流程

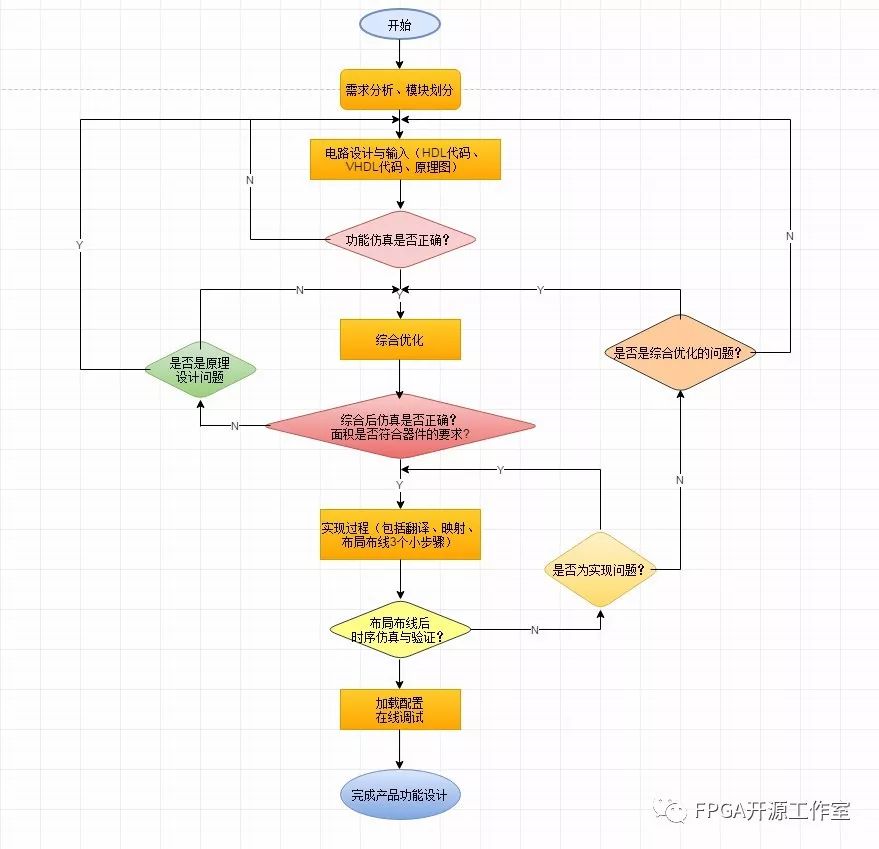

利用Xilinx ISE软件开发FPGA的基本流程包括代码输入、功能仿真、综合、综合后仿真、实现、布线后仿真与验证和下班调试等步骤。如下图所示。

1)电路设计或代码输入

FPGA的设计可以直接画原理图,但是这种方法在比较复杂的系统的情况下,原理图相当复杂,所以慢慢被淘汰,ISE保留这一功能。

现在FPGA的设计输入主要是Verilog和VHDL硬件语言。Verilog语言语法简单,在亚洲区域使用比较广泛;

VHDL被IEEE和美国国防部确认为标准硬件描述语言,在欧洲区域比较常见。

2)功能仿真

在基本的FPGA模块编写完成后,要使用仿真工具对设计的模块进行仿真,验证模块的基本功能是否符合设计。功能仿真也被称为前仿真。常用的仿真工具有

Model Tech公司的Modelsim, Synopsys公司的VCS,Cadence公司的NC-Verilog和NC-VHDL。功能仿真可以加快FPGA的设计,减少设计过程中的错误。

3)综合

综合优化(Synthesize)是将硬件语言或原理图等设计输入翻译成由与,或,非门、RAM、触发器等基本逻辑单元组成的逻辑连接(网表),并根据约束条件优化生成的逻辑连接,输出edf和edn等文件。

4)实现

实现可理解为利用实现工具把逻辑映射到目标器件结构的资源中,决定逻辑的最佳布局,选择逻辑与输入输出功能连接的布线通道进行连线,并产生相应文件(如配置文件与相关报告)。通常可分为如下五个步骤。(1)转换:将多个设计文件进行转换并合并到一个设计库文件中。(2)映射:将网表中逻辑门映射成物理元素,即把逻辑设计分割到构成可编程逻辑阵列内的可配置逻辑块与输入输出块及其它资源中的过程。(3)布局与布线:布局是指从映射取出定义的逻辑和输入输出块,并把它们分配到FPGA内部的物理位置,通常基于某种先进的算法,如最小分割、模拟退火和一般的受力方向张弛等来完成;布线是指利用自动布线软件使用布线资源选择路径试着完成所有的逻辑连接。因最新的设计实现工具是时序驱动的,即在器件的布局布线期间对整个信号通道执行时序分析,因此可以使用约束条件操作布线软件,完成设计规定的性能要求。在布局布线过程中,可同时提取时序信息形成报靠。(4)时序提取:产生一反标文件,供给后续的时序仿真使用。(5)配置:产生FPGA配置时的需要的位流文件。在实现过程中可以进行选项设置。因其支持增量设计,可以使其重复多次布线,且每次布线利用上一次布线信息以使布线更优或达到设计目标。在实现过程中应设置默认配置的下载形式,以使后续位流下载正常。

5)时序分析在设计实现过程中,在映射后需要对一个设计的实际功能块的延时和估计的布线延时进行时序分析;而在布局布线后,也要对实际布局布线的功能块延时和实际布线延时进行静态时序分析。从某种程序来讲,静态时序分析可以说是整个FPGA设计中最重要的步骤,它允许设计者详尽地分析所有关键路径并得出一个有次序的报告,而且报告中含有其它调试信息,比如每个网络节点的扇出或容性负载等。静态时序分析器可以用来检查设计的逻辑和时序,以便计算各通中性能,识别可靠的踪迹,检测建立和保持时间的配合,时序分析器不要求用户产生输入激励或测试矢量。虽然Xilinx与Altera在FPGA开发套件上拥有时序分析工具,但在拥有第三方专门时序分析工具的情况下,仅利用FPGA厂家设计工具进行布局布线,而使用第三方的专门时序分析工具进行时序分析,一般FPGA厂商在其设计环境下皆有与第三方时序分析工具的接口。Synopsys公司的PrimeTime是一个很好的时序分析工具,利用它可以达到更好的效果。将综合后的网表文件保存为db格式,可在PrimeTime环境下打开。利用此软件查看关键路径或设计者感兴趣的通路的时序,并对其进行分析,再次对原来的设计进行时序结束,可以提高工作主频或减少关键路径的跹时。与综合过程相似,静态时序分析也是一个重复的过程,它与布局布线步骤紧密相连,这个操作通常要进行多次直到时序约束得到很好的满足。

在综合与时序仿真过程中交互使用PrimeTime进行时序分析,满足设计要求后即可进行FPGA芯片投片前的最终物理验证。

6)调试与加载配置

设计开发的最后步骤就是在线调试或者将生成的配置文件写入芯片中进行测试。在ISE中使用iMPACT。

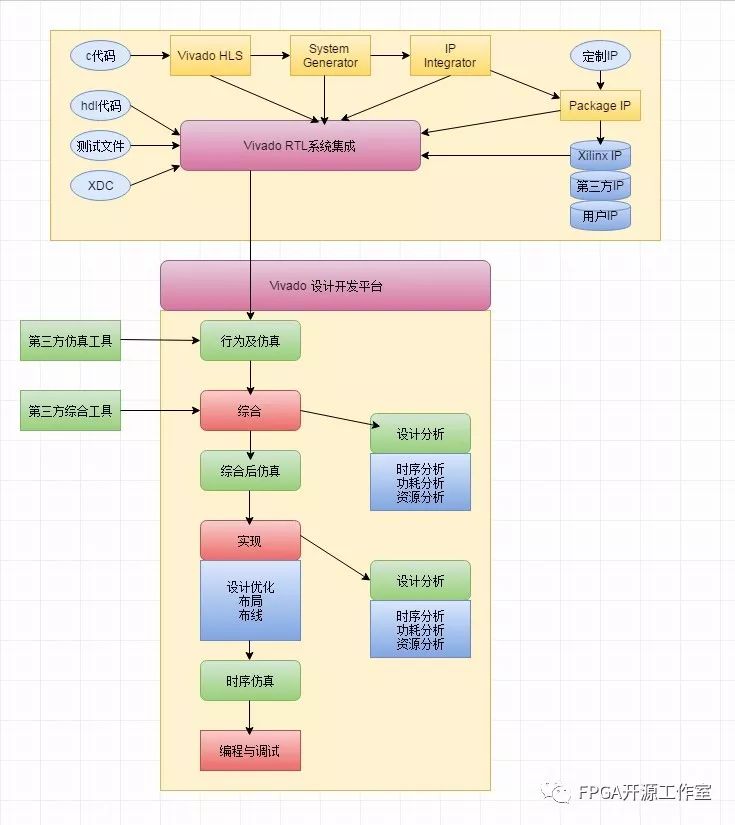

2.XILINXVIVADO传统FPGA设计流程

Xilinx针对7系列FPGA、Zynq-7000 SOC FPGA和UltraScale芯片,为提升设计、集成和实现的效率,推出了全新的开发工具Vivado。

使用Vivado设计FPGA的基本流程如下图

在设计输入阶段,除传统的HDL代码,Vivado还可以接受Vivado HLS生成的HDL代码、System Generator模型输出文件、IP Integrator模型以及IP。

在Vivado下,约束(时序约束和物理约束)采用XDC(xilinx Design Constraints)。

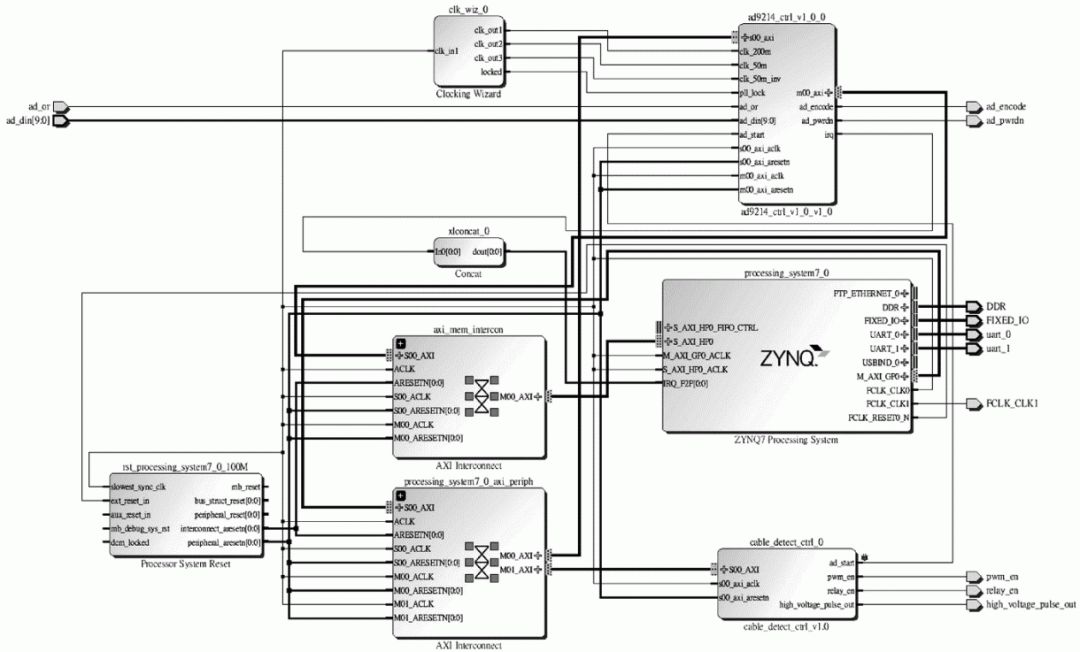

3.SOCFPGA设计流程

针对SOC FPGA的开发,xilinx在Vivado中专门设置了一个工具IP Integrator。

IP Integrator作为IP集成工具,以图形化、模块化的方式在设计中添加IP、连接端口。

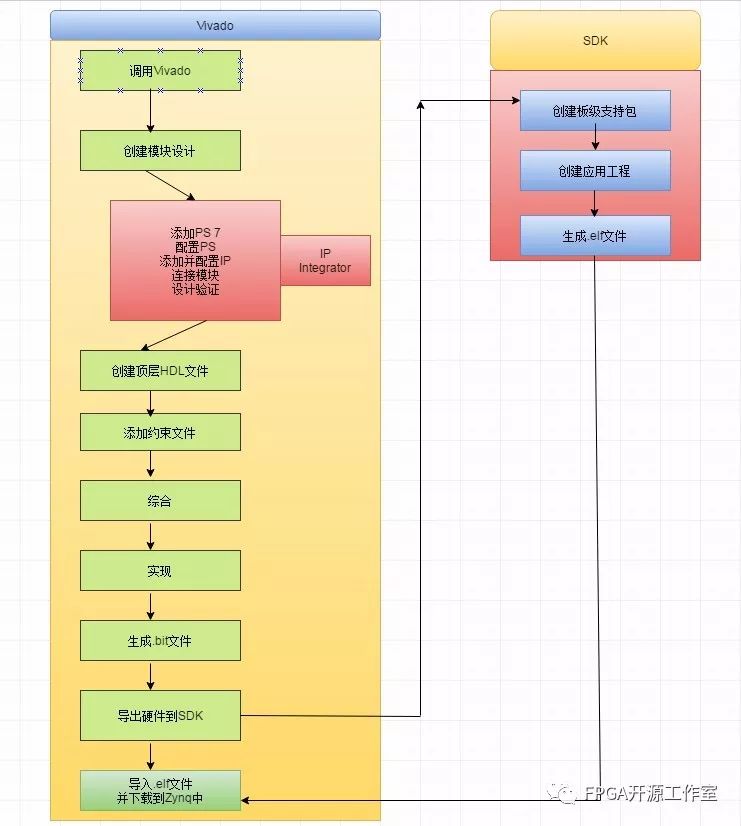

Zynq芯片由两部分组成,分别是PS和PL两部分,相应地需要硬件编程和软件编程。硬件编程使用Vivado,软件编程使用SDK,具体流程见下图。

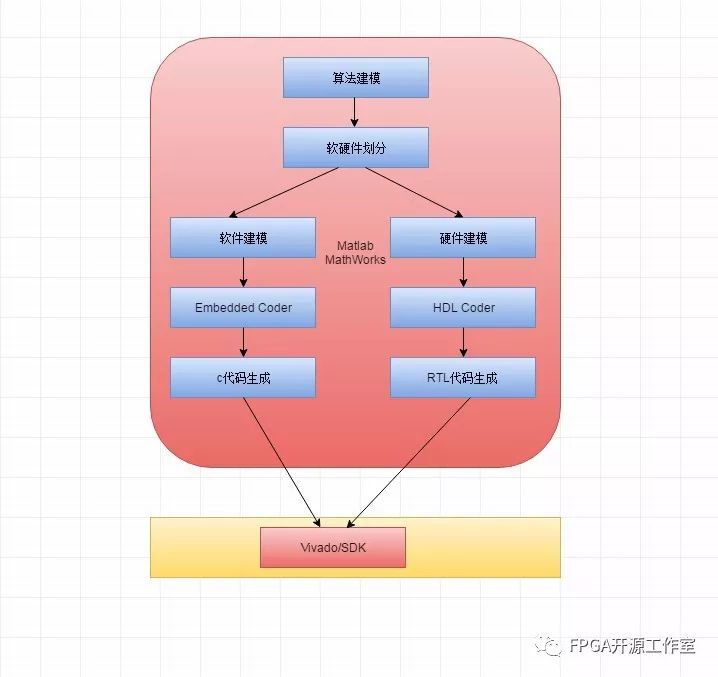

借助Matlab完成Zynq开发,如下图。在Matlab下即可完成算法建模到C代码和RTL代码的生成。

审核编辑 :李倩

-

FPGA

+关注

关注

1664文章

22504浏览量

639310 -

赛灵思

+关注

关注

33文章

1798浏览量

133663 -

仿真

+关注

关注

55文章

4536浏览量

138672

原文标题:从赛灵思FPGA设计流程看懂FPGA设计

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

易灵思2026技术研讨会圆满举办,16nm 钛金系列重塑FPGA效能边界

赛灵思FPGA电源解决方案全解析

易灵思Sapphire SoC中RISC-V平台级中断控制器深度解析

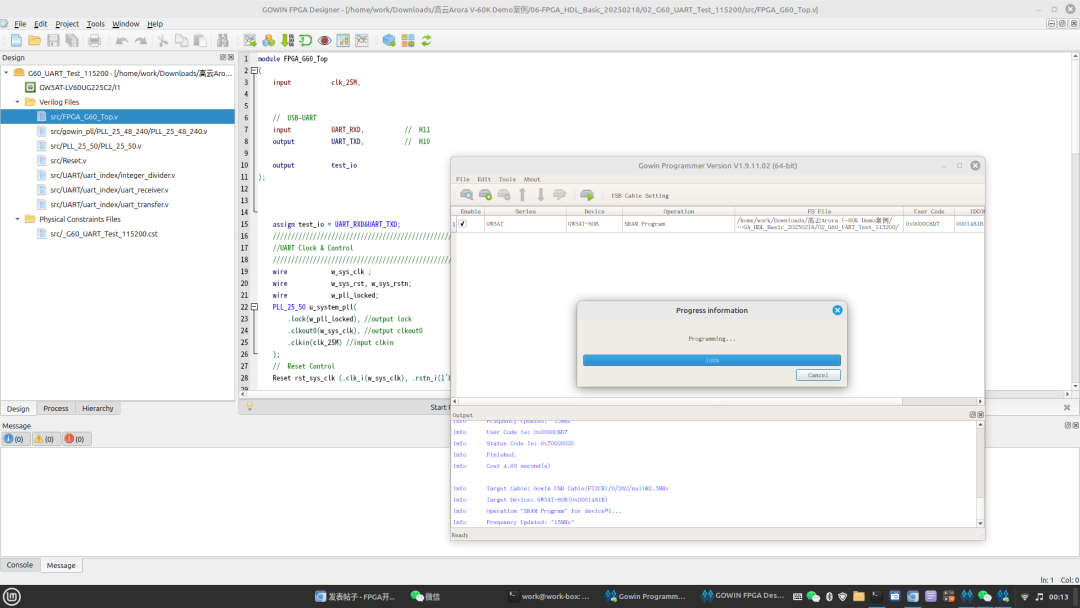

FPGA板下载运行调试流程

FPGA板下载调试流程

易灵思助力上海集成电路紧缺人才培训项目顺利结课

易灵思2025 FPGA技术研讨会成都站圆满收官

【赛题补充说明】2025全国大学生FPGA创新设计竞赛紫光同创杯赛

【赛题知多少】 紫光同创赛题答疑专场|2025年全国大学生嵌入式芯片与系统设计竞赛FPGA赛道

FPGA 40周年!面向未来的FPGA,AMD聚焦边缘智能与异构计算

【经验分享】玩转FPGA串口通信:从“幻觉调试”到代码解析

从赛灵思FPGA设计流程看懂FPGA设计

从赛灵思FPGA设计流程看懂FPGA设计

评论