Mini Circuits的RKK-4-252+倍频器提供4倍的倍频系数,将430至630 MHz的输入频率转换为1720至2520 MHz的输出频率,支持应用包括合成器、本地振荡器、卫星上下转换器等。此模型提供输入功率范围为+16至+19 dBm、低转换损耗和良好的谐波抑制。这个倍增器封装在微型屏蔽表面安装封装(0.50 x 0.50 x 0.18“)中,带有环绕式终端,具有优异的可焊性。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

原文标题:RKK-4-252+4X SMT乘法器,输出频率1720-2520 MHz

文章出处:【微信号:兆亿微波,微信公众号:兆亿微波】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

CD4527B:高性能CMOS BCD速率乘法器的技术剖析与应用探索

(Texas Instruments)的CD4527B,这是一款具有20伏额定电压的低功耗4位数字速率乘法器,它在众多应用场景中展现出卓越的性能。 文件下载: CD4527BNSRG4.pdf 一

CD4089B:高性能CMOS二进制速率乘法器的设计与应用

,以其独特的特性和广泛的应用场景,成为了电子工程师们在设计中值得考虑的重要选择。 文件下载: CD4089BPWE4.pdf 一、CD4089B概述 CD4089B是一款低功耗的4位数字速率乘法器,它的

CD4089B:CMOS 二进制速率乘法器的技术剖析与应用

: CD4089BPW.pdf 一、CD4089B 概述 CD4089B 是一款低功耗的 4 位数字速率乘法器,其输出脉冲速率是时

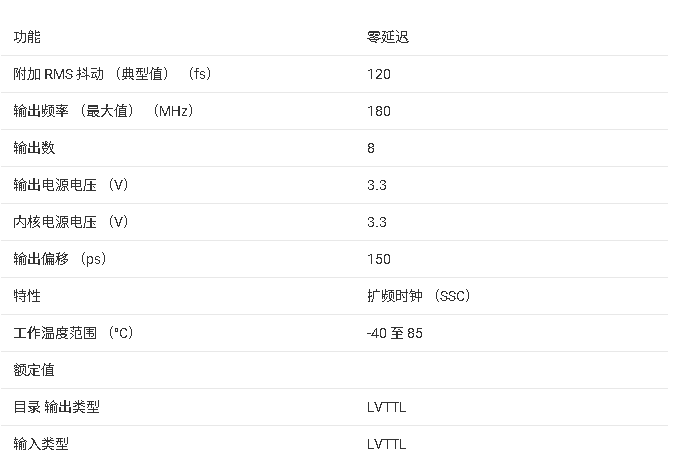

CDCVF25084:高性能时钟乘法器的深度剖析

)的CDCVF25084——一款3.3 - V 1:8零延迟(PLL)x4时钟乘法器。 文件下载: cdcvf25084.pdf 1. 产品概述 CDCVF25084是一款高性能、低偏斜、低抖动的锁相环

低成本模拟乘法器AD633:特性、应用与设计指南

到各种应用场景,为大家呈现一个全面的设计指南。 文件下载: AD633.pdf 一、AD633 概述 AD633是一款功能完备的四象限模拟乘法器,它集成了高阻抗差分X和Y输入,以及高阻抗求和输入(Z)。其低阻抗输出电压由一个埋入

E203V2长周期乘法器核心booth算法解读

低位部分和从第一次开始便从32位寄存器高位开始右移两位,以此类推,进行16次加法运算后,高位部分和已经算出来了,而低位部分和刚好右移到寄存器的最低位,最后还需一个时钟周期输出乘法器的运算结果。

同时

发表于 10-24 09:33

改进wallance树乘法器优化方法

首先,根据之前分享的乘法器的优缺点,我们针对17周期的乘法器进行优化,为乘法设计的专用数据通路,为了保持e203的低功耗、低面积的优点、我们仍采用基4booth算法进行部分积生成,而对

发表于 10-23 06:37

关于E203内核高性能乘法器优化(一)

多个CSA并行地对部分积求和,其中较为经典的结构就是Wallace树形乘法器

下图给出了比较经典的华莱士树的结构:

以一级CSA压缩为延时单位,对9个部分积进行压缩需要4级CSA压缩,共4个延时单位

发表于 10-23 06:09

蜂鸟乘法器设计分享

蜂鸟的乘法器主体设计在ALU模块的子单元MDV模块中,MDV模块包括乘除法器逻辑设计,它只包含运算控制,但并不包含具体运算,它们都需要将部分积或者部分余数传入数据通路(dpath模块)中,从而实现

发表于 10-22 08:21

基4-Booth单周期乘法器的具体设计

的同时,门电路延迟也完全满足要求。甚至在本队尝试将频率提升至32MHz(原E203的2倍)时,该乘法器,包括后文将提到的改进后的除法器依然可以完美地工作。

发表于 10-22 08:07

蜂鸟E203乘法器改进

连续不断的输出,不会像循环移位那样,需计算完才输出,中间没有等待时间。流水线乘法器

大大提高了计算效率,但是占用资源也随即增加。因此将此乘法器用在蜂鸟E203,亦能提高数据计算效率。

发表于 10-22 07:28

蜂鸟E203内核乘法器的优化

乘法器的优化实现一般从两个方面入手。第一是减少生成的部分积数量,另外就是减少部分积累加的延时。

在开源的E203源码中,32*32乘法器是利用radix-4 booth编码产生部分积,每个周期做一次

发表于 10-22 06:11

优化boot4乘法器方法

优化电路设计:在电路设计中,可以采用更快速的逻辑单元和存储器元件,优化关键路径和信号传输路线,从而降低延迟,缩短乘法器的运算周期。

固定位宽:Boot4乘法器可以处理不同位宽的数据,但是处理不同位宽

发表于 10-21 12:13

CDCVF25084 3.3V 1:8零延迟(PLL)x4时钟乘法器技术文档总结

该CDCVF25084是一款高性能、低偏斜、低抖动、锁相环时钟乘法器。它使用 PLL 在频率和相位上将输出时钟精确对齐输入时钟信号,包括 4 的乘法

RKK-4-252+4X SMT乘法器,输出频率1720-2520 MHz

RKK-4-252+4X SMT乘法器,输出频率1720-2520 MHz

评论