电子发烧友网报道(文/李宁远)时钟信号,我们常常在电子组件中看到但很少深入了解,它被用于同步电路,保证相关电子组件能够同步运作。传统的时钟使用外部石英晶体,通过晶体振荡保证精确的节奏。

BAW体声波技术,一种微谐振器技术,这项技术很早就在滤波器中得以应用,用于过滤通信信号。在无线通信正朝着高通信频率、高传输速率和高集成化方向发展中,微谐振器技术开始集成时钟功能提升时钟性能。使用该技术可以将高精度和超低抖动时钟直接集成到包含其他电路的封装中。BAW技术比外部石英晶体体积更小,能通过网络提供更清晰的有线和无线信号,可以为从无线消费电子产品到高端工业系统等一系列领域提供更高质量的通信和更高的效率。

5G与BAW

从BAW应用最广泛的滤波器角度来说,BAW谐振器的关键属性是具备存储结构内的最大声能,用以获得高电气Q因子值,BAW 技术比SAW技术在更高频段、更大带宽下能保持更高的性能。这一点非常重要,在高频段里,BAW技术的表现是更好的。在庞大数据量的应用里需要精准的时钟,BAW技术也是最合适的。

在5G已经到来,且逐步扩大其应用范围的今天,更高带宽和更快数据速率的巨大需求需要通过不断的网络升级实现。传输速率越来越快,对时钟的要求也越来越严格。假设在速率400Gbps时,400Gbps收发器使用四电平脉冲幅度调制(PAM-4)方案来传输数据,这与传统的非归零调制方案相比,可在相同带宽下实现更高的数据速率。

而行业标准802.3bs对PAM-4发射器有非常严格的发射抖动要求,仅将整个发射机抖动的一小部分分配给网络同步器生成的参考时钟,对集成RMS抖动要求能做到低。当前的时钟和石英晶振器件已经开始跟不上数据量迅猛增长的脚步,参考时钟的损伤(如相位噪声)会导致调制信号失真,这在设计更高频率和更宽带宽时会出现不少问题。

在5G升级的推动下,BAW技术时钟能有效减少误码和链路损伤,有助于在网络同步器的输出时钟上实现超低抖动。

BAW振荡器VS石英振荡器

石英晶体振荡器(XOs)已经主导了时间参考市场很久很久,这些晶体振荡器已经覆盖了从低端(实时时钟)到高端(复杂无线电、GPS和军用/航空)应用。石英谐振器有两种不同的方式集成,成为一个独立的振荡器装置,每种方法都有各自的优缺点。第一种方法是将晶体谐振器与振荡电路相结合(SPXO),并简单地添加输出驱动器来支持不同的输出类型,这种办法很简单,但能支持的频率极其有限,频率支持完全依赖于所使用的石英晶体。

另一种晶体集成的方法,是基于PLL,其VCO工作频率更高(通常为GHz)。在频率的支持上这种方法更全面,但也需要更多的核心模块,这意味着尺寸和能耗的上升。而且,PLL校准和锁定将导致启动时间较慢,通常在10 ms或以上。

单IC的BAW振荡器解决方案,包含BAW谐振器、分数输出分频器(FOD)和输出驱动器,它们一起产生一个预先编程的输出频率。这种BAW振荡器在规格上接近于SPXO,但是它能够输出的频率没有SPXO那样的限制,简单来说就是用接近于SPXO的规格实现了基于PLL/VCO石英振荡器的频率。而且BAW振荡器通常启动时间极快,不会出现PLL校准和锁定导致启动时间较慢这种问题。

BAW 超低抖动时钟,TI

对所有的时钟产品,抖动是核心性能。BAW谐振器技术不需要高频VCXO,只需现成的低成本标准低频振荡器,就可将高精度和超低抖动时钟直接集成到包含其他电路的封装中。以TI的LMK6系列BAW振荡器为例,小于60fs的集成RMS抖动远低于PAM-4 串行器/解串器方案里交换机专用 IC 要求在12kHz至20MHz频段内的最大集成参考时钟抖动为150fs的要求。同时在振动方面,BAW振荡器由于振动而表现出最小的频率偏差相比于晶体振荡器有着数量级的改进。

小结

现在越来越多的无线技术被设计进入到电子产品中,而且要在PCB部分不使用太复杂的计算就可以设计好的无线模块。而且在数据速率不断攀升的趋势下,石英晶振越来越难以达到灵活性、尺寸、成本以及抖动性能上的各种要求。基于BAW技术的时钟,大大减少了设计难度,并解决了当前石英晶振器件的局限性。

随着5G进一步普及,在工业自动化、电动汽车、医疗设备、楼宇自动化以及电网设施这些对于数据和稳定性都有较高要求的应用,基于BAW技术时钟会大有可为。

BAW体声波技术,一种微谐振器技术,这项技术很早就在滤波器中得以应用,用于过滤通信信号。在无线通信正朝着高通信频率、高传输速率和高集成化方向发展中,微谐振器技术开始集成时钟功能提升时钟性能。使用该技术可以将高精度和超低抖动时钟直接集成到包含其他电路的封装中。BAW技术比外部石英晶体体积更小,能通过网络提供更清晰的有线和无线信号,可以为从无线消费电子产品到高端工业系统等一系列领域提供更高质量的通信和更高的效率。

5G与BAW

从BAW应用最广泛的滤波器角度来说,BAW谐振器的关键属性是具备存储结构内的最大声能,用以获得高电气Q因子值,BAW 技术比SAW技术在更高频段、更大带宽下能保持更高的性能。这一点非常重要,在高频段里,BAW技术的表现是更好的。在庞大数据量的应用里需要精准的时钟,BAW技术也是最合适的。

在5G已经到来,且逐步扩大其应用范围的今天,更高带宽和更快数据速率的巨大需求需要通过不断的网络升级实现。传输速率越来越快,对时钟的要求也越来越严格。假设在速率400Gbps时,400Gbps收发器使用四电平脉冲幅度调制(PAM-4)方案来传输数据,这与传统的非归零调制方案相比,可在相同带宽下实现更高的数据速率。

而行业标准802.3bs对PAM-4发射器有非常严格的发射抖动要求,仅将整个发射机抖动的一小部分分配给网络同步器生成的参考时钟,对集成RMS抖动要求能做到低。当前的时钟和石英晶振器件已经开始跟不上数据量迅猛增长的脚步,参考时钟的损伤(如相位噪声)会导致调制信号失真,这在设计更高频率和更宽带宽时会出现不少问题。

在5G升级的推动下,BAW技术时钟能有效减少误码和链路损伤,有助于在网络同步器的输出时钟上实现超低抖动。

BAW振荡器VS石英振荡器

石英晶体振荡器(XOs)已经主导了时间参考市场很久很久,这些晶体振荡器已经覆盖了从低端(实时时钟)到高端(复杂无线电、GPS和军用/航空)应用。石英谐振器有两种不同的方式集成,成为一个独立的振荡器装置,每种方法都有各自的优缺点。第一种方法是将晶体谐振器与振荡电路相结合(SPXO),并简单地添加输出驱动器来支持不同的输出类型,这种办法很简单,但能支持的频率极其有限,频率支持完全依赖于所使用的石英晶体。

另一种晶体集成的方法,是基于PLL,其VCO工作频率更高(通常为GHz)。在频率的支持上这种方法更全面,但也需要更多的核心模块,这意味着尺寸和能耗的上升。而且,PLL校准和锁定将导致启动时间较慢,通常在10 ms或以上。

单IC的BAW振荡器解决方案,包含BAW谐振器、分数输出分频器(FOD)和输出驱动器,它们一起产生一个预先编程的输出频率。这种BAW振荡器在规格上接近于SPXO,但是它能够输出的频率没有SPXO那样的限制,简单来说就是用接近于SPXO的规格实现了基于PLL/VCO石英振荡器的频率。而且BAW振荡器通常启动时间极快,不会出现PLL校准和锁定导致启动时间较慢这种问题。

BAW 超低抖动时钟,TI

对所有的时钟产品,抖动是核心性能。BAW谐振器技术不需要高频VCXO,只需现成的低成本标准低频振荡器,就可将高精度和超低抖动时钟直接集成到包含其他电路的封装中。以TI的LMK6系列BAW振荡器为例,小于60fs的集成RMS抖动远低于PAM-4 串行器/解串器方案里交换机专用 IC 要求在12kHz至20MHz频段内的最大集成参考时钟抖动为150fs的要求。同时在振动方面,BAW振荡器由于振动而表现出最小的频率偏差相比于晶体振荡器有着数量级的改进。

小结

现在越来越多的无线技术被设计进入到电子产品中,而且要在PCB部分不使用太复杂的计算就可以设计好的无线模块。而且在数据速率不断攀升的趋势下,石英晶振越来越难以达到灵活性、尺寸、成本以及抖动性能上的各种要求。基于BAW技术的时钟,大大减少了设计难度,并解决了当前石英晶振器件的局限性。

随着5G进一步普及,在工业自动化、电动汽车、医疗设备、楼宇自动化以及电网设施这些对于数据和稳定性都有较高要求的应用,基于BAW技术时钟会大有可为。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

BAW

+关注

关注

3文章

143浏览量

19457

发布评论请先 登录

相关推荐

热点推荐

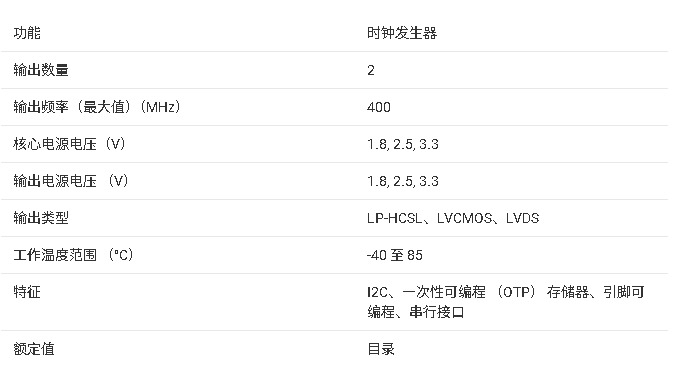

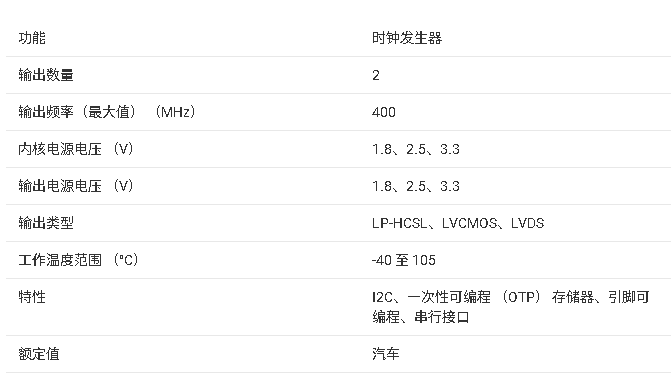

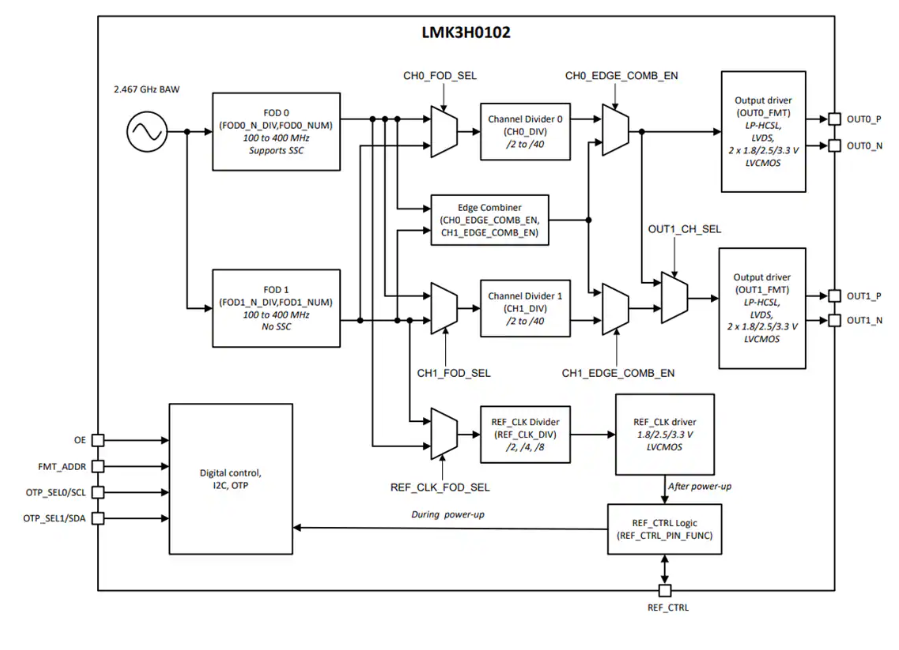

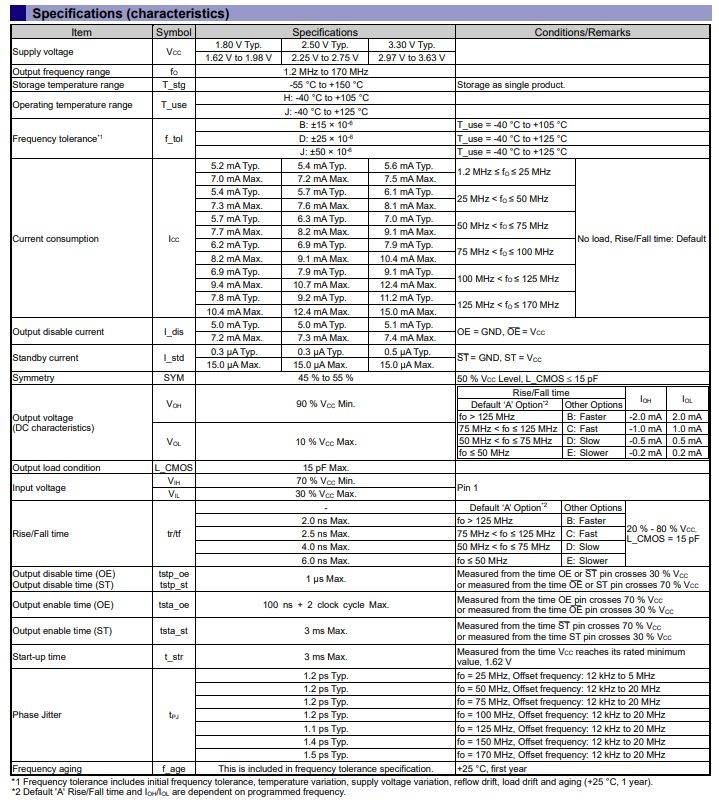

LMK3H0102 参考无源2差分或5单端输出PCIe Gen 1-7兼容可编程BAW时钟发生器总结

该LMK3H0102是一款 2 输出 PCIe Gen 1 至 Gen 7 兼容无基准时钟发生器,支持扩频时钟 (SSC)。该器件基于 TI 专有的体声波 (BAW) 技术,提供 ±2

LMK3C0105 参考无5-LVCMOS输出可编程BAW时钟发生器技术文档总结

LMK3C0105是一款支持 SSC 的 5 输出无基准时钟发生器。该器件基于 TI 专有的体声波 (BAW) 技术,提供 ±25ppm 时钟输出,无需任何晶体或外部

LMK3C0105-Q1 参考无源5路LVCMOS输出可编程BAW时钟发生器技术文档总结

LMK3C0105-Q1 是一款支持 SSC 的 5 输出无基准时钟发生器。该器件基于 TI 专有的体声波 (BAW) 技术,提供 ±25ppm 时钟输出,无需任何晶体或外部

LMK3H0102-Q1 参考无晶体时钟发生器技术文档总结

LMK3H0102-Q1 是一款符合 PCIe Gen 1 至 Gen 7 标准的 2 输出无基准时钟发生器,支持扩频时钟 (SSC)。该器件基于 TI 专有的体声波 (BAW) 技术

精准时钟,驱动未来 ----澜起科技发布多款高性能时钟芯片

,将为人工智能、高速通信、工业控制等关键领域提供精准、可靠的时钟信号支撑。 澜起科技高性能时钟芯片 作为电子系统的"心脏",时钟芯片产生的脉冲信号是系统运行的基石,其信号质量直接决定了

Texas Instruments LMK3H0102无基准时钟发生器数据手册

(BAW) 技术,提供 ±25ppm时钟输出,无需任何晶体或外部时钟基准。这些器件可同时提供两个SSC时钟、两个非SSC

PTP 时钟:精准时钟同步的核心力量

在当今数字化时代,时钟同步对于众多领域的高效、稳定运行至关重要。无论是工业自动化生产线的协同运作,还是汽车电子系统中各个部件的精准配合,都离不开高精度的时钟同步技术。西安同步电子科技有

PTP 时钟:精准时钟同步的核心力量

在当今数字化时代,时钟同步对于众多领域的高效、稳定运行至关重要。无论是工业自动化生产线的协同运作,还是汽车电子系统中各个部件的精准配合,都离不开高精度的时钟同步技术。西安同步电子科技有

爱普生FC-12M石英晶体谐振器精准时钟源解决方案

在当今数字化时代,电子设备无处不在,从我们日常使用的智能手机、平板电脑,到复杂的工业控制系统、通信基站,每一台设备的稳定运行都离不开精准的时钟信号。而在众多提供时钟信号的元件中,爱普生FC-12M

爱普生SG-8201CJA车规晶振:智能汽车时代的精准时钟解决方案

在现代汽车电子系统中,随着自动驾驶和高级驾驶辅助系统(ADAS)的快速发展,对时钟信号的精度和稳定性提出了极高的要求。爱普生推出的SG-8201CJA车规晶振凭借其卓越的性能,成为智能汽车时代的精准时钟解决方案。

基于BAW技术的时钟解决海量数据下的精准时钟需求

基于BAW技术的时钟解决海量数据下的精准时钟需求

评论