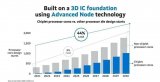

单片 SoC 的尺寸变得太大,无法制造 某些 SoC 的功能要获得最佳实现,可能需要不同的工艺节点 对增强产品的可扩展性和可组合性需求正在增加

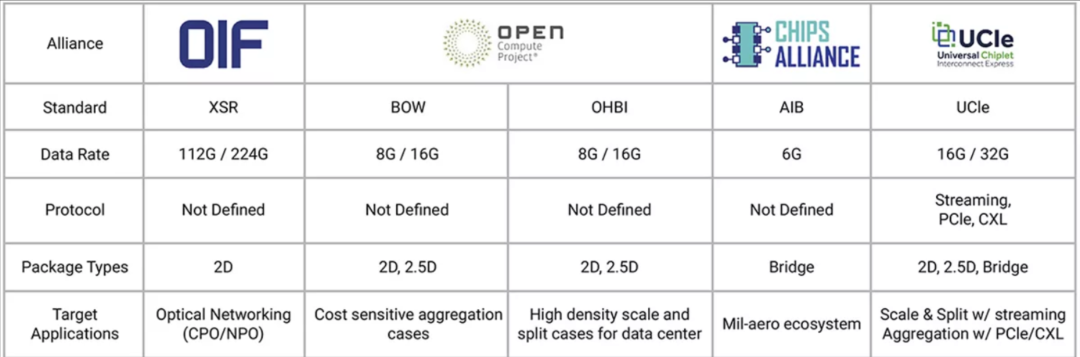

Optical Interface Forum (OIF) – 针对晶粒间连接而优化的 XSR 和 USR 物理层规范 Chips Alliance – 最初由英特尔推出的 AIB 规范 Open Compute Platform (OCP) – 针对不同用例而优化的 OpenHBI 和 Bunch-of-Wires (BOW) 规范 Unified Chiplet Interconnect Express (UCIe) – 涵盖多个用例和完整协议栈的全面晶粒间互连规范

UCIe 系谱

UCIe 路线图和用例

用于先进封装(硅中介层、硅桥或 RDL 扇出)的 UCIe 用于标准包装(有机基材或层压板)的 UCIe

UCIe 规范概述

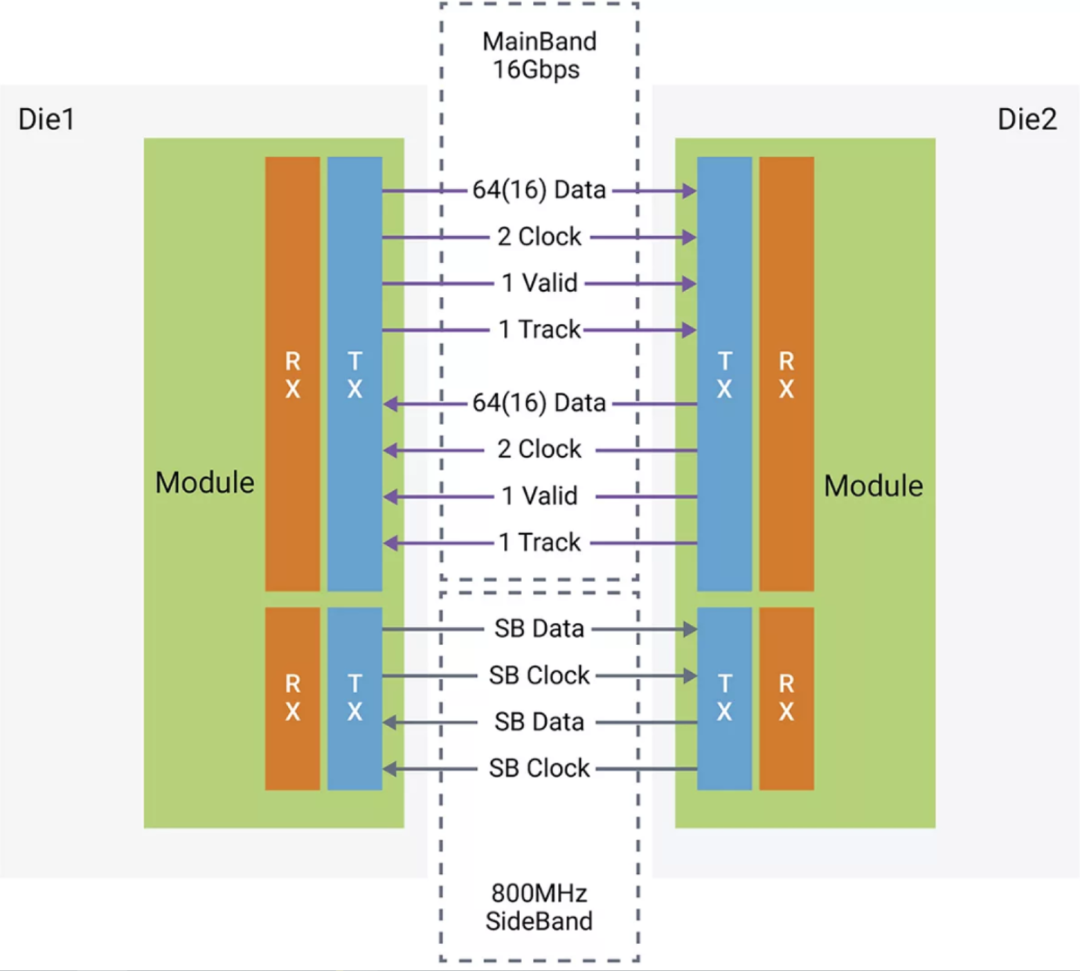

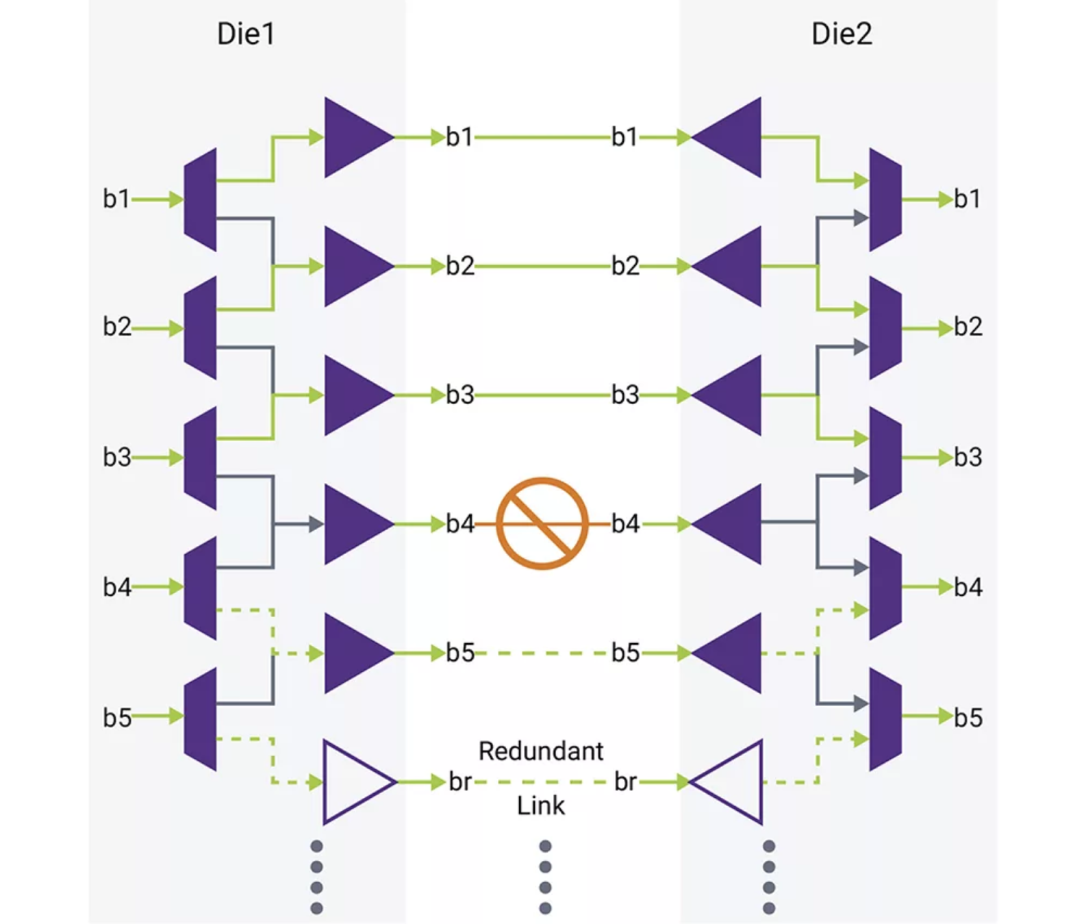

物理层是封装介质的电气接口。它包括电气 AFE(发射器、接收器)以及边带信道,可实现两个晶粒之间的参数交换和协商。它还包括可实现链路初始化、训练和校准算法以及测试和修复功能的逻辑 PHY。 晶粒间适配器层负责链路管理功能以及协议仲裁和协商。它包括基于 CRC 和重试机制的可选纠错功能。 协议层实施一个或多个 UCIe 支持的协议。如今,此类协议是 PCI Express、CXL 和/或流式传输协议。它们是基于 Flit 的协议,可提供最高效率和更低的延迟。

物理层

晶粒间适配器层

CXL3 256B 标准 FLIT 模式 CXL3 256B 延迟优化 FLIT 模式 PCIe6 256B FLIT 模式 CXL2 68B 增强型 FLIT 模式 流式传输 64B 原始模式

协议层

结语

原文标题:多晶粒SoC成趋势,UCIe标准助其一臂之力

文章出处:【微信公众号:电子发烧友网】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

电子发烧友网

+关注

关注

1013文章

544浏览量

167491

原文标题:多晶粒SoC成趋势,UCIe标准助其一臂之力

文章出处:【微信号:elecfans,微信公众号:电子发烧友网】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

马上有券 | 1-6层免费打样无限领,喊上搭子一起冲!

华秋PCB免费打样全新升级1-6层全支持邮费也可参与抵扣另外除新用户注册即有的3张免费打样券外还可邀请好友助你一臂之力积攒助力值兑换免费打样券每邀请2个好友(即2个助力值)即可得1次免费打

【备赛指南】2026全国大学生嵌入式大赛-ST赛道官方推荐,华清远见STM32U5/MP157开发板助你一臂之力!

第九届(2026)全国大学生嵌入式芯片与系统设计竞赛(以下简称"大赛")已正式启动,报名火热进行中。作为教育部认证的国家级A类赛事,大赛历经九年积淀,已成为检验高校电子类专业人才培养质量、展现大学生创新实践能力的重要平台。无论你是初涉嵌入式的新手,还是寻求突破的创客玩家,ST芯片应用赛道都是不容错过的舞台。01芯片应用【ST赛道】选题介绍今年ST赛道公布了七

别让通讯拖后腿!耐达讯自动化Profibus总线光纤中继器,助力焊接精度“一臂之力”

汽车焊装车间的工程师们,是不是常被这几个问题搞得头大?机械臂焊接精度忽高忽低、不同品牌设备“鸡同鸭讲”、改造成本高还耽误生产……这些通讯痛点,今天咱们就用耐达讯自动化的Profibus总线光纤中继器来解决!

如何在智多晶FPGA上使用MIPI接口

大家好呀!今天我们来聊聊一个非常实用的话题——如何在智多晶FPGA上使用MIPI接口。不管是做摄像头图像采集还是屏幕显示控制,MIPI都是非常常见的接口标准。掌握了它,你的视频项目开发效率将大大提升!

新思科技UCIe IP解决方案实现片上网络互连

通用芯粒互连技术(UCIe)为半导体行业带来了诸多可能性,在Multi-Die设计中实现了高带宽、低功耗和低延迟的Die-to-Die连接。它支持定制HBM(cHBM)等创新应用,满足了I/O裸片

多晶硅在芯片制造中的作用

在芯片的纳米世界中,多晶硅(Polycrystalline Silicon,简称Poly-Si) 。这种由无数微小硅晶粒组成的材料,凭借其可调的电学性能与卓越的工艺兼容性,成为半导体制造中不可或缺的“多面手”。

智多晶VBO_TX IP产品核心亮点

在当今数字化世界中,视频数据的高速传输对于众多电子设备和应用场景至关重要。智多晶微电子有限公司推出的 VBO_TX IP(基于 V-by-One HS Standard_Ver 1.4 版本协议技术标准)为这一需求提供了

技术资讯 I 完整的 UCIe 信号完整性分析流程和异构集成合规性检查

。随着3DHI系统越来越复杂,UCIe(UniversalChipletInterconnectExpress)标准变得非常重要,对于未来的先进封装和半导体系统设计而

智多晶FPGA设计工具HqFpga接入DeepSeek大模型

在 AI 赋能工程设计的时代浪潮中,智多晶率先迈出关键一步——智多晶正式宣布旗下 FPGA 设计工具 HqFpga 接入 DeepSeek 大模型,并推出 FPGA 设计专属 AI 助手——晶小

智多晶eSPI_Slave IP介绍

eSPI总线具有低功耗、管脚数量少、高效的数据传输等优点,常用于与EC、BMC、SIO等外设的通信,是PC中CPU与这些外设通信的主流协议。智多晶eSPI_Slave IP符合eSPI标准规范,支持相关协议属性。

多晶粒SoC成趋势,UCIe标准助其一臂之力

多晶粒SoC成趋势,UCIe标准助其一臂之力

评论