AXI总线作为一种线,可以挂若干主设备与从设备,如果若干主设备要同时访问总线,必然会导致总线需要仲裁。本文不涉及细节,只简单减少原理,一般来说这个东西不需要自己写,ARM会提供,但是作为设计者要大致知道原理。

1. 所谓总线,是个什么意思。

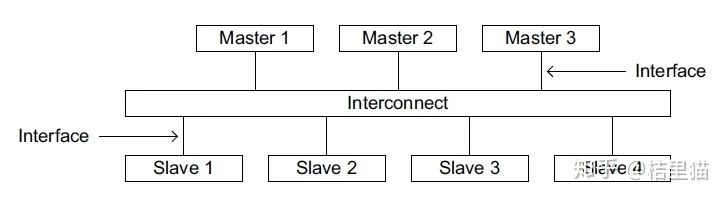

实际上是有个interconnect的模块把所有东西连起来的。主设备会发起读写请求,从设备只能被动接受。SOC中的CPU或者其他加速核心比如AI加速器是主设备。从设备一般是存储啊外设啊之类的东西。基本的连接关系是这样的。

2. 这个Interconnect里有什么东西

这个Interconnect连接了整个系统,起到了仲裁的信号的作用,所以还是比较关键的。一般来讲,疯狂往interconnect上挂各种主从设备是会影响最后的时序的。由于AXI官方文档IHI0022E里面貌似是没有太多这方面介绍,换句话说,AXI协议并没有规定主从设备连一起应该如何工作,于是这里以赛灵思ug1037为基础介绍一下。

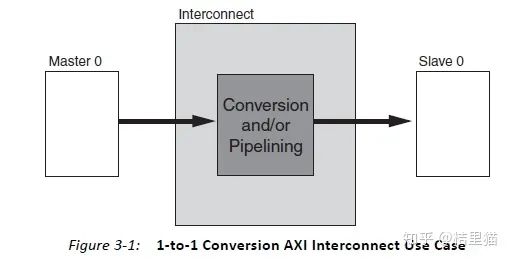

2.1 1to1 interconnect

这个贼简单,不用过多减少。。。一对一的连上去就好了。模范夫妻。

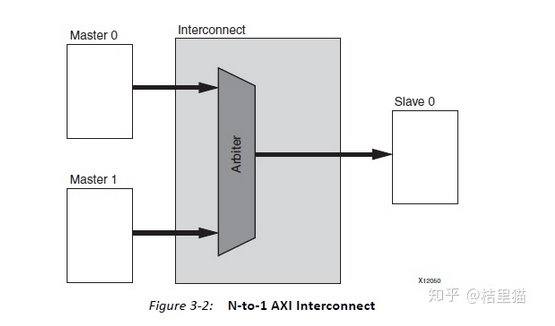

2.2 N-to-1 Interconnect

这个是稍微复杂的版本,类似于一妻多夫。。。如果有多个主设备,一个从设备。那中间需要一个仲裁器。某个主设备传输前请求总线,如果总线忙就等着。一般来讲,最简单的仲裁原理是轮换优先级。例如有三个主设备ABC。上次总线权限给了A。则下次的优先级变为BCA。

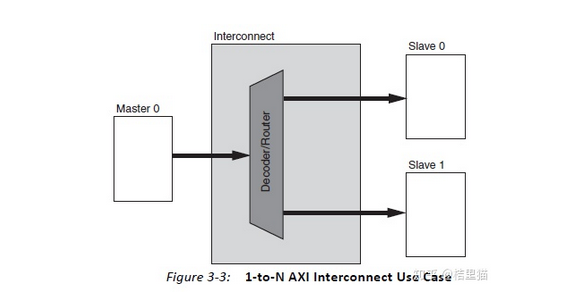

2.3 1-to-N Interconnect

1-to-N原理上比N-to-1简单。一夫多妻的版本。。。只需要简单判断一下地址确认要往哪个从设备里写,基本上就是多路选择器。不需要仲裁。总线也不会阻塞。

2.4 N-to-M Interconnect

这种情况就比较复杂了。。。涉及到多设备时间管理。但实际上稍微复杂一点的SOC这类情况才是常态。

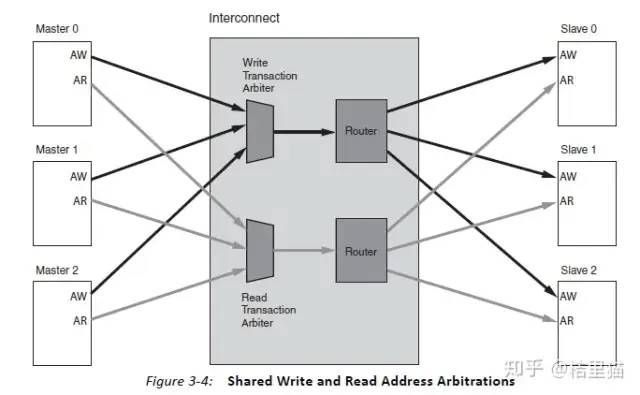

如上图所示,读写通道是分开的。各自有一个仲裁器(Arbiter),仲裁原理和N-to-1是一致的。仲裁器会从所有写请求和所有读请求中各选出来一个来执行。

3. 实际上用的时候怎么用

自己造AXI的各种轮子其实是比较繁琐的,不仅仅是interconnect问题,举个简单的例子,AXI的DMA什么的自己造轮子DEBUG非常耗时。如果是FPGA,可以直接用XILINX的各路IP。如果是ASIC, 一般会有对应的IP卖。比如ARM提供的最小系统一般会自带这个interconnect。

如果SOC比较复杂,那还是有可能需要自己造这个轮子。比如为了压榨总线的性能,如果两个主设备访问的是两个不同的从设备,如果想实现同时执行,那对这个interconnect就有其他的要求。

4. 总结

一般情况下,总线可以理解为一种资源。由一对主从设备独占使用。对于AXI来讲,一般是两种资源,读总线和写总线,通过某种仲裁方式分配给不同的主从设备。

-

soc

+关注

关注

38文章

4514浏览量

227547 -

总线

+关注

关注

10文章

3014浏览量

91286 -

AXI总线

+关注

关注

0文章

68浏览量

14713

原文标题:SOC中AXI总线是如何连接的

文章出处:【微信号:IC学习,微信公众号:IC学习】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

蜂鸟E203 SoC的私有设备总线的简单使用

利用蜂鸟E203搭建SoC【1】——AXI总线的配置与板级验证

人脸识别和AES加密协同的SOC设计架构

将e203 例化AXI总线接口

AXI GPIO扩展e203 IO口简介

RDMA简介9之AXI 总线协议分析2

RDMA简介8之AXI 总线协议分析1

AMD Versal Adaptive SoC Clock Wizard AXI DRP示例

SOC中AXI总线怎么连接

SOC中AXI总线怎么连接

评论