一、本文将介绍如何使用Icarus Verilog+GTKWave来进行verilog文件的编译和仿真。

Icarus VerilogIcarus Verilog极其小巧,支持全平台Windows+Linux+MacOS,并且源代码开源。通过tb文件可以生成对应的仿真波形数据文件。

通过GTKWave可以查看仿真波形图,支持将Verilog转换为VHDL文件。

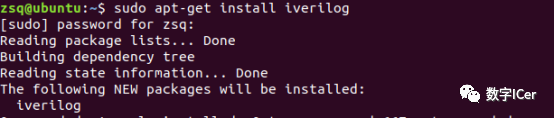

1.安装iverilog:

sudoapt-getinstalliverilog

安装完成查看版本

iverilog-v

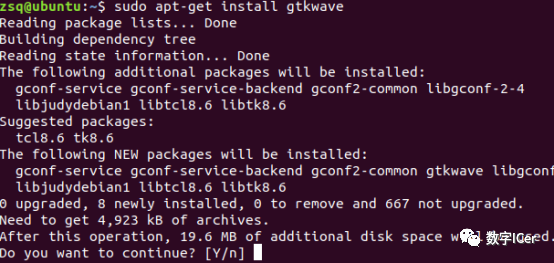

2.安装gtkwave:

sudoapt-getinstallgtkwave

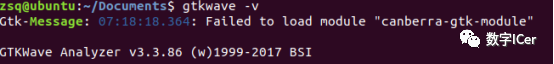

安装完成查看版本

gtkwave-v

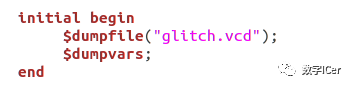

tb中添加:

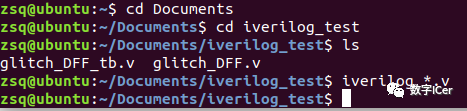

3.编译:

进入文件目录,输入命令:

iverilog*.v

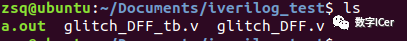

编译完成出现.out文件

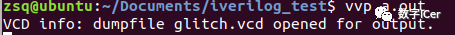

生成.vcd文件

vppa.out

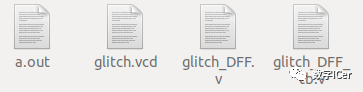

执行后产生的文件如下:

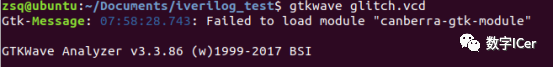

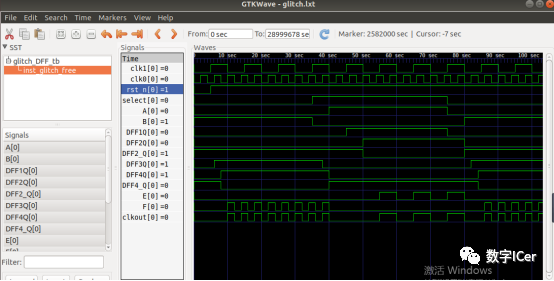

4.用GTKWave打开VCD文件:

gtkwaveglitch.vcd

执行完成后,弹出界面

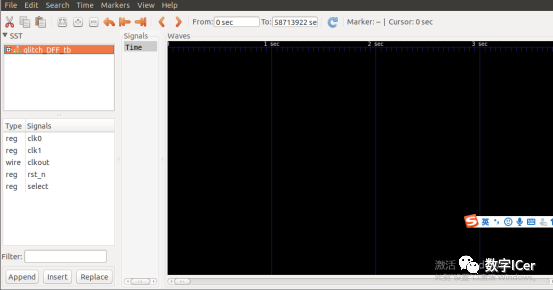

添加波形的时候卡死,可能是glitch.vcd文件太大;

解决:

gtkwave,icarus支持vcd,lxt,lxt2 dump.

vcd通用但vcd dump太大,gtkwave不能很好的查看波形,导致崩溃。

所以最好之前用lxt或将vcd转化为lxt格式。lxt格式是gtkwave的专用格式。

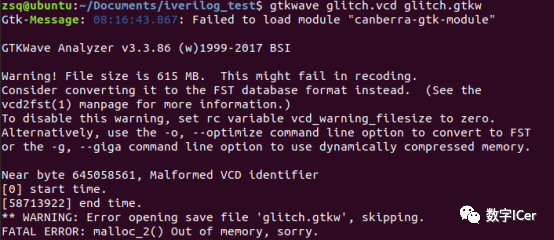

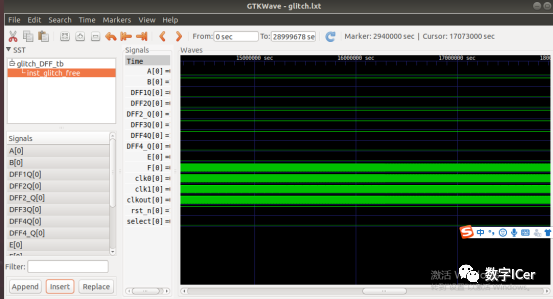

cpglitch.vcdglitch.lxt

添加波形

5.Verilog转换为VHDL

将glitch.v文件转换为VHDL文件glitch.vhd

iverilog-tvhdl-oglitch.vhdglitch.v

审核编辑:郭婷

-

仿真

+关注

关注

53文章

4407浏览量

137671 -

Verilog

+关注

关注

30文章

1370浏览量

114140

原文标题:开源verilog仿真工具 | iverilog+GTKWave

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

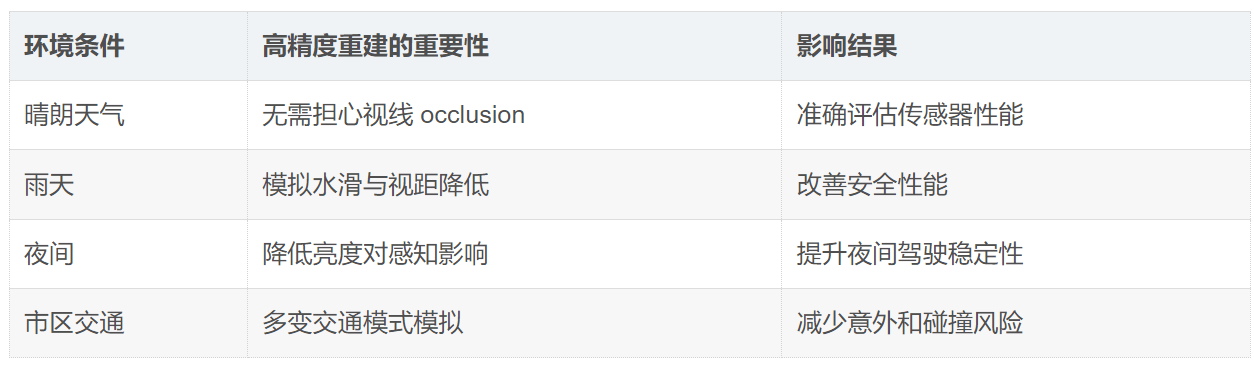

如何选择适合的智驾仿真工具进行场景生成和测试?

利用 NucleiStudio IDE 和 vivado 进行软硬件联合仿真

使用NucleiStudio生成tb仿真需要的.verilog文件

在Ubuntu 虚拟机中使用verilator对蜂鸟E203内核进行仿真

Vivado仿真e203_hbirdv2跑whetstone跑分(开源)

在Linux系统下编译C语言仿真蜂鸟E203(二)

vcs和vivado联合仿真

Linux使用coremark程序进行vcs仿真的注意事项

ESP32驱动SPIFFS进行文件操作

使用开源verilog仿真工具进行文件的编译和仿真

使用开源verilog仿真工具进行文件的编译和仿真

评论