为了精简电路

电器中会用到逻辑电平代替复杂的接线

他们都是如何设计的呢?

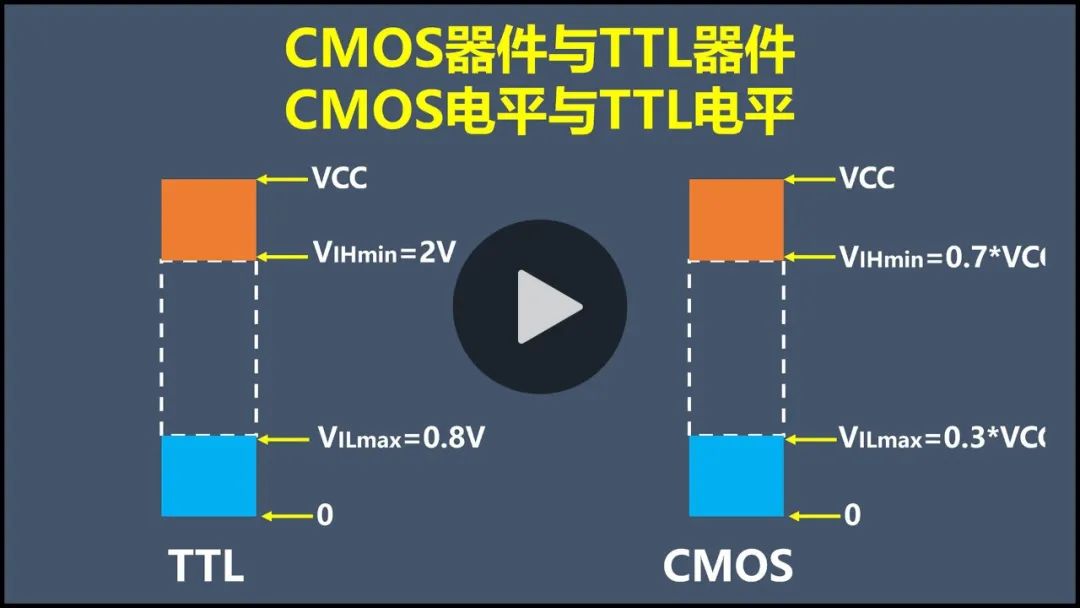

CMOS器件与TTL器件 CMOS电平与TTL电平

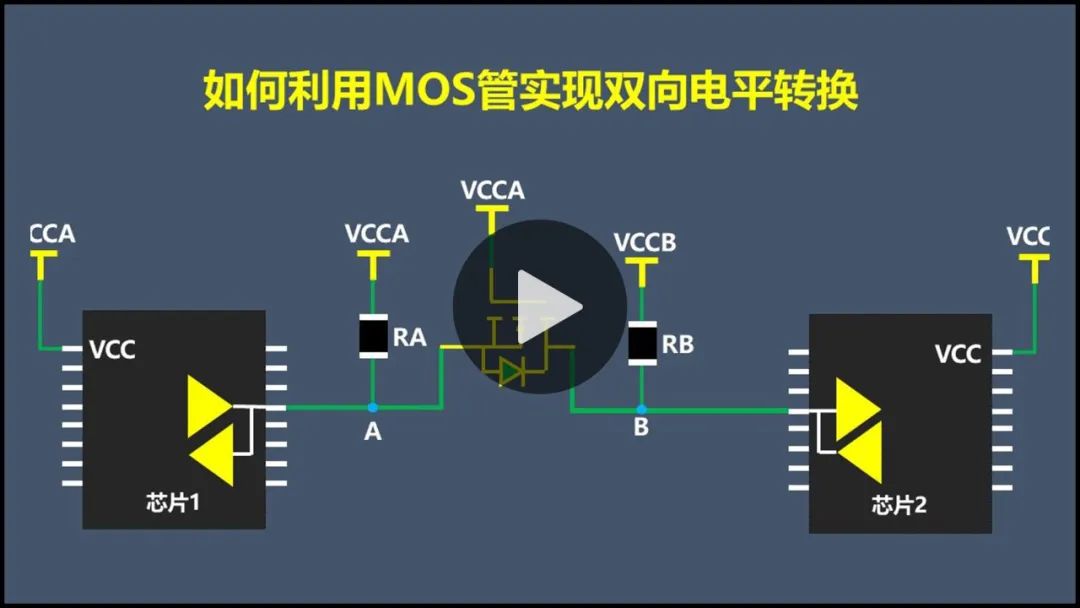

如何利用MOS管实现双向电平转换

什么是LVDS电平?

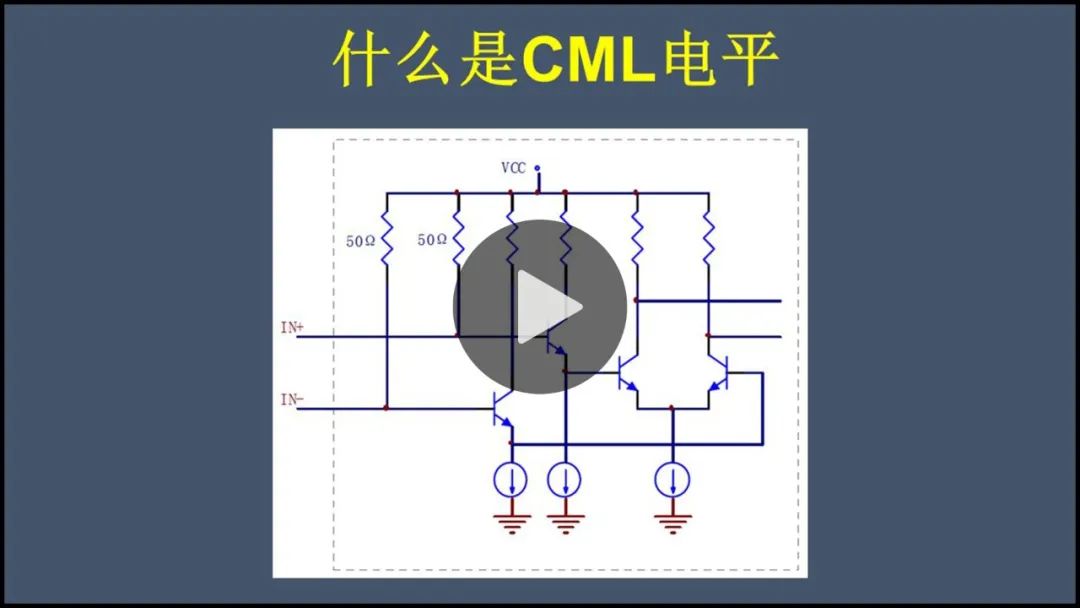

什么是CML电平?

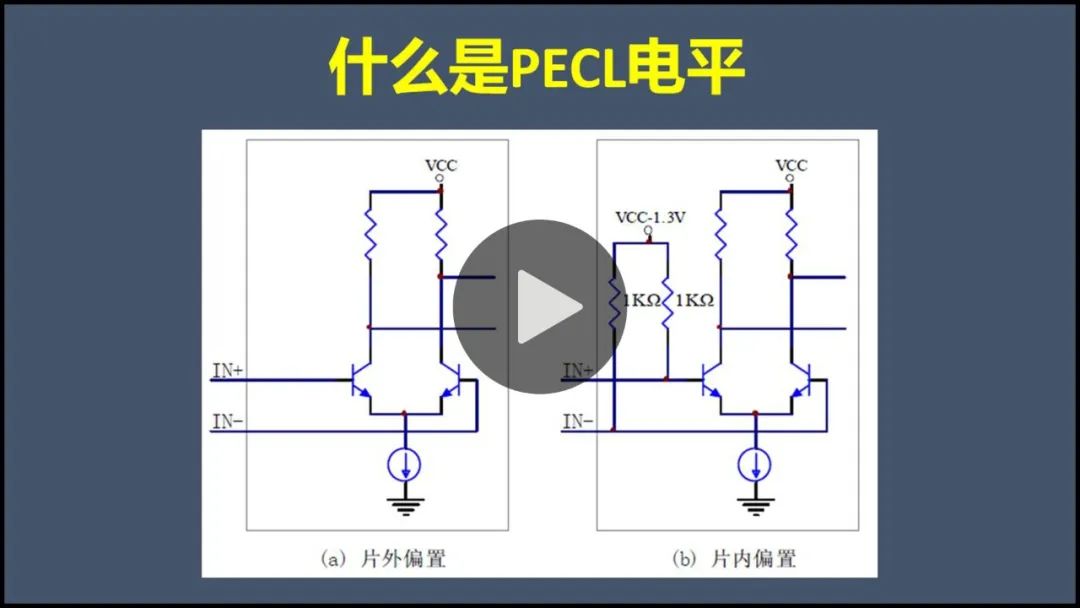

什么是PECL电平?

更多逻辑电平相关视频

可在硬声APP搜索“逻辑电平”观看

原文标题:【硬声推荐】逻辑电平视频合集

文章出处:【微信公众号:硬声】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

逻辑电平

+关注

关注

0文章

205浏览量

15157 -

硬声APP

+关注

关注

1文章

12浏览量

608

发布评论请先 登录

相关推荐

热点推荐

FDN5632N - F085 MOSFET:高性能N沟道逻辑电平器件解析

FDN5632N - F085 MOSFET:高性能N沟道逻辑电平器件解析 在电子设计领域,MOSFET作为关键的半导体器件,广泛应用于各类电路中。今天我们来深入了解一款高性能的N沟道逻辑电平

深入解析 FDS6690A 单 N 沟道逻辑电平 MOSFET

深入解析 FDS6690A 单 N 沟道逻辑电平 MOSFET 在电子设计领域,MOSFET 作为关键的电子元件,其性能直接影响着电路的运行效率和稳定性。今天,我们将深入探讨

详解 onsemi NDT3055L 逻辑电平 N 沟道增强型 MOSFET

详解 onsemi NDT3055L 逻辑电平 N 沟道增强型 MOSFET 在电子设计领域,功率场效应晶体管(MOSFET)是至关重要的元件,广泛应用于各类电路中。今天,我们就来深入探讨

深入解析 onsemi RFD16N05LSM N 沟道逻辑电平功率 MOSFET

深入解析 onsemi RFD16N05LSM N 沟道逻辑电平功率 MOSFET 在电子设计领域,功率 MOSFET 是至关重要的元件,广泛应用于各种电路中。今天我们来详细了解 onsemi 公司

MDD 逻辑IC的逻辑电平不兼容问题与解决方案

)不断被引入市场,它们具有各自的优势,但也带来了逻辑电平不兼容的问题,尤其是在多个不同类型的逻辑IC互联时,电平不匹配的问题显得尤为突出。作为FAE,帮助客户理解

【作品合集】视美泰M-K1HSE、3568开发板测评

视美泰M-K1HSE、3568开发板测评作品合集

产品介绍:

M-KIHSE开发板:

M-KIHSE开发板是一款基于进选时空K1(RISC-V SpacemiT X60)八核处理器的高性能开发平台

发表于 09-22 10:32

【作品合集】米尔RK3576开发板测评

米尔RK3576开发板测评作品合集

产品介绍:

RK3576 是瑞芯微一款面向AI市场推出的高性能处理器,它配备了四核Cortex-A72和四

核Cortex-A53 的 CPU,集成了6TOPS

发表于 09-11 10:19

如何调用mpp硬解+ffmpeg本地播放视频,RK3576

我往rk3576上部署了一个ubuntu系统,想测试rkmpp+ffmpeg或者rkmpp+gstreamer硬解,实现本地播放视频,有什么思路或者案例可以供我参考吗?

目前遇到了很多问题:

无法使用rkmpp解码,如果直接本地播放视频

发表于 08-23 10:05

开关磁阻电机合集

开关磁阻电机合集,需要自行下载

纯分享帖,需要者可点击附件免费获取完整资料~~~

【免责声明】本文系网络转载,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请第一时间告知,删除内容!

发表于 06-05 11:26

ADG3301 1.15 V至5.5 V低压、单通道双向逻辑电平转换器技术手册

ADG3301是一款单通道双向逻辑电平转换器,可用于多电压数字系统,如低压DSP/控制器与高压器件之间的数据传输等。该器件的内部结构允许执行双向逻辑电平转换,且无需借助额外的信号来设置

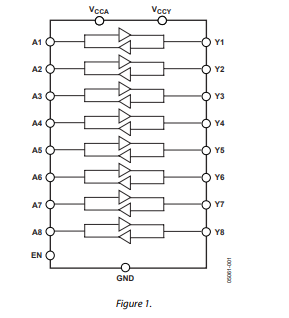

ADG3300 1.15 V至5.5 V低压、8通道双向逻辑电平转换器技术手册

ADG3300是一款双向逻辑电平转换器,内置8个双向通道,可用于多电压数字系统,如低压DSP/控制器与高压器件之间的数据传输等。该器件的内部结构允许执行双向逻辑电平转换,且无需借助额外

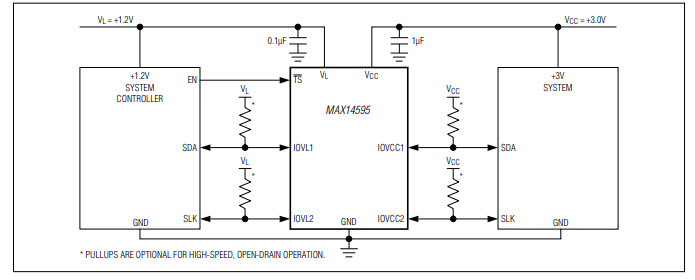

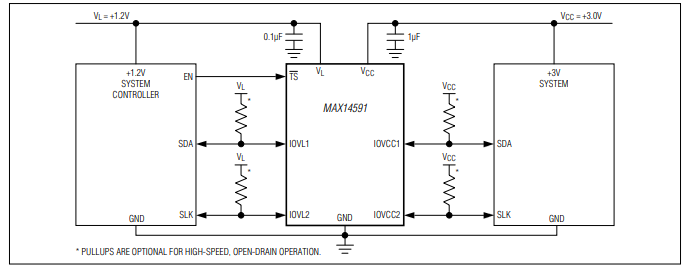

MAX14595高速、漏极开路逻辑电平转换器技术手册

MAX14595为双通道、双向逻辑电平转换器,设计用于手持设备和电池供电等低功耗应用。 外部电压V~CC~和V~L~设置器件两侧的逻辑电平。 将V~L~侧的

【硬声推荐】逻辑电平视频合集

【硬声推荐】逻辑电平视频合集

评论