多核处理器越来越多地被采用在关键系统领域,特别是在关键任务的军事环境中。它们为单核处理器的长期可用性问题以及促进军事系统创新所需的处理能力增加的问题提供了解决方案。由于多核处理器既不提供确定性环境,也不提供可预测的软件执行时间,因此需要一种新的验证方法(一种解决多核时序分析挑战的方法)来安全使用。

处理器的SWaP(尺寸,重量和功率)问题的持续进展导致多核供电的手机比阿波罗11号月球着陆器包含更多的功率。使用多核处理器带来的好处导致该技术在主流技术行业中得到广泛采用,单核处理器现在只占市场的一小部分。由于这种转变,芯片制造商正在远离生产这些传统处理器,它们的长期可用性受到严重质疑。

随着单核处理器的供应不断减少,现代嵌入式系统越来越受欢迎,采用多核处理器是不可避免的。然而,在关键任务军事领域安全使用这些处理器具有挑战性,因为它们既不提供确定性环境,也不提供可预测的软件执行时间。

军用航空电子认证的黄金标准

DO-178C 是 FAA [联邦航空管理局] 和 EASA [欧盟航空安全局] 等著名认证机构批准所有商业软件航空航天系统的主要文件。多年来,它也已成为在军用航空电子系统中使用软件的事实黄金标准。

美国联邦航空局用题为“多核处理器”的立场文件CAST-32A补充了DO-178C指南,以解决航空中越来越多地使用多核处理器的问题。

美国陆军指定的主要适航机构AMRDEC航空工程局(AED)发布了一份名为“多核处理器(MCP)适航要求”的指导文件草案,其中DO-178C和CAST-32A目标被确定为可用于满足MCP [多核处理器]适航要求的指南。

时序分析是 CAST-32A 指南中确定的核心目标之一,并具体由称为 MCP_Software_1 的目标解决,该目标需要证据证明所有托管软件组件正常运行,并且在多核环境中运行时有足够的时间完成其执行。这是一个非常具有挑战性的目标,并且已被证明是旨在认证多核项目的军事和航空航天公司的严重障碍。

分析多核时序行为

由于多种原因,旨在验证单核系统时序行为的验证解决方案不适用于多核时序分析,主要是因为这些解决方案无法考虑资源争用引起的干扰的影响。为了验证多核系统的时序行为,需要专门解决多核时序分析挑战的新方法。

考虑资源争用和干扰

多核系统任务中任务的计时行为不仅受其上运行的软件及其输入的影响,还受与其他内核上运行的任务共享的资源(如总线、缓存和 GPU)争用的影响。为了设计实验来分析多核系统的时序行为,必须识别并考虑干扰源。

图 1 显示了多核架构的简化示例,其中总线在多个内核之间共享。由核心 N 访问此总线而导致的流量可能会影响在核心 0 上运行的应用程序的计时行为,该应用程序需要访问此总线。

图1|多核系统中的干扰信道示例。

必须测试假设

为了分析多核系统的时序行为,必然需要对所研究系统的行为进行一些假设,包括存在的干扰信道的影响。由于多核系统的复杂性,对系统做出的看似合乎逻辑的假设以后可能会被证明是不正确的,可能需要一个迭代过程来做出假设,测试它们,并使用分析结果来完善下一轮测试的假设。

这最好用一个实际示例来解释:正在研究的是运行在 Xilinx Zynq Ultrascale+ ZCU102 目标板上的内存密集型应用对不同干扰水平的敏感性。运行应用程序的应用程序处理单元有四个内核。合理的假设是,由于对系统的先验了解,二级缓存是此应用的主要干扰通道。为了验证这一假设,在应用程序运行时执行了一项测试,同时从 0 到 3 个竞争者内核上运行的任务对 L2 缓存进行持续访问。

图2|CPU 周期和二级缓存未命中。

如果假设有效,则应用程序执行的二级缓存未命中数和 CPU 周期数将随着每个额外的竞争者内核而增加。该图显示,这一假设一直持续到引入第三个竞争者核心。这增加了 CPU 周期数,但二级缓存未命中数与只有两个竞争者内核处于活动状态时大致相同。

多核系统中干扰效应的复杂性意味着设计人员应该期望需要迭代周期来形成假设,测试它们,并使用分析结果形成新的假设。虽然没有办法自动化这个过程,但工程师可以在如何形成关于多核处理器的合理假设以及如何通过处理多个项目和积累经验来在调查工作中重新评估这些假设方面发展专业知识。有效的重新评估和测试将导致全面了解多核处理器的行为方式以及哪些因素会影响其计时行为。

在真实硬件上进行测试

多核CPU很复杂,其内部通常是隐藏的,因此纯分析模型在理解其时序行为方面的用途有限。虽然纯分析(静态分析)模型可以为单核系统提供可用的时序估计,但对于多核系统则不是这种情况。即使使用这些方法,它们也会根据多核配置的病理最坏情况行为产生高度悲观的结果,并且这些结果将没有实际用途。

要从多核系统生成可用的时序指标,必须测量系统本身的时序行为。Rapita Systems的工程师使用巴塞罗那超级计算中心开发的一系列微基准来强调特定的共享资源,并在发生这种争用时观察应用程序的计时行为。通过使用该技术对特定共享资源应用可配置的争用程度,可以制定实验,以帮助根据可行的计时环境分析计时指标。这些实验可以产生满足CAST-32A定时目标所需的关键证据,例如最坏情况执行时间(WCET)。

多核时序分析不能完全自动化

多核处理器的复杂性意味着构建全自动时序分析解决方案是不现实的。虽然工具支持可以自动化大多数数据收集和分析过程,但需要工程智慧和专业知识来了解系统和指导工具使用以产生必要的证据。工程师在了解多核系统、研究干扰信道和使用支持工具方面的经验越多,分析过程的效率就越高。

未来的关键任务

军事领域使用的关键任务嵌入式系统越来越多地使用多核处理器。这些系统的认证考虑因素不是事后才考虑的,而是在开发过程的早期考虑的。值得庆幸的是,DO-178C 提供了一组强大的目标,以确保安全可靠地使用这些处理器。多核系统的时序分析具有挑战性,但久经考验的解决方案可以在商业环境中执行。

审核编辑:郭婷

-

处理器

+关注

关注

68文章

20148浏览量

246942 -

MCP

+关注

关注

0文章

286浏览量

14898

发布评论请先 登录

云拼接处理器的性能如何?

Andes晶心科技推出AndesCore 46系列处理器家族

T113-i芯片技术解析:高性能嵌入式处理器的创新设计

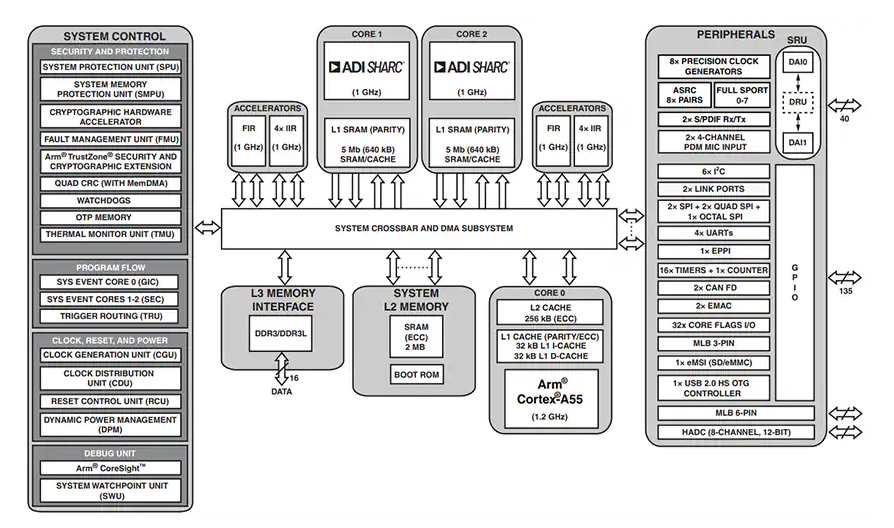

Analog Devices Inc. ADSP-SC598双SHARC+®数字信号处理器数据手册

任务关键型环境中的多核处理器

任务关键型环境中的多核处理器

评论