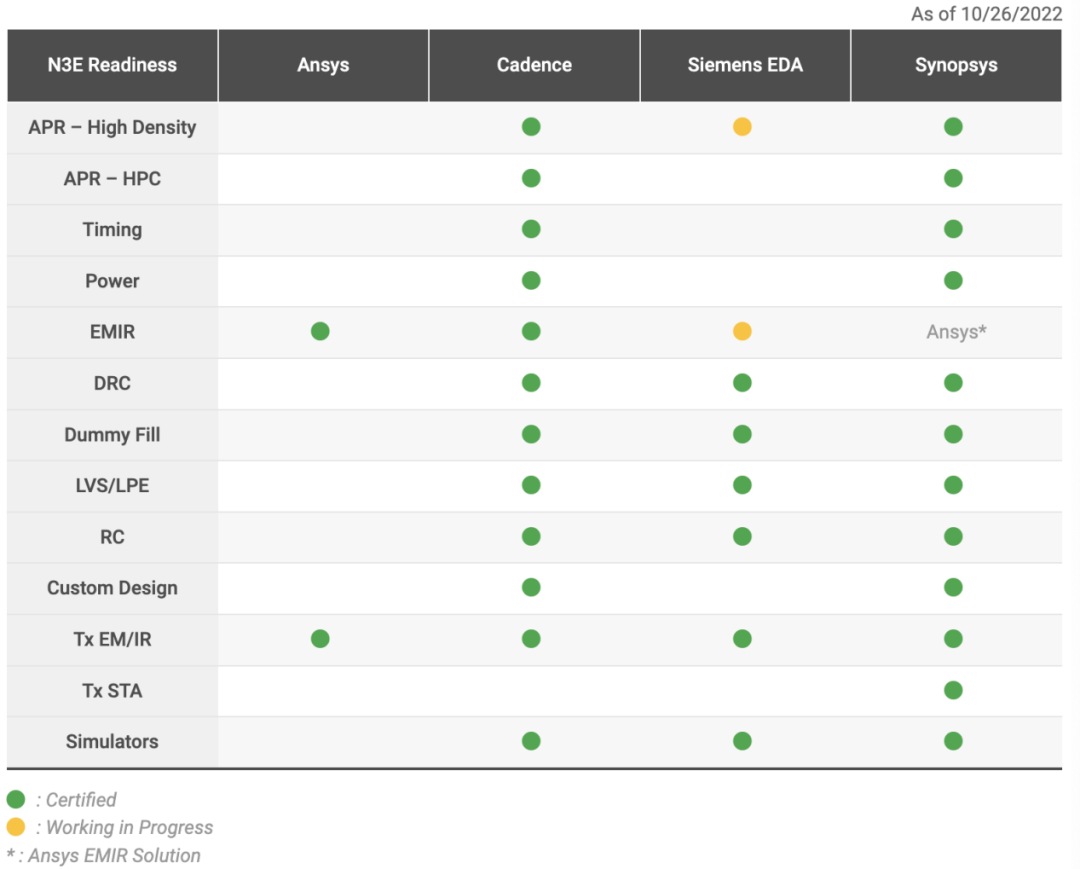

EDA大厂陆续获得认证

不只是最新工艺

写在最后

董明珠:格力为特斯拉供应底盘装备,白电企业对“造车”达成共识? 俄罗斯生产首颗纯国产通信卫星!俄卫星实力有多强? 欧盟统一充电接口!苹果:确定改用USB-C! Marvell大幅裁撤中国研发团队,但另一市场正加大在华投资 警惕!德州仪器:芯片需求疲软,正从消费电子蔓延至工业领域!

原文标题:台积电3nm推出在即,EDA厂商陆续取得认证

文章出处:【微信公众号:电子发烧友网】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

电子发烧友网

+关注

关注

1013文章

544浏览量

167488

原文标题:台积电3nm推出在即,EDA厂商陆续取得认证

文章出处:【微信号:elecfans,微信公众号:电子发烧友网】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

台积电拟投资170亿,在日本建设3nm芯片工厂

据报道,全球最大的半导体代工制造商台积电(TSMC)已最终确定在日本熊本县量产3nm线宽的尖端半导体芯片的计划。预计该项目投资额将达到170亿美元。日本政府正致力于提升国内半导体制造能

1.4nm制程工艺!台积电公布量产时间表

电子发烧友网综合报道 近日,全球半导体代工龙头台积电在先进制程领域持续展现强劲发展势头。据行业信源确认,台积

台积电2纳米制程试产成功,AI、5G、汽车芯片,谁将率先受益?

与现行的3nm工艺相比,台积电在2nm制程上首次采用了GAA(Gate-All-Around,环绕栅极)晶体管架构。这种全新的结构能够让晶体

台积电Q3净利润4523亿元新台币 英伟达或取代苹果成台积电最大客户

39.1%,净利润创下纪录新高,台积电在上年同期净利润为3252.58亿新台币。 每股盈余为新台币17.44元,同比增加39.0%。 目前台积电

台积电2纳米制程试产成功,AI、5G、汽车芯片

又近了一大步。 这一历史性节点不仅意味着制程技术的再度跨越,也预示着未来AI、通信与汽车等核心领域即将迎来一场深刻的“芯革命”。 1、技术再突破 与现行的3nm工艺相比,台积电

台积电预计对3nm涨价!软银豪掷54亿美元收购ABB机器人部门/科技新闻点评

在十一黄金周和国庆假期后第一天工作日,科技圈接连发生三件大事:1、台积电预计将对3nm实施涨价策略;2、日本巨头软银宣布54亿美元收购ABB机器人部门;

突发!台积电南京厂的芯片设备出口管制豁免被美国正式撤销

美国已撤销台积电(TSMC)向其位于中国大陆的主要芯片制造基地自由运送关键设备的授权,这可能会削弱其老一代晶圆代工厂的生产能力。 美国官员最近通知台

今日看点:传台积电先进2nm芯片生产停用中国大陆设备;保时捷裁员约200人

传台积电先进2nm芯片生产停用中国大陆设备 业内媒体报道,根据多位知情人士透露,台

发表于 08-26 10:00

•2760次阅读

台积电2nm工艺突然泄密

据媒体报道,台积电爆出工程师涉嫌盗取2纳米制程技术机密,台湾检方经调查后,向法院申请羁押禁见3名涉案人员获准。 据悉,由于台“科学及技术委员

重新定义基础款,eSUN Basic 系列产品已陆续上线!

eSUN易生PLA基础(PLA-Basic)、PETG基础(PETG-Basic)等基础(Basic)系列产品已陆续上线,它们的主要特点在于出色的性价比,在保持价格优势的同时,也为用户提供较好的打印使用体验。

长电科技先进封装技术助力智能眼镜功能升级

2025年以来,众多厂商陆续推出智能眼镜产品,“百镜大战”一触即发,市场或将迎来爆发元年。根据国际数据公司(IDC)的预测,2025年全球智能眼镜市场出货量将达到1280万台,同比增长26%。轻量化设计、AI大模型融合与现实多场

台积电先进制程涨价,最高或达30%!

%,最高可能提高30%。 今年1月初台积电也传出过涨价消息,将针对3nm、5nm等先进制程技术进行价格调整,涨幅预计在

发表于 05-22 01:09

•1335次阅读

西门子与台积电合作推动半导体设计与集成创新 包括台积电N3P N3C A14技术

西门子和台积电在现有 N3P 设计解决方案的基础上,进一步推进针对台积电 N

发表于 05-07 11:37

•1618次阅读

台积电3nm推出在即,EDA厂商陆续取得认证

台积电3nm推出在即,EDA厂商陆续取得认证

评论