我们认为半导体世界中的许多事情是理所当然的,但如果几十年前做出的某些决定不再可行或最优了,我们应该怎么办?我们看到了一个使用 finFET 的小例子,平面晶体管将不再扩展。今天,我们面临着几个更大的破坏,这些破坏将产生更大的连锁反应。

技术通常以线性方式发展。每一步都提供了对以前存在的增量改进,或者克服了一些新的挑战。这些挑战来自新节点、新物理效果或限制等。虽然这非常有效,而且许多单独的步骤都很出色,但它建立在纸牌屋的基础上,如果基础上的某些东西从根本上来说变化,整个设计、实现和验证的连锁反应可能非常显著。

01单个连续内存

这些更改之一已经进行了一段时间。1945 年首次描述的冯诺依曼处理器架构,具有单一的连续内存空间,是绝对的突破。它提供了一个图灵完备的解决方案,可以解决任何有限问题。这成为几乎所有计算机的实际架构。

内存很快成为了大小和性能方面的限制。为了克服这个问题,引入了缓存以使廉价的大容量内存看起来像更昂贵、更快的内存。随着时间的推移,这些缓存变得多级,跨多个主机连贯,并在越来越大的地址空间上工作。

但这不再是许多现代计算功能的要求。在基于对象的软件功能和特定领域计算的时代,对内存组织的需求可能是有害的。它基于这样一个前提,即程序可以随机访问它想要的任何东西——安全专家希望这不是真的。

必须充分考虑缓存和一致性的全部成本。“在芯片中实现一致性是复杂且昂贵的,” Imperas Software的创始人兼首席执行官 Simon Davidmann 说。“当您进行多级缓存时,内存层次结构变得越来越复杂,并且越来越充满错误,并且消耗越来越多的功率。”

当任务很好理解时,可以避免这种开销。“在数据流引擎中,一致性不那么重要,因为您将在边缘移动的数据直接从一个加速器传送到另一个加速器,” Arteris IP的研究员兼系统架构师 Michael Frank 说。“如果你对数据集进行分区,一致性就会成为障碍,因为它会花费你额外的周期。您必须使用查找表。您必须提供更新信息。”

面向对象系统的采用,以及限制类型转换的强类型语言和对程序员的一些限制,可以使执行流程可预测并避免对单个连续内存空间的需求。诸如在图形和机器学习中发现的任务在有限的内存块上运行,并且不会从复杂的内存管理或对内存的硬件控制中受益。

特定领域的计算正在导致人们重新考虑这方面的许多方面。“例如,DSP 倾向于提供分布式内存池,通常直接在软件中管理,” Arm研发团队的高级首席研究工程师 Matt Horsnell 说。“与传统的共享内存系统相比,这可能更适合专门应用程序的带宽要求和访问模式。这些处理器通常通过提供对特定访问模式(例如,N 缓冲、FIFO、行缓冲区、压缩等)的直接支持来提供某种形式的内存专业化。”

02新的内存类型

改变内存架构有很大的影响。“挑战在于,在过去,人们有一个很好的抽象模型来思考计算系统,” Rambus的研究员和杰出发明家 Steven Woo 说。“他们从来没有真正考虑过存储。它最初是免费出现的,而编程模型只是让你在引用内存时,它就发生了。你永远不必明确说明你在做什么。随着摩尔定律的放缓和功率缩放的停止,人们开始意识到有很多新的存储可以进入方程式。但要让它们真正有用,你必须摆脱我们过去拥有的非常抽象的观点。”

第二个相关的变化是通过新的内存技术实现的。长期以来,SRAM 和 DRAM 都针对速度、密度和性能进行了优化。但是 DRAM 的扩展已经停滞不前,而且 SRAM 受到最新节点的可变性的影响,因此难以保持密度。基于不同物理特性的新内存类型最终可能会更好,但这可能不是主要好处。

例如,如果采用ReRAM,存储单元本质上就会变成模拟的,这就开辟了许多可能性。Mythic 负责产品和业务开发的高级副总裁 Tim Vehling 说:“模拟的一个基本理念是,您实际上可以在存储单元本身中进行计算。” “你实际上消除了整个内存移动问题,因此功率大幅下降。当模拟发挥作用时,您可以进行高效的计算和很少的数据移动。借助模拟内存计算技术,它的能效实际上比数字等效技术高出几个数量级。”

这与机器学习所需的乘法/累加函数完全一致。“执行这些 MAC 操作所消耗的能量是巨大的,”西门子 EDA产品经理 Sumit Vishwakarma 说。“神经网络有权重,这些权重存在于内存中。他们必须不断地访问内存,这是一项非常耗能的任务。计算能力是传输数据所需能力的十分之一。为了解决这个问题,公司和大学正在研究模拟计算,它将权重存储在内存中。现在我只需要输入一些输入并得到一个输出,这基本上是这些权重与我的输入的乘积。”

当模拟和数字解耦时,模拟电路不再受阻。Semtech 信号完整性解决方案集团营销和应用副总裁 Tim Vang 说:“我们可以设计模拟电路,在某些情况下提供与数字等效甚至更好的功能,而且我们可以在较旧的节点上做到这一点。” “成本可以更低,因为我们不需要所有的数字功能,因此芯片尺寸可以更小。我们可以降低功耗,因为我们没有那么多功能。”

当内存发生变化时,软件堆栈中的所有内容都会受到影响。Synopsys产品营销总监 Prasad Saggurti 说:“通常会发生一种算法,我们看到了一种优化它的方法,优化内存,以便更好地实现算法。” “另一方面,我们拥有这些不同类型的内存。你能改变你的算法来利用这些新的记忆吗?过去,使用 TCAM 主要是一种网络域结构来查找 IP 地址。最近,ML 训练引擎开始使用 TCAM。这需要根据可用存储器的类型来改变软件或固件。”

03CMOS 的终结

但到目前为止,最大的潜在变化是 CMOS 的终结。随着器件变得更小,掺杂的控制变得具有挑战性,这会导致器件阈值电压的显着变化。掺杂定义了器件的极性,例如器件是 PMOS 还是 NMOS,正是这些器件的配对创建了 CMOS 结构,这是创建的所有数字功能的基础。随着行业向全栅 finFET 结构迁移,出现了一种新的可能性。

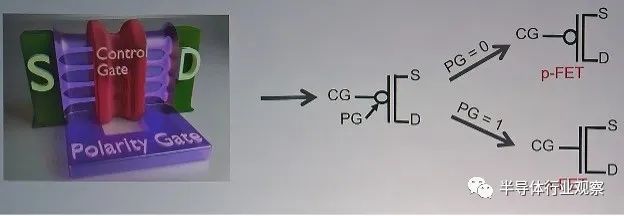

“使用水平堆叠的纳米线,您实际上可以构建具有两个栅极的晶体管,”洛桑联邦理工学院电气工程和计算机科学教授 Giovanni De Micheli 在 DAC 2022 主题演讲中说。“你使用第二个栅极来极化晶体管并使晶体管成为 P 或 N 晶体管(见图 1)。你会得到一个更强大的晶体管,因为它创建了一个比较器而不是一个开关。现在,有了这些类型的设备,您就可以拥有全新的拓扑结构。”

图 1. GAA 极性门的 3-D 概念图。资料来源:Michele De Marchi 论文,EPFL,2015

理论上,这可以通过将极性门一分为二来进一步实现。除了是 p 型或 n 型之外,这将增加每个晶体管也成为高或低阈值电压器件的能力。因此,每个晶体管在运行期间都可以具有不同的功率/性能特性。

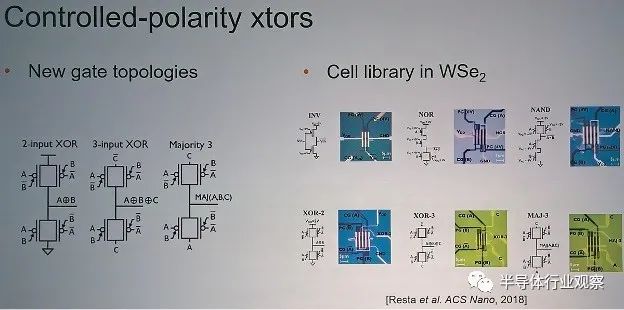

让我们回到逻辑抽象。“几十年来,我们一直在用 NAND 和 NOR 设计数字电路,”De Micheli 说。“为什么?因为我们一开始就被洗脑了,因为在CMOS中那是最方便的实现。但是,如果您从多数逻辑的角度思考(见图 2),您就会意识到这是进行加法和乘法运算的关键运算符。今天,我们为机器学习实现的所有电路,其中的主要部分就是进行加法或乘法运算。这就是为什么多数是极其重要的。此外,多数逻辑是超导体、光学技术、内存中的非易失性逻辑等许多技术的自然模型。”

图 2. 基于极性门器件的新逻辑元件。资料来源:De Micheli/EPFL

De Micheli 的研究表明,采用多数逻辑设计的电路可以使用今天略微修改的 EDA 工具将延迟减少 15% 到 20%。

但这些类型的变化确实需要对综合和其他步骤进行重大重新思考。Synopsys 的技术策略师 Rob Aitken 说:“如果这被证明是一个很有前途的载体,你真的需要彻底重新考虑合成引擎。” “许多新设备不会有效地采用 NAND/NOR 电路并从中构建东西,而是将本机调整为 XOR、多数门或其他一些逻辑功能。会发生什么?综合关注您正在构建的基本事物,虽然它过于简单化,但逻辑综合需要一个 PLA,然后将其折叠成一个多层次的对象。以不同的逻辑风格重新思考很重要。”

改变基本的晶体管功能对流程的许多方面都有重大影响。例如,设备现在有四个或五个终端,而不是三个,这会对布局和布线产生什么影响?它将如何影响扇入扇出和拥塞?

04结论

改变是困难的。一项有前途的技术必须克服现有技术数十年的优化,这会带来巨大的惯性挑战。它还可能需要同时更改解决方案的许多部分,例如硬件和软件,或整个实现链中的工具。但随着该行业接近半导体的一些基本物理极限,它需要变得更加灵活并愿意改变。

审核编辑:汤梓红

-

芯片

+关注

关注

463文章

54463浏览量

469577 -

半导体

+关注

关注

339文章

31279浏览量

266701 -

内存

+关注

关注

9文章

3238浏览量

76524

原文标题:芯片架构师需要思考的一些问题

文章出处:【微信号:算力基建,微信公众号:算力基建】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

高通Oryon架构之父宣布离职:曾一手定义移动芯片黄金时代

在并联使用MOS存在一些问题,要怎样做才能避免这些问题?

关于六类网线一些问题的解答

对浮点指令扩展中一些问题的解决与分享

蜂鸟E203的浮点指令集F的一些实现细节

Vivado浮点数IP核的一些设置注意点

在TR组件优化与存算一体架构中构建技术话语权

求助,关于TC387使能以及配置SOTA 中一些问题求解

射频工程师需要知道的一些常见转接头

Tenstorrent 首席架构师:未来 RISC-V 会是计算机的主流

关于芯片设计的一些基本知识

芯片架构师需要思考的一些问题

芯片架构师需要思考的一些问题

评论