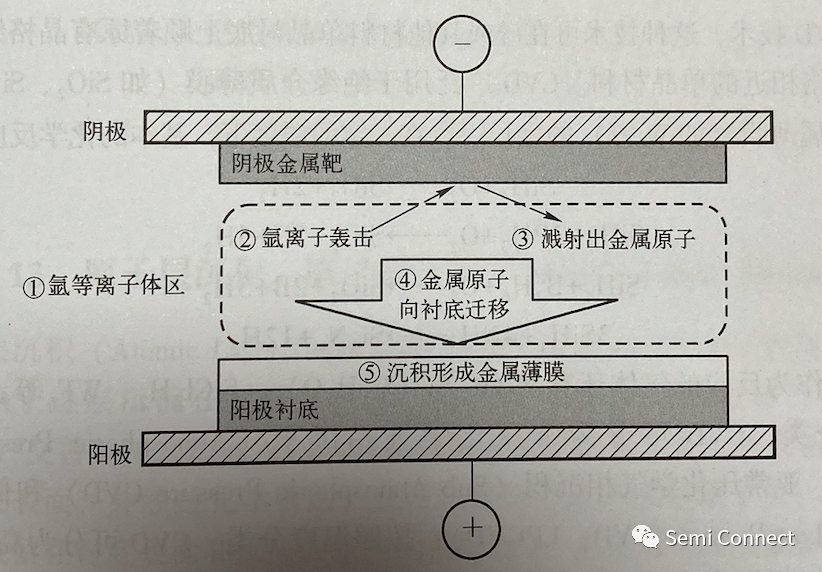

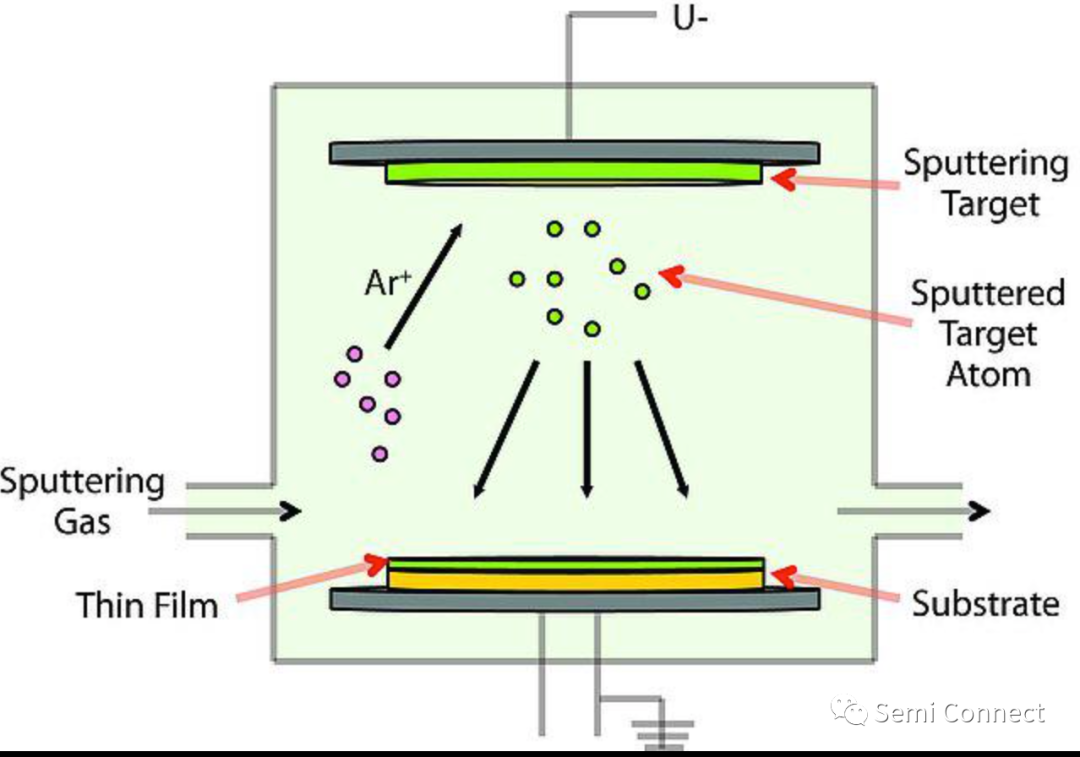

物理气相沉积(Physical Vapor Deposition, PVD)工艺是指采用物理方法,如真空蒸发、溅射 (Sputtering)镀膜、离子体镀膜和分子束外延等,在圆片表面形成薄膜。在超大规模集成电路产业中,使用最广泛的 PVD 技术是溅射镀膜,主要应用于集成电路的电极和金属互连。溅射镀膜是在高度真空条件下,稀有气体(如氩气 Ar)在外加电场作用下电离成离子(如 Ar),并在高电压环境下轰击材料靶源,撞击出靶材的原子或分子,经过无碰撞飞行过程抵达圆片表面形成薄膜。氩气(Ar)的化学性质稳定,其离子不会与靶材和薄膜产生化学反应。随着集成电路芯片进入0. 13um 铜互连时代,铜的阻挡材料层采用了氮化钛(TiN)或氮化钽(TaN)薄膜,产业技术的需求推动了对化学反应溅射技术的研发,即在溅射腔里,除了氩气,还有反应气体N2,这样从靶材Ti 或 Ta 轰击出来的Ti 或Ta 与氮气反应,生成所需的 TiN 或TaN 薄。

常用的溅射方式有 3种,即直流溅射、射频溅射和磁控溅射。由于集成电路的集成度不断提高,多层金属布线的层数越来越多,PVD工艺的应用也更为广泛。PVD 材料包括 AI-Si、AI-Cu、 Al-Si-Cu、Ti、Ta、Co、TiN、TaN、Ni、WSi2等。 PVD和溅射工艺通常是在一个高度密闭的反应腔室里完成的,其真空度达到 1X10(-7)~9×10(-9)Torr ,可保证反应过程中气体的纯度;同时,还需要外接一个高电压,使稀有气体离子化以产生足够高的电压表击靼材。评价物理气相沉积和溅射工艺的主要参数有尘埃数量,以及形成薄膜的电阻值、均匀性、反射率、厚度和应力等。

审核编辑 :李倩

-

射频

+关注

关注

106文章

6123浏览量

173857 -

PVD

+关注

关注

4文章

51浏览量

17674

原文标题:物理气相沉积及溅射工艺(PVD and Sputtering)

文章出处:【微信号:Semi Connect,微信公众号:Semi Connect】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

天弘激光诱导化学图形化沉积设备:重塑高端电子制造新范式

厚声贴片电阻的厚膜工艺与薄膜工艺有何区别?

集成电路制造中薄膜生长工艺的发展历程和分类

台阶仪应用丨电子束蒸镀与磁控溅射铝膜的厚度与均匀性对比研究

应用材料AMAT/APPLIED MATERIALS Producer® XP Precision® CVD系列二手薄膜沉积CVD设备拆机/整机|现场验机评测

PTC热敏电阻直流磁控溅射工艺解析

基于光学成像的沉积薄膜均匀性评价方法及其工艺控制应用

金属淀积工艺的核心类型与技术原理

基于失效案例的航空发动机涂层技术优化研究:机理、措施与质量控制要点

半导体“化学气相沉积(CVD)碳化硅(Sic)”工艺技术详解;

物理气相沉积及溅射工艺(PVD and Sputtering)

物理气相沉积及溅射工艺(PVD and Sputtering)

评论